針對環形振蕩器的功耗大、噪聲大、線性度差等問題,基于TSMC 55 nm工藝,提出了一種新型交叉前饋結構環形振蕩器電路。深入分析了器件自身熱噪聲、閃爍噪聲對環形振蕩器輸出相噪貢獻百分比,利用電容濾波技術來降低振蕩器輸出相噪,采用源極負反饋電路得到線性電流來改善調頻線性度,并提供了寬調諧范圍。Spectre RF仿真結果表明,設計的環形振蕩器頻率覆蓋范圍為0.2 GHz~3.8 GHz,產生8相位,相位噪聲為-91.34 dBc/Hz@1 MHz,在1.2 V電源電壓下消耗電流為4.6 mA ,線性度良好。

0引言

壓控振蕩器(VCO)是一種由電壓控制輸出頻率的振蕩器,是無線通信系統中一個重要的模塊,也是鎖相環電路(PLL)的核心,它的相位噪聲、靈敏度等參數直接影響PLL的最終性能。環形振蕩器比電感電容諧振壓控振蕩器(LC VCO)有很多顯著的優勢:不需電感元件,節省芯片面積,節省成本,調諧范圍寬,并且很容易實現多相位。不過,環形振蕩器的相位噪聲性能通常要稍差一些。綜合考慮其功耗低、面積小和集成高等優點,環形振蕩器被廣泛應用在通信領域。目前,低功耗、低噪聲、寬調諧的新型環形振蕩器結構吸引了眾多學者投入研究,例如文獻[1]中設計了一種頻率范圍為2.05 GHz~3.35 GHz的環形振蕩器,其相位噪聲為-89.6 dBc/Hz@1 MHz,核心電路的功耗為18.36 mW,不過,其功耗較大,不能滿足在無線通訊系統中的低功耗要求。針對振蕩器存在的功耗大、噪聲大、線性度差等問題,提出了一種新型環形振蕩器結構,該環形振蕩器的頻率范圍為0.2 GHz~3.8 GHz,產生8相位,相位噪聲為-91.34 dBc/Hz@1 MHz。

1環形振蕩器

1.1 環形振蕩器

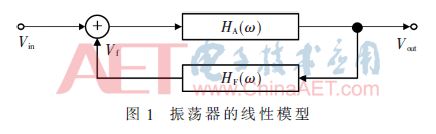

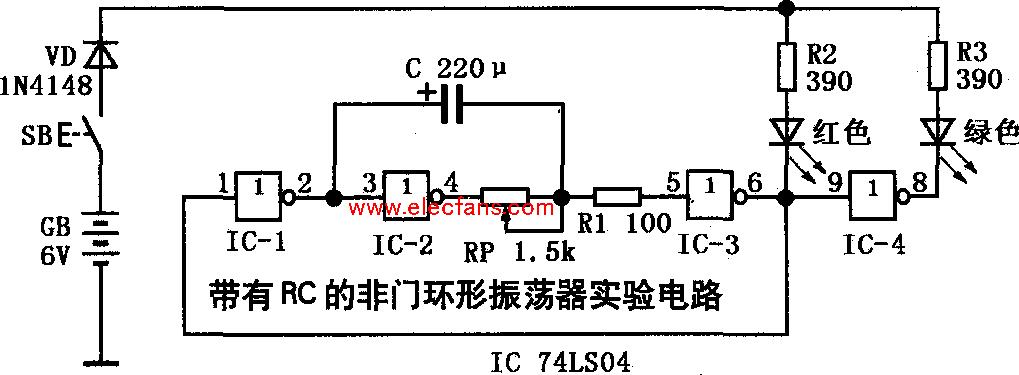

環形振蕩器的核心結構是在一個振蕩頻率處呈正反饋的環路,如圖1所示。

圖中,HA(ω)是基本放大器的傳輸函數,HF(ω)為反饋網絡的傳輸函數。反饋系統的閉環增益為式(1):

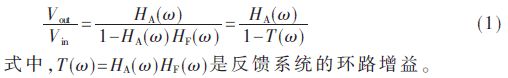

環形振蕩器的工作原理是環路傳輸函數僅在一個頻率點上滿足Barkhausen判據,即在某一頻率ω下滿足式(2)就可以產生振蕩。

其中,ω0表示輸入電壓為0的輸出頻率,KVCO為VCO的增益,單位為rad/(s·V),Vcon為控制電壓。

1.2 電路原理分析與設計

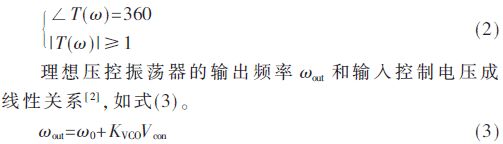

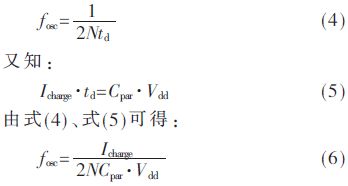

環形振蕩器的相位噪聲主要來自于散粒噪聲、熱噪聲和環境噪聲。熱噪聲是溫度、帶寬和電阻作用的結果;散粒噪聲是直流偏置電流引起的;而環境噪聲主要來自VCO外部電源的噪聲和襯底的噪聲。延遲單元可以采用單端結構和差分結構,以差分結構為基本延遲單元構成的差分環形振蕩器具有很好的對稱性,在克服環境噪聲方面具有很大的優勢,但是由于電路復雜,不僅增大了芯片的面積,而且帶來較多的熱噪聲,因此選用結構簡單、器件少的單端結構,可以有效地減少由器件本身帶來的熱噪聲。一個N級的環形振蕩器,每級的延時為td,則其頻率為:

其中,Icharge為充電電流,Cpar為延時單元輸出節點的總寄生電容,Vdd為供電電壓。

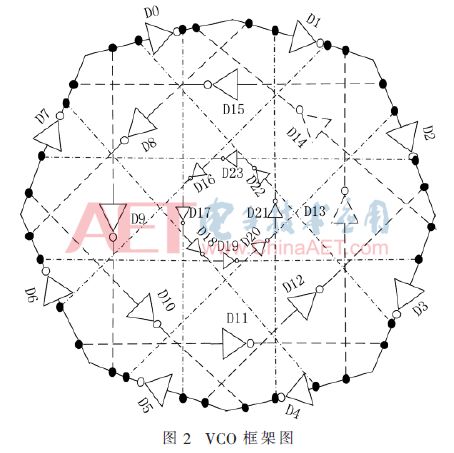

考慮到芯片面積,設計的環形壓控振蕩主要由24個反相器組成,如圖2所示,其中D0~D8依次首尾相連構成主環形結構。輸入端用 Vcon表示,VCO的振蕩頻率隨著輸入端電壓的變化而變化。

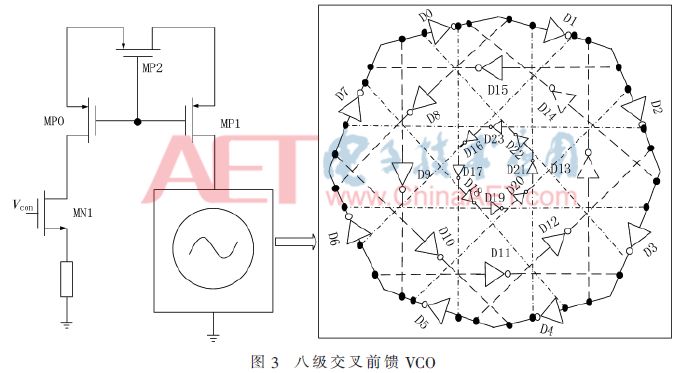

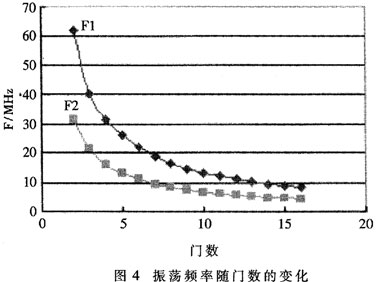

由圖3可知,該VCO主要包含三種環路,第一種是由D0~D8八個延遲單元組成的最慢主環路,第二種是包含兩個四級反向延遲單元組成的閉環環路,分別為D9—D11—D13—D15、D8—D10—D12—D14,另外還有一種包含四個閉環環路,分別為D16—D20,D17—D21,D18—D22,D23—D19分別組成的環路,主環路與各個子環路之間保持一個完美的對稱關系。

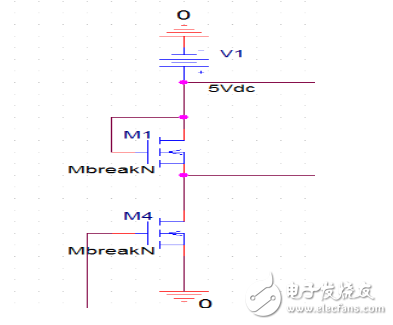

通過改變MN1的電流來改變負阻大小,那么MP0、MP1漏極等效電阻也隨之改變,進而調節振蕩頻率,由于是低電源供電,MP0、MP1采用電流鏡結構。MP0、MP1漏極等效阻值的變化會導致不同頻率信號的輸出擺幅不同,會影響VCO的噪聲性能,為滿足通信系統的需要,需要調整電流鏡的寬長比進而優化壓控振蕩器相位噪聲。

根據環形振蕩器的振蕩原理,這個以八級反相延遲單元為主環形鏈的VCO構成的壓控振蕩器可以實現正交相位的頻率信號輸出,可以有效抑制環境噪聲,在時鐘數據恢復電路中有著重要的應用[5]。

1.3 緩沖器設計

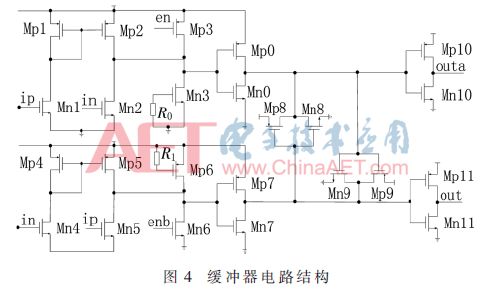

為了使環形振蕩器有良好的輸出匹配,在電路中引入如圖4所示的緩沖級,它主要由差分對、單端反相器以及latch組成,差分對的輸出作為反相器的輸入,從而確保了電路的對稱性。該緩沖級可以將環形振蕩器的輸出波形變為占空比50%的時鐘信號,并且可以提高驅動能力。

1.4 版圖設計

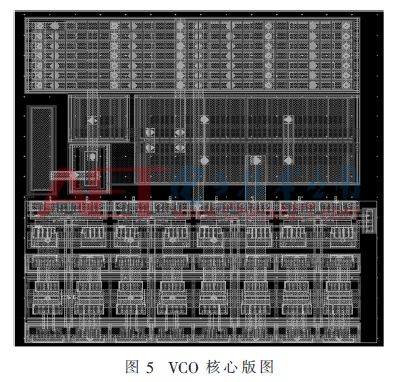

版圖設計是集成電路工藝的重要部分,版圖設計的好壞直接影響芯片的功能。本文設計的環形振蕩器基于TSMC 55 nm工藝,著重分析了VCO匹配和降噪等問題,根據版圖設計的基本規則利用virtuoso Layout Editor工具進行布局布線,并通過了DRC和LVS驗證。設計的環形振蕩器版圖如圖5所示,核心版圖面積為70 μm×81 μm。

1仿真結果

2.1 前仿結果

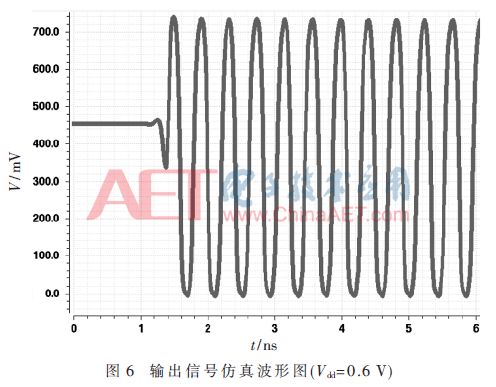

利用Cadence公司Spectre RF仿真工具進行瞬態仿真,結果如圖6所示。從圖中可以看出,當Vdd=0.6 V時,環形振蕩器的起振時間約為1.4 ns,振蕩幅度約為0.74 V。該結果說明振蕩器的起振情況良好,且起振時間比較短。

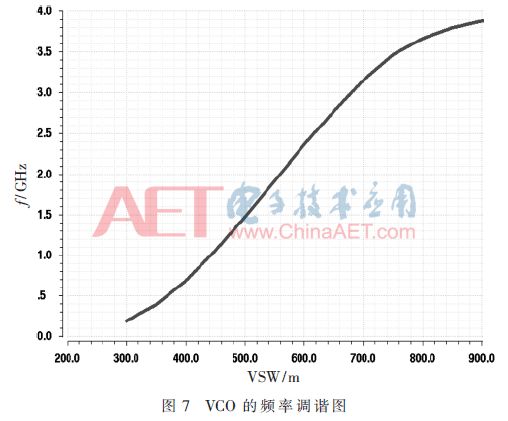

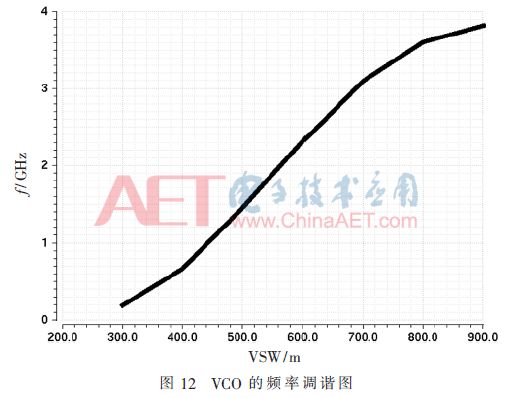

VCO的頻率調諧圖如圖7所示,從圖7可以看出,當控制電壓在0~0.9 V之間變化時,VCO頻率調諧范圍為0.2 GHz~3.8 GHz,且調諧曲線在0.4~0.8 V具有較好的線性度。

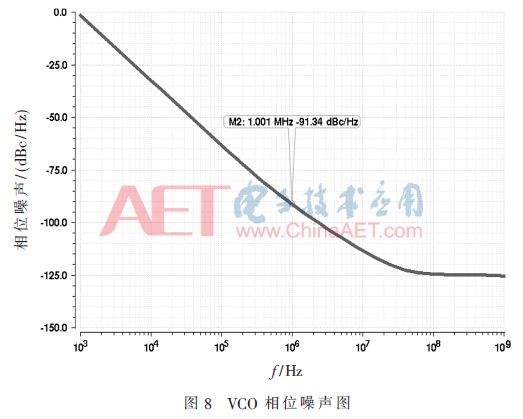

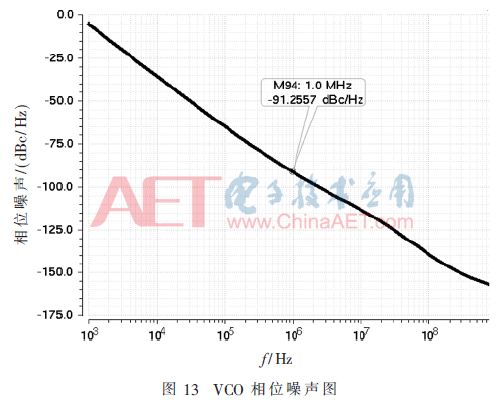

相位噪聲是壓控振蕩器的重要參數和性能指標。壓控振蕩器的相位噪聲性能通過PSS和PNOISE共同仿真得到,頻偏范圍設置為1 kHz到1 GHz。當調諧電壓為0.6 V,輸出中心頻率為2.4 GHz時的整體電路相位噪聲曲線如圖8所示,可見在頻偏1 MHz處,相位噪聲為-91.34 dBc/Hz。

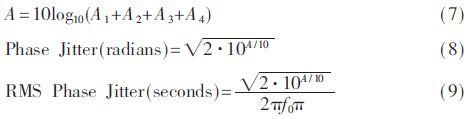

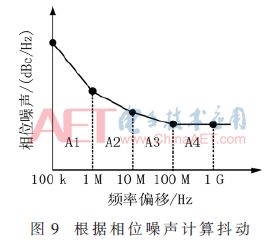

抖動(Jitter)和相位噪聲均是衡量環形振蕩器噪聲性能的參數,抖動是在時域來衡量振蕩器振蕩信號過零點時間的不確定性;相位噪聲是在頻域來衡量振蕩器的頻譜純度,它們在本質上是一樣的,只是運用不同的表述方法來闡述同一種現象[6]。根據相位噪聲計算抖動如圖9所示,設A=面積=綜合相位噪聲功率(dBc),則:

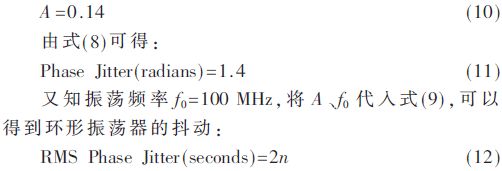

在圖8所示的相位噪聲圖中讀取圖9中各個頻率偏移所對應的相位噪聲。經計算得:

由于低頻VCO通常抖動比較大,一般用PLL環可以有效過濾低頻噪聲。

2.2 后仿真結果

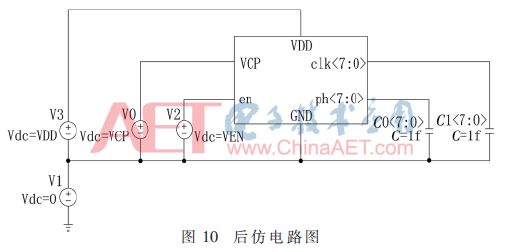

經過對版圖的修改與優化,通過DRC及LVS驗證,運用版圖參數提取工具PEX對版圖進行了寄生電阻、寄生電容等參數的提取。圖10給出了后仿真的電路原理圖。

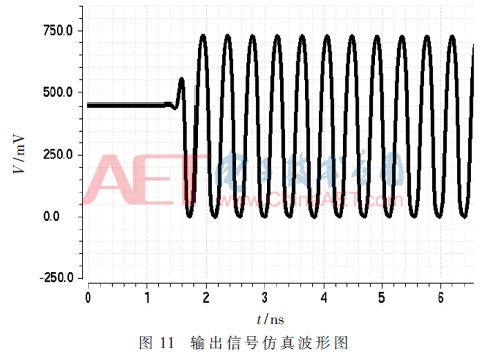

版圖寄生參數提取后,搭建同樣的仿真環境,運用仿真工具分別對VCO穩定振蕩時的瞬態輸出信號波形、調頻特性和相位噪聲性能進行了后仿真,后仿真結果分別如圖11~圖13所示。由圖可知,后仿結果與前仿結果基本一致,可見版圖設計滿足振蕩器的頻率調節范圍在0.2 GHz~3.8 GHz之間,中心頻率處的相位噪聲為-91.34 dBc/Hz@1 MHz,功耗為4.6 mW,線性度良好。

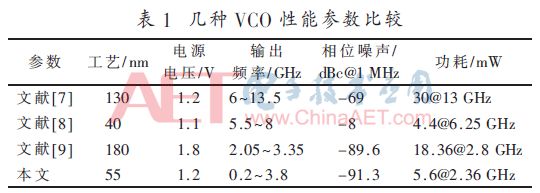

表1總結了設計的環形壓控振蕩器的性能參數,并與工藝條件相近的振蕩器進行對比。可以看出,設計的環形振蕩器在低功耗的條件具有較高的頻率,并且相位噪聲較好。

3結論

基于TSMC 55 nm工藝,采用交叉前饋電路結構設計了一個2.4 GHz的低功耗環形振蕩器,在1.2 V電源電壓下整個環形振蕩器的最大功耗為5.6 mW,相位噪聲為-91.34 dBc/Hz,該VCO具有低功耗、低相噪、可調節范圍寬等優點,可應用于鎖相環、頻率發生器及時鐘恢復等電路。

-

電路

+關注

關注

173文章

5999瀏覽量

173905 -

無線通信

+關注

關注

58文章

4669瀏覽量

144561 -

壓控振蕩器

+關注

關注

10文章

139瀏覽量

29485

原文標題:【學術論文】一種低功耗低噪聲8相位輸出環形振蕩器

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IC設計:一個接入環形振蕩器的奇怪電路

環形振蕩器,環形振蕩器工作原理是什么?

可調可重構的環形振蕩器物理不可克隆函數設計

一種新型交叉前饋結構環形振蕩器電路

一種新型交叉前饋結構環形振蕩器電路

評論