摘要

針對FPGA軟件測試過程中仿真測試和實物測試的不足,提出了一種基于仿真測試用例的實物自動化測試環境,將用于仿真測試的Testbench進行解析處理,形成能夠用于FPGA實物測試的傳輸信號,通過執行器將此信號轉換為作用于被測FPGA芯片的實際信號,并采集被測FPGA芯片的響應,實現對FPGA的實物自動化測試。采用實物自動化測試環境驗證平臺對設計架構進行了驗證,取得了良好的效果。

0 引言

隨著FPGA設計規模的不斷擴大,因FPGA軟件設計而造成的質量問題也越來越突出,成為影響裝備質量的重要因素。而測試是當前解決該問題的最有效手段,因此,越來越多的型號裝備產品定型過程對FPGA軟件測試提出了新的要求[3]。

然而FPGA測試與常規軟件測試不同,因其測試環境限制,測試過程需大量依賴于仿真和分析的方法[4],而在實際芯片中開展的測試往往是板級、系統級測試,測試結果可信度低且無法有效發現FPGA軟件設計缺陷[5-6]。為此,本文提出了一種基于仿真測試平臺Testbench數據的自動化測試環境框架,測試結果具有較高的可信度,能夠有效提高FPGA測試質量。

1 FPGA動態測試概述

1.1 FPGA動態測試環境原理

當前型號裝備FPGA定型測試過程主要方法包括設計檢查、功能仿真、門級仿真、時序仿真、靜態時序分析、邏輯等效性檢查和實物測試。其中功能仿真、門級仿真、時序仿真和實物測試均為動態測試,開展測試時需依據測試要求,建立FPGA運行的外圍環境,根據測試對象的不同,可將此類環境分為仿真測試環境和實物測試環境。

采用仿真測試環境時,需根據測試用例將測試數據映射為不同時刻下的不同信號值,形成仿真測試平臺文件Testbench,通過仿真測試工具將被測FPGA產生的響應進行采集和自動判斷,形成測試結論[7]。

采用實物測試環境時,往往構建系統測試環境,將FPGA與外圍電路、設備一起運行,通過外部總線接口設置激勵數據,然后通過總線輸出接口查看響應結果,人工分析和判斷,形成測試結論[8]。

1.2 FPGA動態測試特點

動態測試因測試實施過程中被測系統處于運行狀態,能夠較為準確地反映系統實際運行時的行為,因此在測試技術中成為最重要的測試手段之一。FPGA動態測試過程通常采用仿真測試與實物測試相結合的方法,通過執行測試用例覆蓋FPGA需求、發現相關缺陷,與靜態測試相比, 具有測試結果直觀、覆蓋率高等優勢。

但是,FPGA動態測試也存在一定弊端,在當前型號測試任務中越來越突出[9-10],主要包括:(1)仿真測試過分依賴于仿真工具的性能;(2)仿真測試覆蓋率因使用IP核等原因無法得到充分保障;(3)實物測試針對系統數據,而無法針對芯片信號。

當前高可靠系統的FPGA動態測試方法作為型號任務測試中的重要測試手段,在工程實踐中雖然能夠發現大量FPGA質量缺陷,但是上述弊端得不到解決,FPGA潛在的質量風險就無法得到有效控制。

2 自動化測試環境設計

2.1 環境需求分析

為提高當前高可靠系統FPGA動態測試的可信性及測試效率,動態測試過程需滿足如下測試要求:

(1)測試激勵應能夠完整反映FPGA芯片的輸入輸出行為,而非系統級測試激勵僅反映應用數據,即測試用例數據需由應用層降低至信號傳輸層。

(2)動態測試的目標FPGA設計需在真實的器件上運行,而非采用仿真工具替代目標FPGA運行。

(3)動態測試激勵的施加及測試結果的采集均能夠滿足FPGA設計需求的精度及實時性,即能夠對被測FPGA設計施加高精度的信號輸入,同時能夠支持對被測FPGA輸出信號的高精度采集;此外,對FPGA各激勵及響應信號的實時性應滿足系統要求[11]。

2.2 環境框架構建

2.2.1 工作原理

為滿足動態測試環境需求,設計基于Testbench的實物測試環境,通過Testbench對測試信號作用域、觸發時刻的描述,解決測試激勵的信號傳輸層需求;通過將Testbench信號轉換成真實的電路信號并施加于真實的被測FPGA芯片,解決被測系統運行的真實性問題;通過高性能FPGA芯片進行Testbench信號描述與真實電路信號的轉換,解決測試激勵及響應的精度及實時性需求。具體工作原理如下:將Testbench進行語義解析,便可獲得測試激勵數據。此激勵數據若不用于仿真,而經過信號分配施加于被測FPGA芯片實體,便可實現基于Testbench的實物測試。同時,解析Testbench中對預期信號的讀取過程,并將被測FPGA實體的輸出信號讀取出來便可獲得被測FPGA的運行結果,然后將實際運行結果與預期結果進行自動比對,便可實現基于Testbench的自動化測試過程。

2.2.2 系統結構

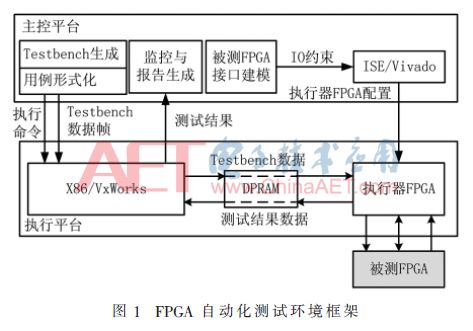

根據Testbench下的FPGA自動化測試工作原理,設計FPGA自動化測試環境框架如圖1所示。

將測試環境按照測試的實時性要求劃分成主控平臺和執行平臺兩部分,主控平臺為非實時節點,執行平臺為實時節點。

主控平臺主要完成測試準備及測試結果分析工作。準備工作包括測試激勵的準備和測試接口的準備。測試激勵的準備是指將Testbench中的測試激勵信息進行解析的過程,具體過程為:在主控平臺中完成Testbench的編輯后,將生成的Testbench經形式化處理,解析成激勵域和結果域兩類字段,每個域字段內均包含時刻、引腳和引腳值3個要素,最終形成包含有測試激勵信息的數據幀消息,并通過以太網將該數據幀消息發送至執行平臺。測試接口的準備是指設計被測FPGA外圍接口模型,并將其綜合、布局布線后下載至一片高性能FPGA(以下稱為執行器FPGA)中等待運行的過程;對于不同的被測FPGA測試項目,需對執行器FPGA分別進行接口模型的創建。測試結果分析工作用于接收測試結果數據,生成測試報告。

執行平臺可視為一個多路信號收發平臺,其接收主控下發的Testbench激勵數據幀消息,并存入大容量DPRAM中,當收到測試執行命令時,將該數據幀消息通過DPRAM發送至執行器FPGA。執行器FPGA按照DPRAM中描述的信號引腳、信號值及信號觸發時間信息,輸出信號至被測FPGA,并按照采集引腳地址及采集時機讀取被測FPGA產生的輸出信號,然后將采集的被測FPGA響應結果通過DPRAM發送給處理器,實時上報至主控平臺,用于監控和測試結果分析。

2.3 關鍵技術

基于Testbench的實物自動化測試環境以Testbench為數據核心,通過執行器FPGA進行數據到信號的轉換,因此,Testbench解析方法及執行器FPGA設計是構建實物自動化測試環境的關鍵技術。

2.3.1 Testbench解析方法

Testbench是開展FPGA測試的數據驅動,也是FPGA測試結果采集的驅動。Testbench由激勵產生、激勵施加、響應判斷3部分構成[12]。在開展基于Testbench的自動化實物測試環境構建中對Testbench的解析主要是指對激勵產生、響應判斷的解析;激勵施加的實質是例化被測FPGA(即DUT,Design Under Test),對于構建自動化實物測試環境并沒有影響。

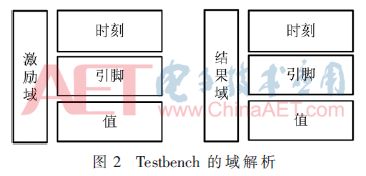

無論采用何種語言構建Testbench,激勵產生都會最終落實為在指定時刻對DUT引腳施加特定值的操作集合,因此可將Testbench的激勵施加過程解析為時刻、引腳、引腳值的集合,命名該集合為激勵域。

Testbench中的響應判斷過程在一系列激勵產生并施加于DUT后實施,與激勵域類似,該過程也可理解為在指定時刻起對DUT引腳采集值的操作集合,該過程也同樣解析為時刻、引腳、引腳值3個要素,并命名該集合為結果域。與激勵域不同的是,結果域中的引腳值用于存儲預期結果數據,該引腳值也可設為空,即無預期結果,表示由人工判定測試結果。

綜上,一個Testbench可以解析為如圖2所示的激勵域及結果域的集合。

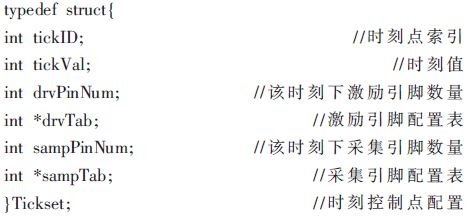

為提高測試環境的時間控制精度并提高存儲效率[13],將一個時刻點下的激勵域及結果域解析為時刻控制點配置結構Tickset,其定義形式如下:

其中,tickVal表示激勵信號觸發的時刻點,drvPinNum用于存儲該時刻點同時為多少個引腳賦值,drvTab是指向具體引腳配置表的指針,引腳配置表結構形式如下:

這樣,一個時刻點即為一個Tickset結構,其中包含了drvPinNum個激勵引腳和sampPinNum個采集引腳,每個引腳的地址和值也都包含在內。

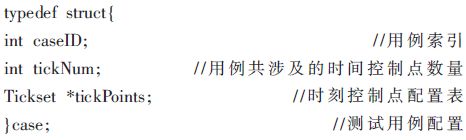

一個Testbench中包含了多個時刻點,共同構成了一個測試用例,因此一個測試用例可定義為case結構,形式如下:

在case結構中包含了tickNum個Tickset,指針變量tickPoints表示具體的時刻控制點配置Tickset集合。

自動化實物測試環境的設計目標之一為提高測試執行效率,為此,可將所有生成的Testbench一次解析,生成測試用例集Caseset,實現測試用例集內用例的不間斷執行。Caseset的定義形式如下:

設計Testbench解析軟件,按照上述約定協議形式將全部Testbench文件進行格式化后解析,最終形成的測試用例集Caseset下發至執行平臺,通過CPU寫入DPRAM中,供執行器FPGA讀取、配置。

2.3.2 執行器FPGA設計

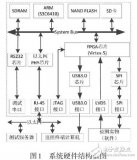

執行器FPGA是銜接被測FPGA與測試環境的接口適配單元,主要完成Testbench數據與電路信號的轉換功能,在整個自動化測試環境中起核心作用。其內部主要模塊及信息傳遞關系如圖3所示。

執行器FPGA讀取DPRAM中的Testbench激勵數據消息,解析出激勵域和結果域,并對將兩個域的時刻控制值交由計數器處理。

激勵域解析模塊讀取DPRAM中激勵數據所要施加的FPGA引腳地址、激勵值[14],然后經地址數據分配模塊進行FPGA引腳索引和數據鎖存,到達激勵觸發時刻后將激勵數據通過指定的引腳輸出至被測FPGA。

結果域解析模塊讀取DPRAM中結果采集所需要的引腳地址、預期結果值,經地址數據分配模塊進行引腳映射,當采集時刻到達時,地址數據分配模塊再從采集緩存中讀取對應的數據值,并與DPRAM中的預期采集結果值進行比較,將該時刻的結論發送至DPRAM用于與實際測試結果一起上傳至主控平臺。

時刻控制模塊是執行器FPGA的控制中樞,一方面,讀取DPRAM中的時刻描述,計算獲得執行器FPGA實際需觸發輸入輸出的時刻,通過計數器控制激勵和采集的使能,從而實現對FPGA信號的實時性傳輸控制;另一方面,通過讀取DPRAM中的測試用例數量、測試激勵域數量、結果域數量、各個域內不同時刻點的引腳信號的數量,管理測試用例中的不同測試時刻的激勵域與結果域數據的時刻、引腳的配置,為激勵域解析模塊和結果域解析模塊實現引腳和數據分配提供依據。

此外,執行器FPGA中還包括由主控平臺被測FPGA接口建模軟件配置的input引腳組、output引腳組及inout引腳組,用于配合地址收分配模塊進行數據管理。

2.4 軟硬件部署

自動化動態測試環境中包括上位機主控平臺和下位機執行平臺兩部分,主控平臺運行于PC無需開展特別硬件設計;執行平臺主要包括X86CPU、DPRAM和執行器FPGA 3部分,其中X86CPU通過DPRAM與執行器FPGA進行數據通信的設計采用常規的DPRAM通信方法。

軟件方面,上位機主控平臺部署Testbench解析軟件,解析Testbench為Caseset測試用例集格式;部署被測FPGA接口建模軟件,通過執行器FPGA集成開發環境ISE的配合實現對執行器FPGA與被測FPGA連接引腳的配置;通過監控與報告生成軟接收并顯示測試執行結果數據,生成測試報告;下位機執行平臺X86CPU運行實時操作系統VxWorks 5.5,進行測試命令的執行及測試數據分發和實時回傳。

3 實驗與應用

基于上述設計方法,開發設計FPGA仿真用例實物化測試環境原型,包含Testbench解析器軟件、FPGA接口建模軟件等核心軟件,將Testbench文件解析成Caseset集合格式;采用XC7VX690T作為執行器FPGA,設計其數據與信號的轉換邏輯,并通過外置接線板與被測FPGA芯片交聯。將該平臺試用于某型衛星導航通信FPGA軟件測試中,與“仿真+系統”測試方式相比,顯著提高了測試工作效率。

4 結論

本文探索性地提出了一種基于仿真測試平臺的實物自動化測試環境,用于FPGA軟件測試中彌補仿真測試和當前實物測試存在的弊端,通過實物自動化測試環境原型對設計框架進行驗證,結果表明該測試環境具有測試覆蓋率高、測試效率高的優點,在后續項目中加以優化便可作為FPGA測試工程實踐的主要工具。

-

FPGA

+關注

關注

1638文章

21860瀏覽量

609889 -

芯片

+關注

關注

459文章

51744瀏覽量

431110 -

仿真測試

+關注

關注

0文章

93瀏覽量

11441

原文標題:【學術論文】基于Testbench的FPGA實物自動化測試環境設計

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

分享一種嵌入式系統自動化測試的詳細方案

OPhone自動化測試技術概述

嵌入式半實物仿真測試ETest-USB架構的相關資料下載

國產嵌入式系統半實物仿真自動化測試系統軟件ETest簡介

一種自動測試系統軟件平臺的設計

一種GUI自動化測試框架方案

評論