國內IC界正經歷著一系列重大動作,圍觀者都在拭目以待著最終結果。雖是微電子專業可惜一直都在岸邊等待著國內IC大潮,只是聞到潮水的咸味,還沒見真正到來,出于專業的原因對于業界的這類大事總是特別留意,如果“趨勢”不出意外,未來的5-10年國內自主設計的大規模IC相信會迎來大發展。

設計的IC規模越大,早期的評估就越顯重要性,國內目前絕大多數IC設計都屬規模較小,有能力做大規模的企業還是少得可憐,出于大環境的因素及這類小項目本身情況,對CO-DESIGN的需求還不明顯。當年做ASIC封裝時,由于芯片規模都較大、對上下游的相互影響也很大,因而CO-DESIGN的流程是必須且重要的,這個流程也是在自己悟出一部份再加自己寫的一些小腳本補充就這樣應付過來了。雖流程自己用起來覺得還算通順,但畢竟沒在統一的環境下完成,總覺得有稍稍不夠完美。

前段與CADENCE技術人員交流時發現,原來已有一個成熟好用的評估工具---OrbitIO!于是自已研究了好幾天還讓他過來現場答疑了3次,自己再寫個新的小腳本終于把這個流程完美打通。

隨著國內以后IC設計規模的增大,這個CO-DESIGN方法的提前準備會給從業者帶來實質的便利,相信用到這個流程而有共鳴者也許是后面幾年后的事情,這與我們4年前出版的《IC封裝基礎與工程設計實例》書一樣超前了些,沒給我帶來實質性的好處!

對于沒有PCB及封裝背景的“專家”要在早期全面評估好一個大規模的芯片:使用何種封裝,如何分配管腳等等,需要與相關領域“專家”反復溝通。為了解放“專家”,這個“神器”就應運而生了,只要你會使用EXCEL就基本可以進行較為精確的評估。

1)下面以一個CASE為思路展開!

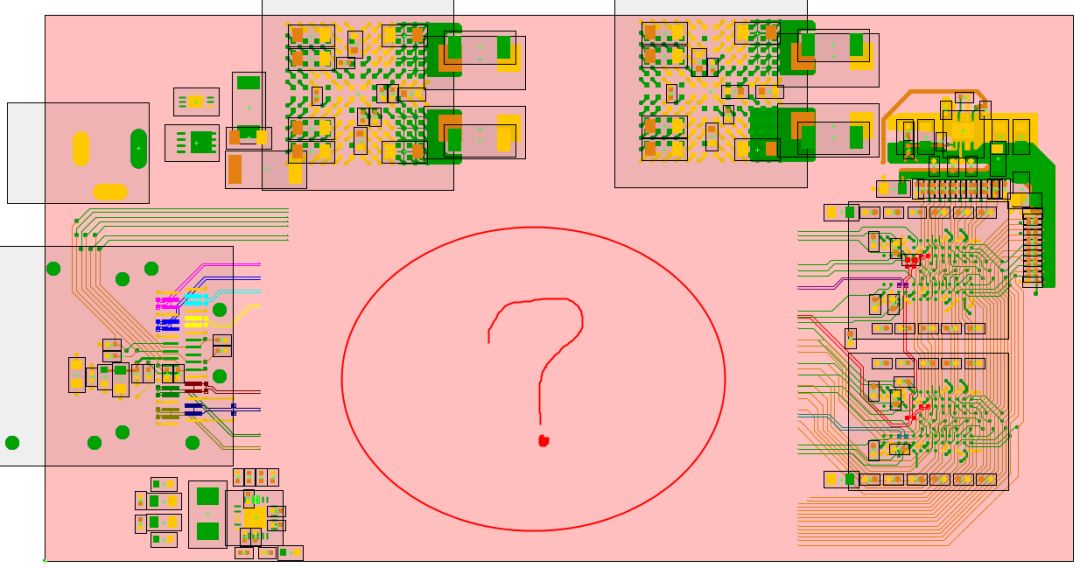

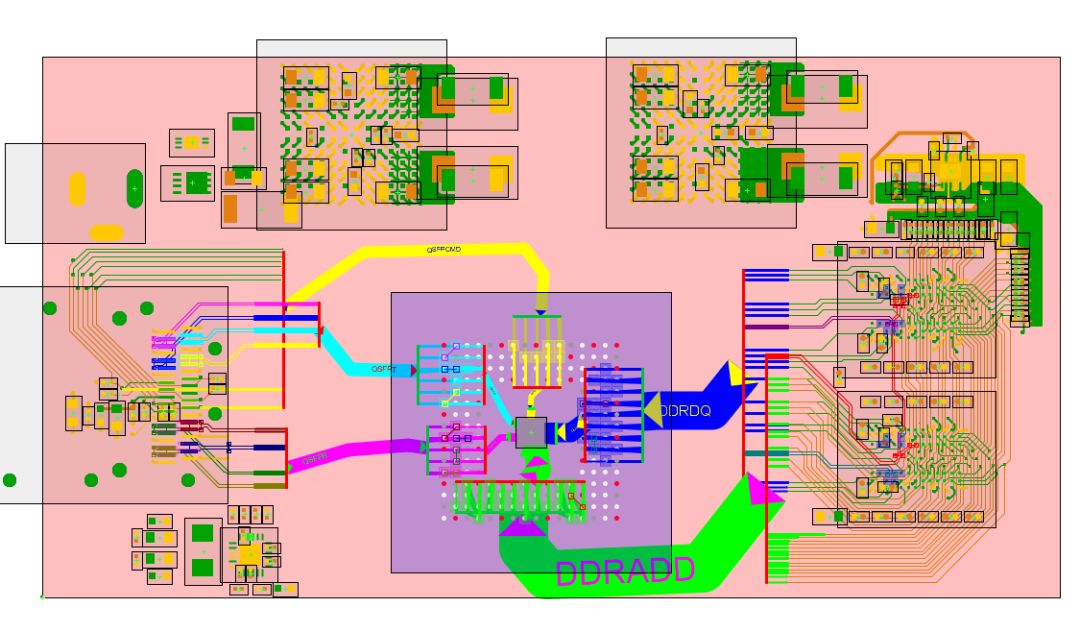

需求:開發一款用于某單板上的特定功能模塊芯片,如何評估新的芯片封裝用多少管腳、封裝需要多大、DIESIZE需要多大及需要多少PAD呢?如下圖提供了新開發的芯片與周邊器件的相對位置的粗略情況。

圖---(1)要開發的芯片在單板中的擺放位置

如你是一個“資深”系統架構師或是“資深”的硬件專家,接下來就有得忙了,因為評估需要輸入數據,你后面的事情基本是圍繞:先找后端的“專家”們商量后,再找封裝的“專家”及PCB的“專家”們商量,要各領域的評估數據,這么一整2天過去了,也許結果還得再等等,急也沒用,因為“部門墻”是實實在在的存在,不同部門都在“忙”著,你還真沒辦法!

是否想過這個評估工作在初期“專家自己”也可以獨立完成呢?不用求其它的“專家”們呢?而且還可以得到一個很靠譜的評估結果。

答案是肯定的,看看下面的做法!

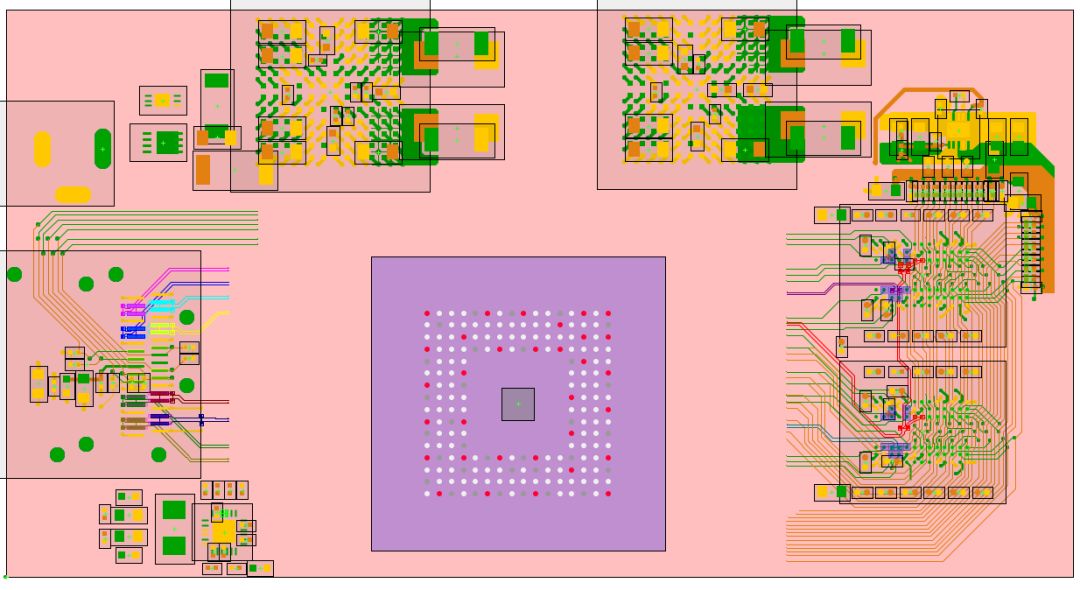

第一步就是估算接口的數量及電源、地的比例,找一個PIN數差不多的BGA封裝及把一個相應數量PAD的DIE一起放在同一個界面中(這個界面就是提到的OrbitIO,一種把IC-PAKCAGE-PCB都導入到同一個平臺下處理的軟件)如下圖。

圖(2)---放入空白的BGA及DIE

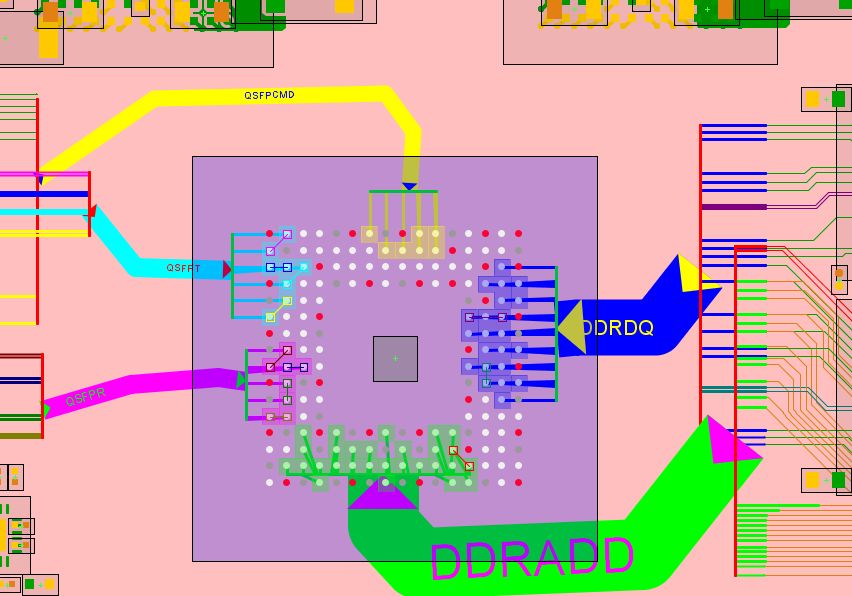

接下來“專家自己”就可以在OrbitIO平臺下進行布線規劃評估了,這個過程只需幾分鐘,從下圖可見,從PCB引線到BGA封裝且自動分配好管腳,很直觀且高效。

圖(3)---PCB周邊器件往BGA空管腳上分配網絡

忙完了從PCB到BGA的管腳引線,接下來就是從BGA中往DIE上的PAD分配網絡,這個過程也是幾分鐘!效果同樣是很直觀、高效。

圖(4)---BGA往DIE空管腳上分配網絡

最后的BGA及DIE網絡分配完成效果如下圖,結果令人很興奮,效果直觀、結果靠譜!

圖(5)---從PCB往BGA再往IC上的管腳分配網絡整體效果

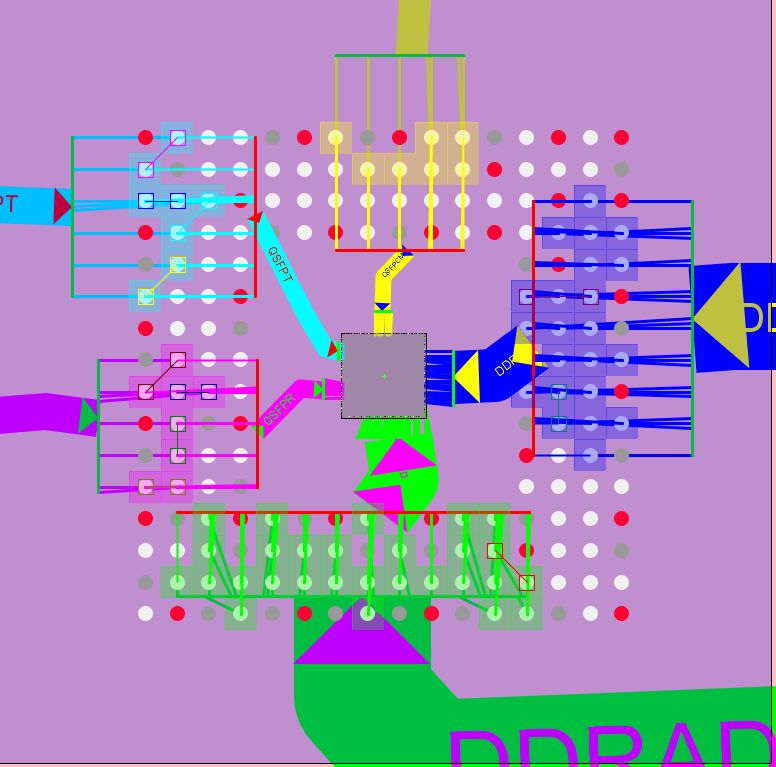

整個過程的評估操作只需要4分多鐘,芯片越復雜越能體現這個方法與流程的優越性,平時只做PIN數較少的芯片難有機會真正體會到其中的奧秒之處了。

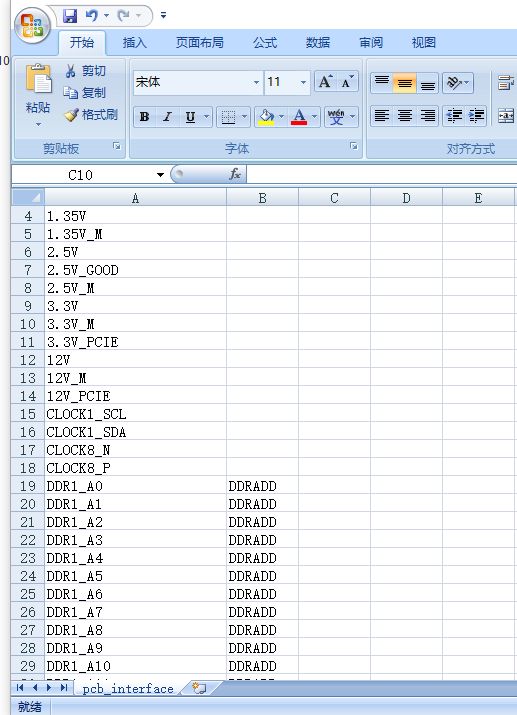

作為一個“專家”在評估復雜封裝及芯片時最害怕的一件事是:需求經常在變、接口經常在變,因為這又得找其它領域的“專家”重新評估,這時使用新工具平臺就很有必要了,因為OrbitIO提供的平臺與使用方法太簡單且直觀,不需要太多的IC、封裝及PCB等背景知識,只需要在EXCEL中處理下,如下圖在EXCEL進行接口的分組。

圖(6)---在EXCEL中對芯片的接口分組

原來幾個部門不同人協調2天的活,現在只要很短時間就可以由一個人完全搞定。當然在后面的APD與PCB間的相互導入更細致的話就更完美了,有興趣也可以與作者進一步深入交流。

-

pcb

+關注

關注

4324文章

23155瀏覽量

399100 -

嵌入式

+關注

關注

5089文章

19169瀏覽量

306769 -

微電子

+關注

關注

18文章

387瀏覽量

41243

原文標題:專家講壇 | IC-PKG-PCB CO-DESIGN探討---方案快速評估

文章出處:【微信號:CadencePCB,微信公眾號:CadencePCB和封裝設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于模塊電源的船舶集控系統嵌入式單板機電源設計

瑞薩RA-T系列芯片ADC和GPT功能模塊的配合使用

開發一款用于某單板上的特定功能模塊芯片

開發一款用于某單板上的特定功能模塊芯片

評論