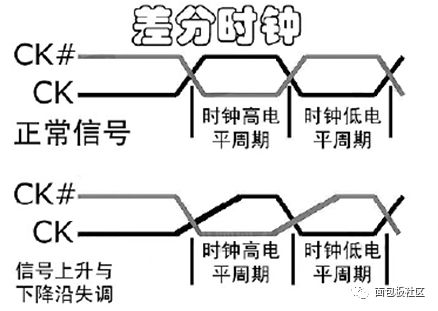

關(guān)鍵技術(shù)之一:差分時(shí)鐘

差分時(shí)鐘是DDR的一個(gè)非常重要的設(shè)計(jì),是對(duì)觸發(fā)時(shí)鐘進(jìn)行校準(zhǔn),主要原因是DDR數(shù)據(jù)的雙沿采樣。由于數(shù)據(jù)是在時(shí)鐘的上下沿觸發(fā),造成傳輸周期縮短了一半,因此必須要保證傳輸周期的穩(wěn)定以確保數(shù)據(jù)的正確傳輸,這就對(duì)CK的上下沿間距有了精確的控制的要求。

一般說(shuō)來(lái),因?yàn)闇囟取?a target="_blank">電阻性能的改變等原因,CK上下沿間距可能發(fā)生變化,此時(shí)與其反相的CK#就起到糾正的作用,因?yàn)椋珻K上升沿快下降沿慢,CK#則是上升沿慢下降沿快。也就是,與CK反相的CK#保證了觸發(fā)時(shí)機(jī)的準(zhǔn)確性。

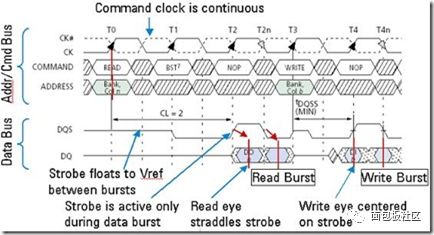

關(guān)鍵技術(shù)之二:數(shù)據(jù)選取脈沖(DQS)

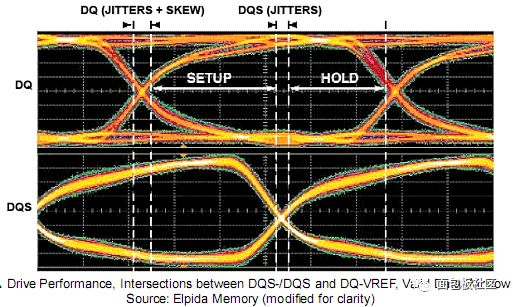

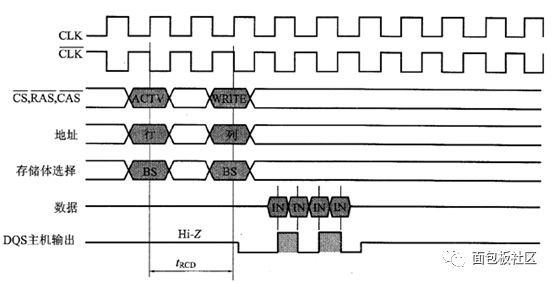

DQS是DDR SDRAM中的另一項(xiàng)關(guān)鍵技術(shù),它的功能是用來(lái)在一個(gè)時(shí)鐘周期內(nèi)準(zhǔn)確的區(qū)分出每個(gè)傳輸周期,并便于接收方準(zhǔn)確接收數(shù)據(jù)。每一顆芯片都有一個(gè)DQS信號(hào)線(xiàn),它是雙向的,在寫(xiě)入時(shí)它用來(lái)傳送由芯片發(fā)來(lái)的DQS信號(hào),讀取時(shí),則由內(nèi)存生成DQS向芯片發(fā)送。因此可以認(rèn)為DQS就是數(shù)據(jù)的同步信號(hào)。

我們知道DDR之前的SDR就是使用clock來(lái)同步的,因此理論上,DQ的讀寫(xiě)時(shí)序完全可以由clock來(lái)同步。但是,由于速度提高之后,可用的時(shí)序余量越來(lái)越小,而引入DQS是為了降低系統(tǒng)設(shè)計(jì)的難度和可靠性,也就是可以不用考慮DQ和clock之間的直接關(guān)系,只用分組考慮DQ和DQS之間的關(guān)系,很容易同組同層處理。

DQ和DQS只是組成了源同步時(shí)序的傳輸關(guān)系,可以保證數(shù)據(jù)在接收端被正確的所存,但是IC工作時(shí),內(nèi)部真正的同步時(shí)鐘是clock而不是DQS,數(shù)據(jù)要在IC內(nèi)部傳輸存儲(chǔ)同樣需要和clock(內(nèi)部時(shí)鐘比外部時(shí)鐘慢)去同步,所以就要求所有的DQ信號(hào)還是同步的,而且和clock保持一定的關(guān)系,所以就要控制DQS和clock之間的延時(shí)了。

在寫(xiě)入時(shí),以DQS的高/低電平期中部為數(shù)據(jù)周期分割點(diǎn),而不是上/下沿,但數(shù)據(jù)的接收觸發(fā)仍為DQS的上/下沿。

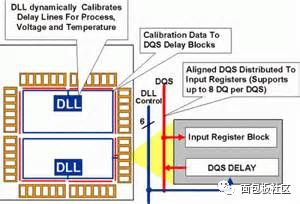

關(guān)鍵技術(shù)之三:延遲鎖定回路(DLL)

第三個(gè)關(guān)鍵技術(shù)是DLL技術(shù),也就是延遲鎖定回路。需要這種技術(shù)的原因是,內(nèi)外時(shí)鐘的不同步問(wèn)題。內(nèi)外時(shí)鐘不同步在SDRAM中就存在了,不過(guò)因?yàn)樗墓ぷ?傳輸頻率較低,所以?xún)?nèi)外同步問(wèn)題并不突出。

但是,DDR SDRAM對(duì)時(shí)鐘的精確性有著很高的要求,而DDR SDRAM有兩個(gè)時(shí)鐘,一個(gè)是外部的總線(xiàn)時(shí)鐘,一個(gè)是內(nèi)部的工作時(shí)鐘,在理論上DDR SDRAM這兩個(gè)時(shí)鐘應(yīng)該是同步的,但由于種種原因,比如溫度、電壓波動(dòng)而產(chǎn)生延遲使兩者很難同步,更何況時(shí)鐘頻率本身也有不穩(wěn)定的情況。我們熟悉的DDR SDRAM的tAC就是因?yàn)閮?nèi)部時(shí)鐘與外部時(shí)鐘有偏差而引起的,它很可能造成因數(shù)據(jù)不同步而產(chǎn)生錯(cuò)誤。

怎么解決呢?實(shí)際上,因?yàn)椴煌骄褪且环N正/負(fù)延遲,如果延遲不可避免,那么若是設(shè)定一個(gè)延遲值,如一個(gè)時(shí)鐘周期,那么內(nèi)外時(shí)鐘的上升與下降沿還是同步的。鑒于外部時(shí)鐘周期也不會(huì)絕對(duì)統(tǒng)一,所以需要根據(jù)外部時(shí)鐘動(dòng)態(tài)修正內(nèi)部時(shí)鐘的延遲來(lái)實(shí)現(xiàn)與外部時(shí)鐘的同步,這就是DLL的任務(wù)。

DLL主要的目的就是生成一個(gè)延遲量給內(nèi)部時(shí)鐘,來(lái)補(bǔ)充正負(fù)不同步造成的正負(fù)延遲。

有了這些技術(shù)就構(gòu)成了內(nèi)存帝國(guó)的最基本的元素,之后的DDR2,DDR3和DDR4以及即將推出的DDR5將以此為基礎(chǔ),內(nèi)存的功耗及頻率得到一次又一次的飛躍。

-

dll

+關(guān)注

關(guān)注

0文章

116瀏覽量

45961 -

DDR

+關(guān)注

關(guān)注

11文章

719瀏覽量

66145 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3099瀏覽量

74851

原文標(biāo)題:DDR的概念解讀-三大關(guān)鍵技術(shù)

文章出處:【微信號(hào):gh_bee81f890fc1,微信公眾號(hào):面包板社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談華為通信大模型的關(guān)鍵技術(shù)

直流充電測(cè)試負(fù)載關(guān)鍵技術(shù)解析

圓柱鋰電池自動(dòng)點(diǎn)焊機(jī):關(guān)鍵技術(shù)解析與產(chǎn)業(yè)化應(yīng)用進(jìn)展

Arm帶你了解2025年及未來(lái)在不同技術(shù)市場(chǎng)的關(guān)鍵技術(shù)方向

鴻道Intewell工業(yè)操作系統(tǒng),三大關(guān)鍵技術(shù),領(lǐng)跑行業(yè)前沿

云計(jì)算HPC軟件關(guān)鍵技術(shù)

探究三相電阻焊控制器在現(xiàn)代焊接工藝中的關(guān)鍵技術(shù)應(yīng)用與實(shí)踐

先進(jìn)雙向點(diǎn)焊控制器在工業(yè)生產(chǎn)中的關(guān)鍵技術(shù)應(yīng)用與解析

華為發(fā)布兩大關(guān)鍵創(chuàng)新技術(shù)方向

實(shí)驗(yàn)室被動(dòng)式空氣凈化技術(shù)關(guān)鍵技術(shù)解析

機(jī)載低軌衛(wèi)星通信發(fā)展及關(guān)鍵技術(shù)綜述

面向手機(jī)直連的星載相控陣:關(guān)鍵技術(shù)與未來(lái)展望

儲(chǔ)能BMS的關(guān)鍵技術(shù)是什么

高通賦能互聯(lián)未來(lái):5G Advanced Release 18中的五大關(guān)鍵技術(shù)發(fā)明

智能電網(wǎng)十大關(guān)鍵技術(shù)解析

評(píng)論