概述

AD9524提供低功耗、多路輸出時鐘分配功能,具有低抖動性能,還配有片內(nèi)集成鎖相環(huán)(PLL)和電壓控制振蕩器(VCO)。片內(nèi)VCO的調(diào)諧頻率范圍為3.6 GHz至4.0 GHz。

數(shù)據(jù)表:*附件:AD9524 6路輸出、雙環(huán)路時鐘發(fā)生器技術(shù).pdf

AD9524旨在滿足長期演進(jìn)(LTE)和多載波GSM基站設(shè)計的時鐘要求。它依靠外部VCXO清除參考抖動,以滿足嚴(yán)格的低相位噪聲要求,從而獲得可接受的數(shù)據(jù)轉(zhuǎn)換器信噪比(SNR)性能。

輸入接收器、振蕩器和零延遲接收器支持單端和差分兩種操作。當(dāng)連接到恢復(fù)的系統(tǒng)參考時鐘和VCXO時,器件產(chǎn)生1 MHz至1 GHz范圍內(nèi)的6路低噪聲輸出,以及一路來自PLL1的專用緩沖輸出。一路時鐘輸出相對于另一路時鐘輸出的頻率和相位可通過分頻器相位選擇功能改變,該功能用作無抖動的時序粗調(diào),其調(diào)整增量相當(dāng)于VCO輸出信號的周期。

通過串行接口可以對封裝內(nèi)EEPROM進(jìn)行編程,以便存儲用于上電和芯片復(fù)位的用戶定義寄存器設(shè)置。

應(yīng)用

- LTE和多載波GSM基站

- 無線和寬帶基礎(chǔ)設(shè)施

- 醫(yī)療儀器

- 為高速ADC、DAC、DDS、DDC、DUC、MxFE提供時鐘

- 低抖動、低相位噪聲時鐘分配

- SONET、10Ge、10G FC和其它10 Gbps協(xié)議的時鐘產(chǎn)生和轉(zhuǎn)換

- 前向糾錯(G.710)

- 高性能無線收發(fā)器

- 自動測試設(shè)備(ATE)和高性能儀器儀表

特性

- 輸出頻率:<1 MHz至1 GHz

- 啟動頻率精度:<±100 ppm(由VCXO參考精度決定)

- 零延遲操作

輸入至輸出邊沿時序:<±150 ps - 6路輸出:可配置為LVPECL、LVDS、HSTL和LVCMOS

- 6個具有零抖動可調(diào)延遲的專用輸出分頻器

- 可調(diào)延遲:63個分辨率步進(jìn),步長等于VCO輸出分頻器的?周期

- 輸出間偏斜:<±50 ps

- 針對奇數(shù)分頻器設(shè)置提供占空比校正

- 上電時所有輸出自動同步

- 非易失性EEPROM存儲配置設(shè)置

- 欲了解更多特性,請參考數(shù)據(jù)手冊

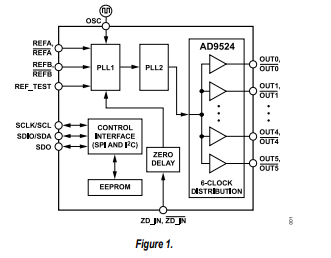

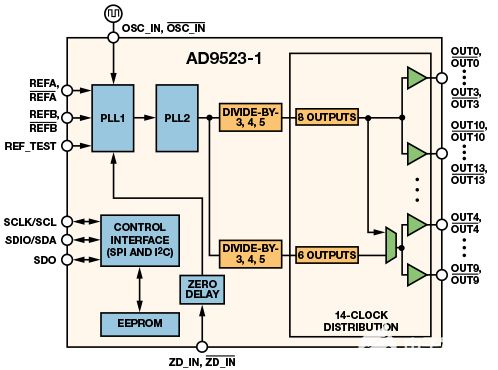

框圖

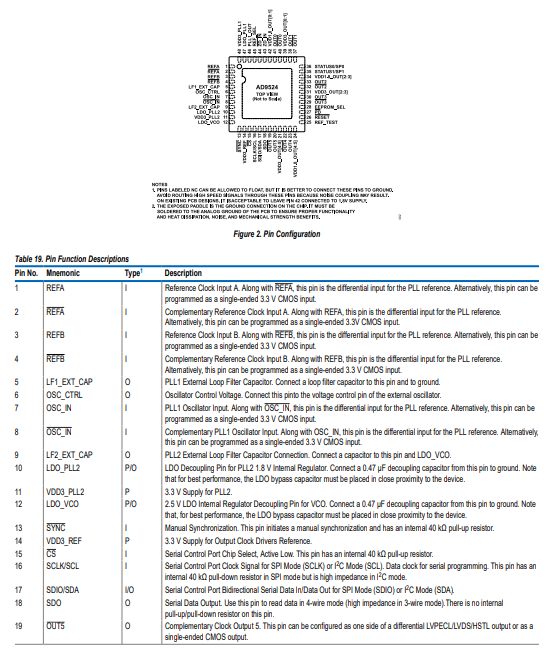

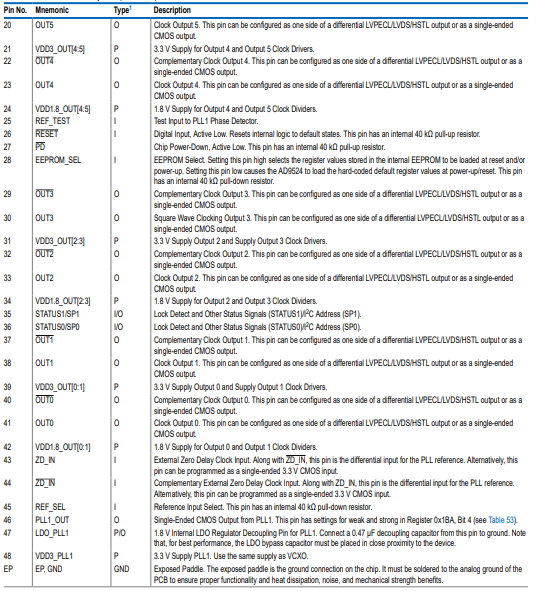

引腳配置描述

典型性能特征

AD9524是一款采用基于整數(shù)N的鎖相環(huán)(PLL)的時鐘發(fā)生器。該器件架構(gòu)由兩個級聯(lián)的PLL級組成。第一級PLL1,是一個整數(shù)除法PLL,它使用一個外部壓控晶體振蕩器(VCXO),最高可達(dá)250MHz。PLL1具有較窄的環(huán)路帶寬,可對輸入?yún)⒖夹盘栠M(jìn)行初始的抖動消除。第二級PLL2,是一個頻率乘法PLL,它將第一級的輸出頻率轉(zhuǎn)換到3.6GHz至4.0GHz的范圍。PLL2集成了一個基于整數(shù)的反饋分頻器,可實(shí)現(xiàn)整數(shù)倍頻。可編程整數(shù)分頻器(1至1024)跟隨PLL2,最終確定1GHz的輸出頻率。

AD9524包含信號處理模塊,可在兩個參考輸入之間實(shí)現(xiàn)平滑切換。該電路會自動檢測參考輸入信號的存在。如果只有一個輸入存在,器件將其作為活動參考。如果兩個輸入都存在,其中一個將成為活動參考,另一個則成為備用參考。如果活動參考失效,電路會自動切換到備用參考(如果有),使其成為新的活動參考。

寄存器設(shè)置決定了在失效參考再次可用時采取的行動:是留在參考B上,還是恢復(fù)到參考A。如果可以使用其他參考,AD9524支持保持模式。參考選擇引腳(REF_SEL,引腳45)可用于手動選擇哪個參考處于活動狀態(tài)(見表43)。保持模式的精度取決于VCO在半電源電壓下的頻率穩(wěn)定性。

任何分頻器設(shè)置都可通過串行編程端口進(jìn)行編程,從而實(shí)現(xiàn)廣泛的輸入/輸出頻率比。這些分頻器還包括一個可編程延遲,可在需要時調(diào)整輸出信號的時序。

輸出端口與LVPECL、LVDS或HSTL邏輯電平兼容(見輸入/輸出端接建議部分);然而,AD9524僅采用CMOS工藝實(shí)現(xiàn)。

每個PLL的環(huán)路濾波器都是集成且可編程的。兩個PLL環(huán)路濾波器中,每個僅需一個外部電容。

AD9524的工作溫度范圍為擴(kuò)展工業(yè)溫度范圍 -40°C至85°C。

組件模塊 - 輸入PLL(PLL1)

PLL1 總體描述

從根本上講,輸入PLL(稱為PLL1)由鑒頻鑒相器(PFD)、電荷泵、無源環(huán)路濾波器以及外部VCO組成,它們在閉環(huán)中運(yùn)行。

PLL1具有以約10Hz至100Hz的窄環(huán)路帶寬運(yùn)行的靈活性。這種相對較窄的環(huán)路帶寬賦予AD9524抑制參考輸入抖動的能力。出現(xiàn)在PLL1上的抖動隨后會形成參考輸入系統(tǒng)時鐘的低相位噪聲版本。

-

發(fā)生器

+關(guān)注

關(guān)注

4文章

1389瀏覽量

62335 -

pll

+關(guān)注

關(guān)注

6文章

838瀏覽量

135869 -

時鐘

+關(guān)注

關(guān)注

11文章

1853瀏覽量

132621

發(fā)布評論請先 登錄

相關(guān)推薦

AD9571ACPZPEC時鐘發(fā)生器銷售

MAX3624 低抖動、精密時鐘發(fā)生器,提供四路輸出

MAX3679A高性能四路輸出時鐘發(fā)生器(Maxim)

抖動器和時鐘發(fā)生器的6分或13的LVCMOS輸出ad9524數(shù)據(jù)表

AD9524 6路輸出、雙環(huán)路時鐘發(fā)生器

AD9523時鐘發(fā)生器的性能特點(diǎn)及應(yīng)用分析

AD9520-0:12路LVPECL/24路CMOS輸出時鐘發(fā)生器,集成2.8 GHz VCO

AD9523-1:低抖動時鐘發(fā)生器,14路LVPECL/LVDS/HSTL輸出或29路LVCMOS輸出 數(shù)據(jù)手冊

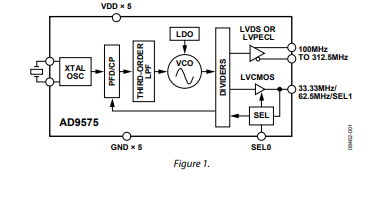

AD9575:網(wǎng)絡(luò)時鐘發(fā)生器,雙輸出數(shù)據(jù)表

雙環(huán)路時鐘發(fā)生器清除抖動,提供多個高頻輸出

AD9575雙路輸出網(wǎng)絡(luò)時鐘發(fā)生器技術(shù)手冊

評論