概述

AD9525旨在滿足長期演進(LTE)和多載波GSM基站設計的轉換器時鐘要求。

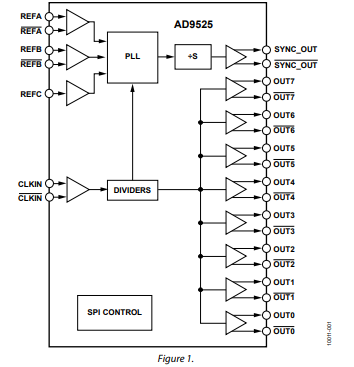

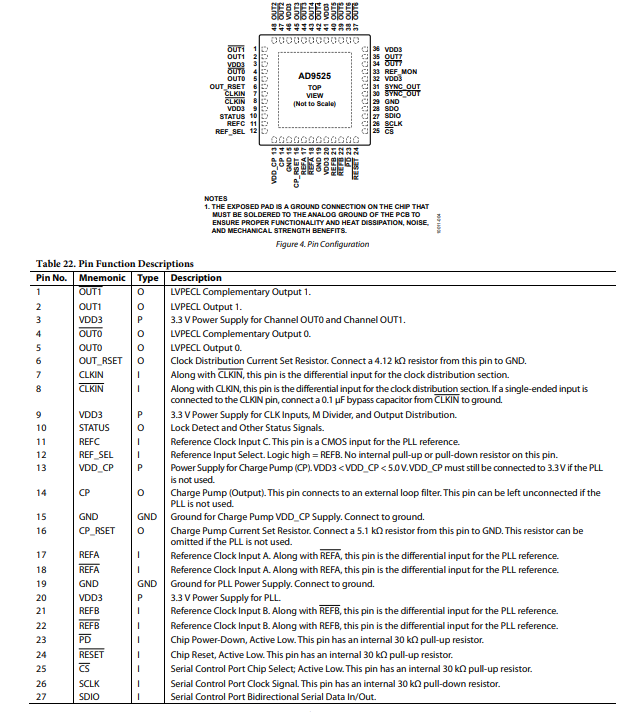

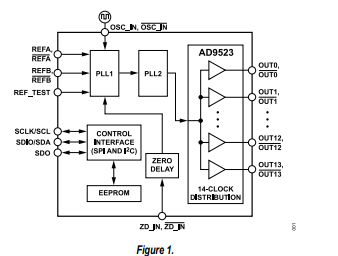

AD9525提供低功耗、多路輸出時鐘分配功能,具有低抖動性能,并且片內集成鎖相環(PLL),可以配合外部VCO或VCXO使用。VCO輸入和八個LVPECL輸出最高工作頻率為3.6 GHz。所有輸出共用一個分頻器,分頻范圍為1到6。

AD9525提供了一個專用輸出,可用于提供一個用于重置或同步數據轉換器的可編程信號。輸出信號可以通過一個SPI寫入操作激活。

AD9525提供48引腳LFCSP封裝,可以采用3.3 V單電源供電。外部VCXO或VCO的工作電壓最高可達5.5 V。

AD9525的工作溫度范圍為?40°C至+85°C的擴展工業溫度范圍。

數據表:*附件:AD9525旨在滿足長期演進(LTE)和多載波GSM基站設計的轉換器時鐘技術手冊.pdf

特性

- 集成超低噪聲頻率合成器

- 8個差分3.6 GHz LVPECL輸出和1個LVPECL或2個CMOS SYNC輸出

- 2個差分參考輸入和1個單端參考輸入

應用

LTE和多載波GSM基站

為高速ADC、DAC提供時鐘

自動測試設備(ATE)和高性能儀器儀表

40/100Gb/s OTN線路端時鐘

電纜/DOCSIS CMTS時鐘

測試與測量

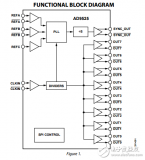

框圖

引腳配置描述

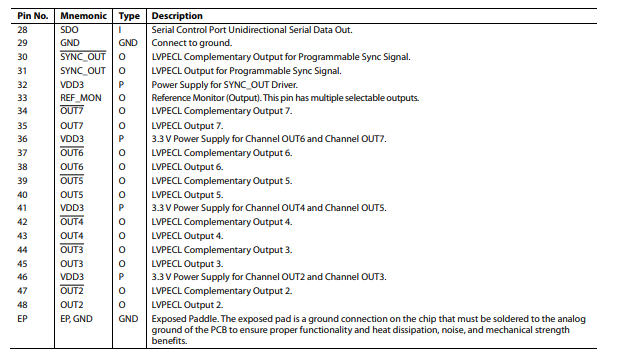

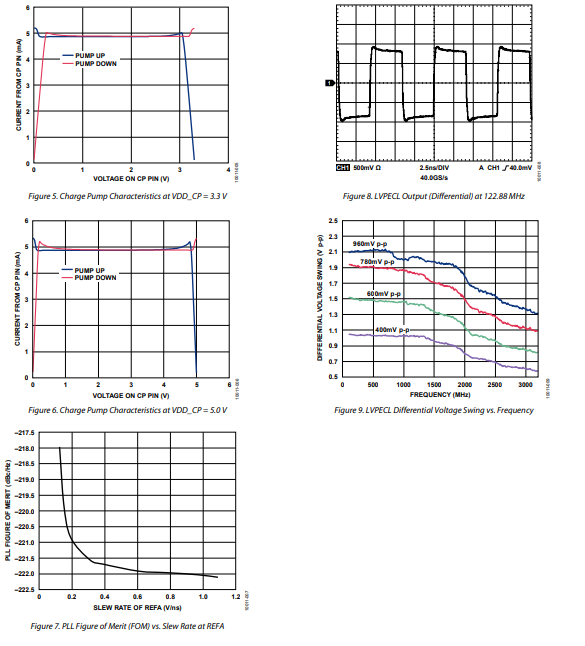

典型性能特征

術語解釋

相位抖動和相位噪聲

理想正弦波可被視為在每個周期內,相位隨時間從0°到360°持續且均勻地變化。實際信號會在一段時間內顯示出與理想相位變化的偏差量,這種現象被稱為相位抖動。盡管有許多因素會導致相位抖動,但一個主要因素是隨機噪聲,其統計特性呈高斯(正態)分布。

這種相位抖動會導致正弦波在頻域中的能量擴散,產生連續的功率譜。該功率譜通常以給定頻率偏移處每單位Hz的dBc值來表示,它是相對于載波頻率功率,在1Hz帶寬內所包含功率的比值(以分貝表示) 。對于每次測量,偏移頻率處的功率值也會給出。

對某一頻率偏移區間(例如10kHz到10MHz)內的總功率進行積分也具有實際意義。這被稱為該頻率偏移區間上的積分相位噪聲;它能直觀地反映出該頻率偏移區間內相位噪聲所導致的時間抖動情況。

相位噪聲對模數轉換器(ADC)、數模轉換器(DAC)和射頻混頻器的性能有不利影響。它會降低這些轉換器和混頻器可實現的動態范圍,盡管影響方式略有不同。

時間抖動

相位噪聲是頻域現象,而在時域中,其表現為時間抖動。觀察正弦波時,兩個連續過零點之間的時間會發生變化。觀察方波時,(時間)抖動表現為信號邊沿與理想(規則)觸發時刻的偏差。在這兩種情況下,與理想時間的偏差量就是時間抖動。由于這些變化是隨機的,所以時間抖動的規格以均方根(rms)或1σ(高斯分布中的1個標準差)表示。

在數模轉換器(DAC)或模數轉換器(ADC)的采樣時鐘上出現的時間抖動,會降低信號噪聲比(SNR)和動態范圍。最低的可能抖動能使給定轉換器發揮出最高性能。

附加相位噪聲

附加相位噪聲是指可歸因于被測外部振蕩器或時鐘源的相位噪聲量。通過減去任何外部振蕩器或時鐘源的相位噪聲,就可以預測該器件在與各種振蕩器和時鐘源配合使用時,對系統總相位噪聲的影響程度,因為每個振蕩器和時鐘源都會對總相位噪聲產生各自的貢獻。在許多情況下,一個元件的相位噪聲會主導系統的相位噪聲。當存在多個相位噪聲源時,總相位噪聲是各個貢獻源的均方根總和。

附加時間抖動

附加時間抖動是指可歸因于被測外部器件或子系統的時間抖動量。通過減去任何外部振蕩器或時鐘源的時間抖動,就能夠預測該器件在與各種振蕩器和時鐘源配合使用時,對系統總時間抖動的影響程度,因為每個振蕩器和時鐘源都會對總時間抖動產生各自的貢獻。在許多情況下,一個外部振蕩器或時鐘源的時間抖動會主導系統的時間抖動。

-

轉換器

+關注

關注

27文章

8884瀏覽量

150070 -

LTE

+關注

關注

15文章

1364瀏覽量

178679 -

時鐘

+關注

關注

11文章

1856瀏覽量

132638 -

GSM

+關注

關注

9文章

836瀏覽量

123667 -

AD9525

+關注

關注

0文章

5瀏覽量

9208

發布評論請先 登錄

相關推薦

ADI推出業界最低抖動RF時鐘IC AD9525

用于評估AD9525 3.6 GHz時鐘發生器的評估板AD9525/PCBZ

用于評估AD9525 2950 MHz VCO時鐘發生器的評估板AD9525/PCBZ-VCO

Xilinx推出Smarter無線電解決方案 可滿足新一代LTE與多載波GSM平臺性能需求

低電壓輸出低抖動時鐘發生器ad9525數據表

AD9525 AD9525旨在滿足長期演進(LTE)和多載波GSM基站設計的轉換器時鐘要求。

評論