小數分頻頻率合成器的實現方法有多種,如Pulse swallowing、Pulse interpolatoin、Wheately random jittering、Σ-Δ modulation[1],其中Σ-Δ modulation架構以其優良的相噪指標及全數字化而成為小數分頻頻率合成器的主流。本文旨在分析Σ-Δ量化噪聲對小數分頻頻率合成器相位噪聲及雜散的影響,找到適合于小數分頻頻率合成器的Σ-Δ調制器。

1相位噪聲

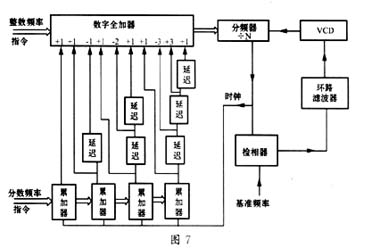

基于鎖相環閉環回路實現小數分頻頻率合成器,建立線性數學模型,分析其相位噪聲源及傳遞函數。

1.1 相位噪聲模型

Rohde已經闡明[2],PLL的每個組成部分都產生噪聲。小數分頻頻率合成器主要相位噪聲源有參考時鐘相位噪聲θref(t)、PFD相位噪聲θPFD(t)、VCO相位噪聲θVCO(t)、分頻器相位噪聲θdiv(t)、Σ-Δ量化噪聲。

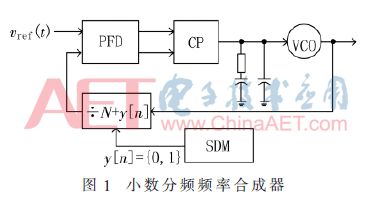

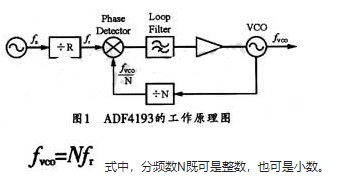

基于鎖相環小數分頻頻率合成器如圖1所示。

定義τn為第n個參考時鐘的上升沿時刻,則:[3]

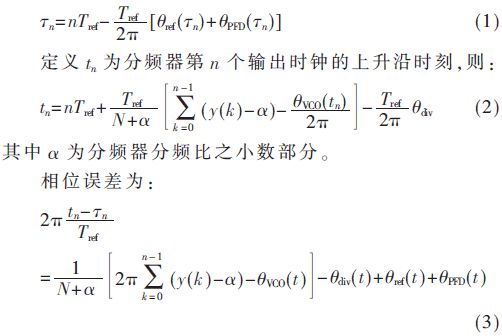

由相位誤差公式及圖1,可以推得圖2所示的Σ-Δ小數分頻頻率合成器相位噪聲線性模型。

1.2 相位噪聲分析

Σ-Δ小數分頻頻率合成器相位噪聲源到輸出端的傳遞函數除VCO相位噪聲傳遞函數為高通濾波傳遞函數外,其余噪聲源到輸出端的傳遞函數均為低通濾波傳遞函數。本文著重分析Σ-Δ量化噪聲對輸出相位噪聲的影響。

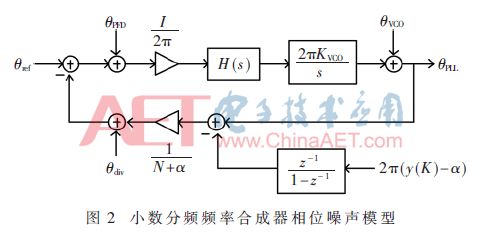

圖2中(y(k)-α)為Σ-Δ量化噪聲q(t),其Z域傳遞函數NTF(z)=(1-z-1)L[4]。由量化噪聲注入到PLL的相位噪聲為:

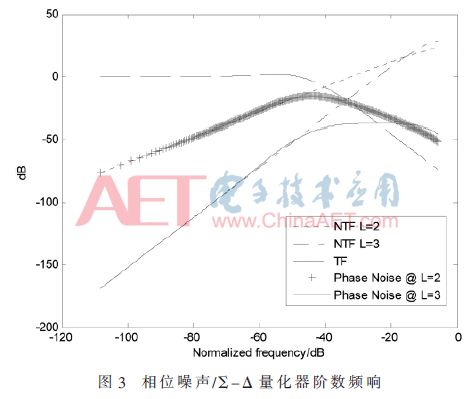

1.2.1 Σ-Δ量化器階數對相位噪聲的影響

MATLAB繪制不同Σ-Δ量化器階數,量化噪聲引起的PLL輸出相位噪聲頻域響應,如圖3所示。曲線“.”為二階Σ-Δ量化器注入到頻率合成器的相位噪聲

可見,Σ-Δ量化器階數越高,小數分頻頻率合成器帶內相位噪聲越低。

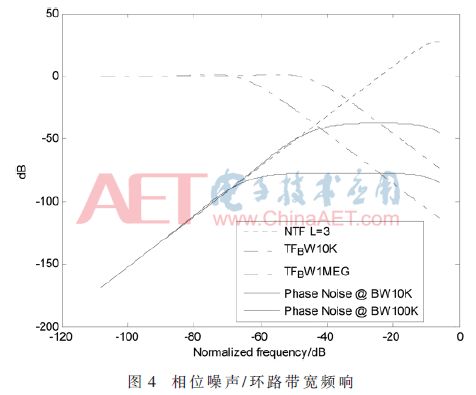

1.2.2 環路帶寬對相位噪聲的影響

圖4為3階Σ-Δ量化器,在不同PLL環路濾波器帶寬條件下,小數分頻頻率合成器帶相位噪聲頻譜圖。曲線“.”為三階Σ-Δ量化器相位噪聲;曲線“.-”分別為帶寬10 kHz與1 MHz頻率合成器相位噪聲傳遞函數;實線分別為帶寬10 kHz與1 MHz的三階Σ-Δ頻率合成器相位噪聲。

由此可見,環路帶寬越小,由Σ-Δ量化引起的相位噪聲越低。

2相位噪聲優化

通過1.2.1分析,高階Σ-Δ量化器可以將量化噪聲推到高頻,使得帶內量化噪聲降低,頻率合成器輸出相位噪聲也降低。

由一階調制器構成的MASH高階Σ-Δ量化器,無條件穩定,但是MASHΣ-Δ量化器存在的問題是它的輸出是多位,頻率合成器之分頻器設計復雜,且分頻比會在多模之間切換,會給鑒相器的輸出引入高頻抖動。

高階單環路Σ-Δ量化器存在穩定性問題。為使高階單環路Σ-Δ量化器穩定工作,其噪聲傳遞函數增益需滿足[5]:

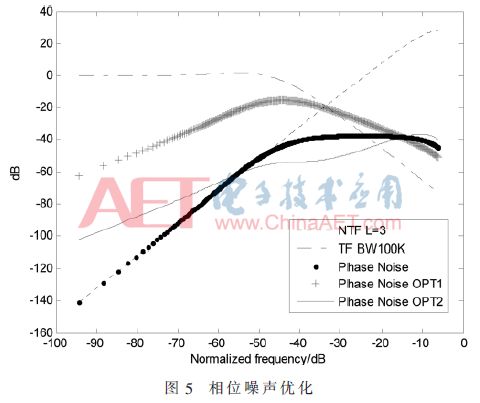

通過高階環路引入前饋通路,改變NTF增益,使其穩定工作。但是帶來的缺點是NTF對量化噪聲的抑制低于理想NTF(z)=(1-z-1)L對量化噪聲的抑制。本文提出,信號在輸入Σ-Δ量化器之前,添加高頻零點,從而使內置二階Σ-Δ量化器的小數分頻頻率合成器獲得可以與高階Σ-Δ頻率合成器相當的相位噪聲指標。相位噪聲優化如圖5所示。

圖5中,曲線“--”為三階Σ-Δ量化器相位噪聲;曲線“.-”相位噪聲傳遞函數;曲線“+”為二階Σ-Δ頻率合成器相位噪聲;曲線“.”為三階Σ-Δ頻率合成器相位噪聲;實線為插入高階零點后的二階Σ-Δ頻率合成器相位噪聲。顯而易見,輸入信號插入高頻零點后,二階Σ-Δ頻率合成器可以獲得高階Σ-Δ量化頻率合成器性能。

另一種優化相位噪聲的方法是降低頻率合成器環路帶寬,如1.2.2分析所示。但是為抑制VCO相位噪聲,需要增加頻率合成器帶寬[6]。設計中需要折中優化,找到最優帶寬。

需要注意的是,Σ-Δ頻率合成器鎖定后,Σ-Δ量化器輸出頻率等于參考時鐘頻率,提高參考時鐘頻率,量化器工作頻率也提高,可以把量化噪聲推到更高頻,進入信號帶內的相位噪聲更低,不需要通過壓低頻率合成器帶寬來降低相位噪聲,使得Σ-Δ頻率合成器帶寬提升。

3雜散

分析Σ-Δ頻率合成器雜散產生機理,從優化Σ-Δ調制器角度,提出雜散抑制措施。

3.1 雜散分析

Σ-Δ頻率合成器由于其反饋支路分頻器分頻比動態切換,反饋信號上升沿時刻為:

此外,Σ-Δ量化器位數不夠,會導致量化器飽和,產生很大的雜散。同時,量化器飽和也會惡化噪聲傳遞函數NTF,高頻量化噪聲會進入信號帶內。

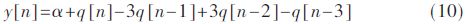

三階Σ-Δ量化器時域表達式為:

歸一化量化噪聲|q[n]|≤0.5,可得|y[n]|≤|a|+4。

至少需要3 bit表示y[n],量化器才不會飽和[7]。

3.2 雜散抑制

優化Σ-Δ量化器設計,抑制雜散。

為抑制Σ-Δ頻率合成器固有雜散,可以在Σ-Δ量化器的輸入信號上迭加一個能量很低的白噪聲[8]。迭加白噪聲后的輸出頻率誤差部分可表達為(y[n]-α+qwhite)×fref。白噪聲的存在使得頻率誤差部分不再固定出現在α×fref與(1-α)×fref及其諧波處的雜散。

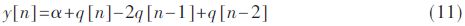

為降低Σ-Δ頻率合成器相位噪聲,需要高階Σ-Δ量化器。由3.1節分析可知,高階Σ-Δ量化器需要量化器位數高,才不至于導致量化器飽和而產生雜散。但是量化器位數高,y[n]取值范圍寬,輸出頻率雜散部分(y[n]-α)×fref會產生更多的諧波,會產生更大的瞬時相位差,要鑒相器具有很高的線性度[9]。從抑制雜散角度看,Σ-Δ量化器階數不宜高。對于二階Σ-Δ量化器,時域表達式為:

歸一化量化噪聲|q[n]|≤0.5,可得|y[n]|≤|a|+2。y[n]可由2 bit表示,量化器才不會飽和。相比于高階Σ-Δ頻率合成器,2階Σ-Δ頻率合成器雜散成分小。

4芯片實現

基于SMIC0.13 μm RF制程,設計了1.575 GHz PLL IP。PLL之小數分頻通過數字二階Σ-Δ量化器的輸出動態切換PLL反饋路徑分頻比實現,滿足GPS時鐘超低相噪/雜散指標,該IP已量產于GPS接收機芯片,可獲得-150 dBm接收靈敏度。

5結論

本文分析研究了Σ-Δ量化器對小數分頻頻率合成器相位噪聲及雜散的影響,并建立小數分頻頻率合成器線性數學模型,通過MATLAB驗證理論分析的可靠性。同時,提出優化Σ-Δ量化器措施,以降低小數分頻頻率合成器相位噪聲與雜散。本文認為,輸入信號預先插入高頻零點,且迭加低能量白噪聲的二階Σ-Δ量化器適合于Σ-Δ頻率合成器。通過提高Σ-Δ駐量化器工作頻率可提升頻率合成器帶寬。

-

頻率合成器

+關注

關注

5文章

224瀏覽量

32582 -

相位噪聲

+關注

關注

2文章

183瀏覽量

23103

原文標題:【學術論文】小數分頻頻率合成器的Σ-Δ調制分析及優化

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

詳解頻率合成器高性能架構的實現

ADF4158-直接調制波形產生6.1 GHz小數N分頻頻率合成器

評論