3D封裝與系統級封裝概述

一、引言:先進封裝技術的演進背景

隨著摩爾定律逐漸逼近物理極限,半導體行業開始從單純依賴制程微縮轉向封裝技術創新。3D封裝和系統級封裝(SiP)作為突破傳統2D平面集成限制的核心技術,正在重塑電子系統的集成范式。3D封裝通過垂直堆疊實現超高的空間利用率,而SiP則專注于多功能異質集成,兩者共同推動著高性能計算、人工智能和物聯網等領域的技術革新。

根據Mordor Intelligence報告,全球2.5D/3D封裝市場規模已從2023年的86.6億美元增長至2029年的216.3億美元,年復合增長率達17.2%。這種爆發式增長源于三大技術驅動力:HBM存儲器需求激增、AI芯片對帶寬的渴求,以及移動設備對微型化的極致追求。

二、3D封裝技術體系解析

2.1 技術原理與核心要素

3D封裝的核心在于垂直互連架構的實現,其技術突破點體現在三個維度:

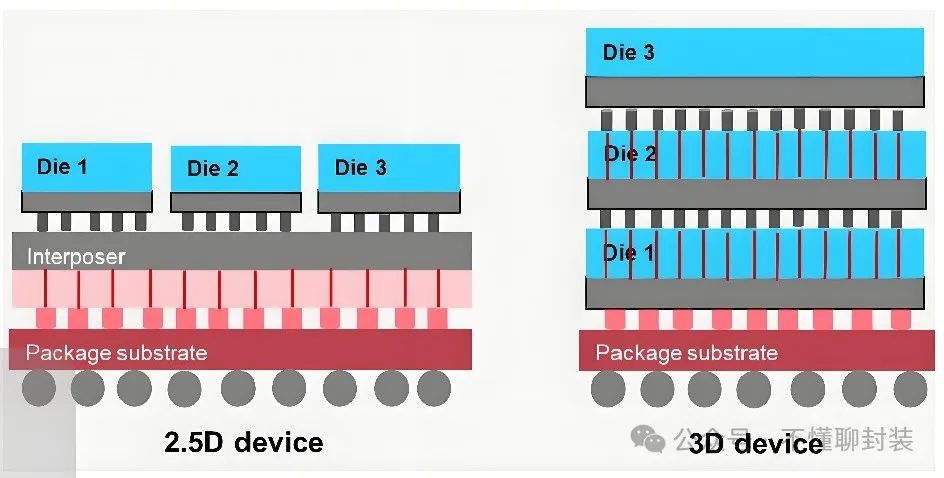

硅通孔(TSV)技術:在芯片內部制作直徑5-50μm的垂直導電通道,實現層間直接電氣連接。英特爾的Foveros技術采用10μm級TSV,使互連密度達到傳統鍵合的100倍。

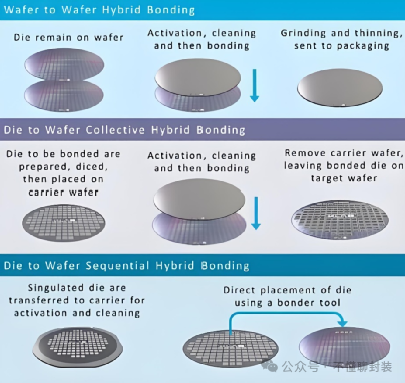

混合鍵合(Hybrid Bonding):通過銅-銅直接鍵合實現1μm以下間距互連,臺積電的SoIC技術已將此工藝良率提升至99.4%,顯著降低RC延遲。

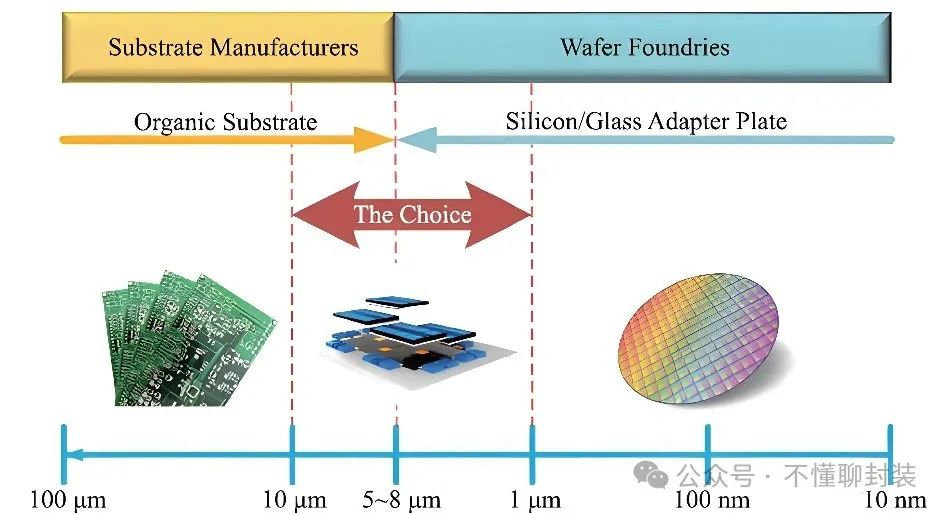

轉接板:從硅基轉接板(如CoWoS的1700mm2超大尺寸)到玻璃基板(TGV),材料選擇直接影響信號完整性和熱膨脹匹配。

2.2 典型實現方案對比

2.3關鍵技術挑戰

熱管理:堆疊結構導致熱流密度激增,AMD的3D V-Cache采用非對稱布局將熱點溫度控制在85℃以下。

機械應力:TSV引起的局部應力可達200MPa,需通過應力緩沖層和環形柵結構補償。

測試策略:采用IEEE 1838標準構建邊界掃描鏈,實現95%以上的堆疊前芯片篩選率。

三、系統級封裝(SiP)的技術演進

3.1 技術定義與架構創新

SiP通過三維異質集成將處理器、存儲器、傳感器等不同制程/材料的元件整合于單一封裝。高通的Snapdragon 8 Gen1將8核CPU、GPU、5G基帶等10+芯片集成,封裝體積縮減30%的同時功耗降低22%。

關鍵技術突破點:

1.埋置式結構:將無源器件嵌入有機基板,村田的0402尺寸電感集成度提升5倍。

2.扇出型封裝:臺積電InFO技術實現4μm RDL線寬,支持5000+ I/O的處理器封裝。

3.柔性互連:應用液態金屬互連技術,彎曲半徑可達3mm仍保持10^8次循環可靠性

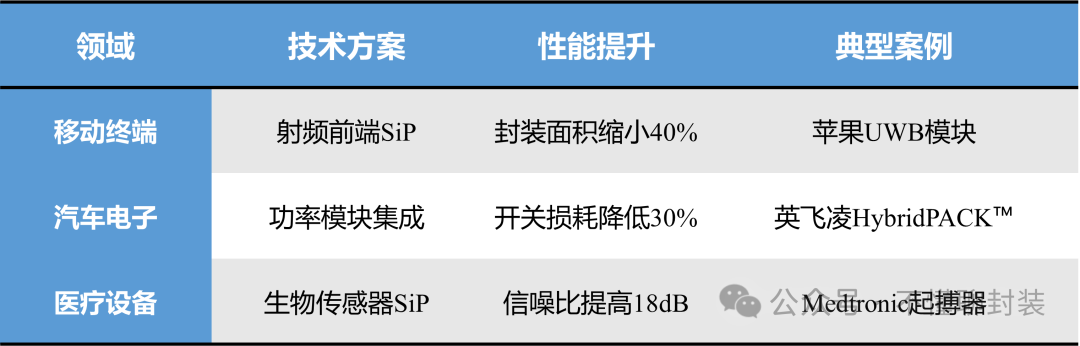

3.2 典型應用場景分析

結語

從3D封裝帶來的垂直革命到SiP實現的系統級創新,先進封裝技術正在書寫半導體行業的第二增長曲線。隨著混合鍵合、光子集成等技術的成熟,封裝已從單純的保護功能進化為決定系統性能的核心要素。未來十年,3D/SiP技術將與AI、量子計算等前沿領域深度耦合,推動電子系統向更高維度演進,最終實現"封裝即芯片"的產業新范式。

-

系統級封裝

+關注

關注

0文章

37瀏覽量

9206 -

3D封裝

+關注

關注

7文章

139瀏覽量

27578

原文標題:3D封裝與系統級封裝概述

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論