項目場景:

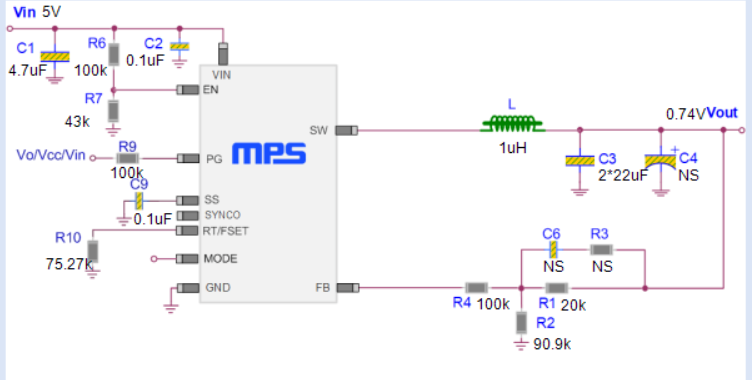

二級BUCK電源電路,DCDC芯片輸入5V,輸出0.74V,開關頻率2.1MHz。工作在FCCM模式。

如下圖1所示:

問題描述

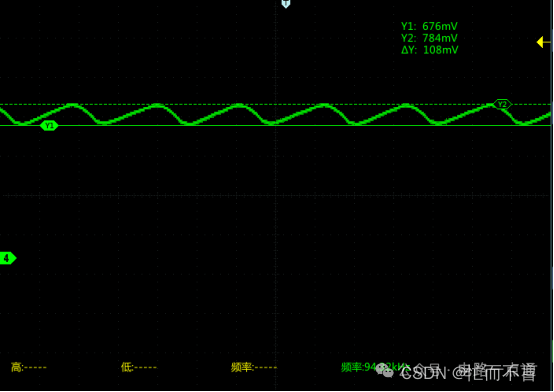

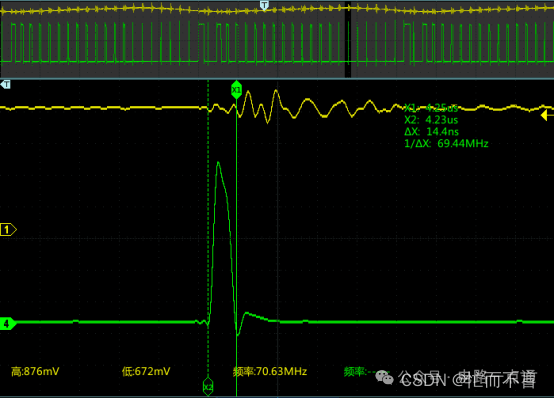

1、測試發現輸出電壓紋波超過100mV,紋波頻率約94kHz。不滿足后級芯片對紋波噪聲的要求。如下圖

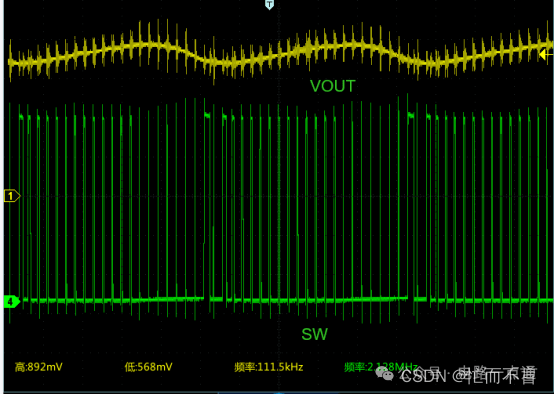

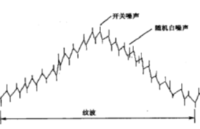

2、如下圖,同時測量SW管腳信號和輸出信號。其中綠色是DCDC的SW管腳信號,黃色是輸出電壓(上面的毛刺脈沖是探頭串擾,實際波形見上圖1) 。可以看出SW信號的脈沖寬度是一直在變化的,從而也導致輸出電壓不斷變化,變化趨勢與SW的變化對應。

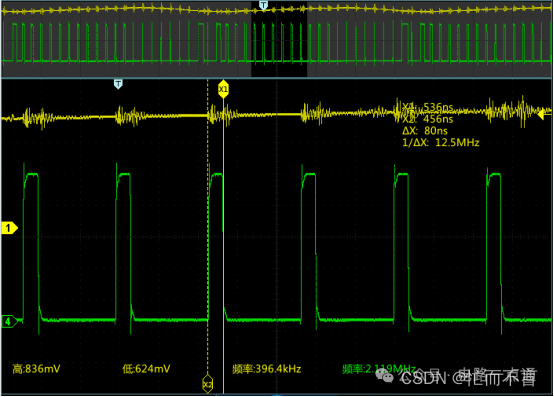

如下圖3,輸出電壓最低點開始,脈沖寬度持續10來個周期一直在80ns左右

3、輸出電壓達到最高點后,輸出脈沖寬度變成14ns左右的尖峰脈沖。然后導致輸出電壓開始下降。

原因分析:

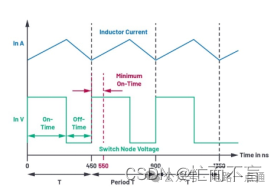

SW脈沖寬度變化的原因與DCDC的最小導通時間有關。理論計算SW信號的高電平脈沖寬度約等于0.74V/(5V*2.1MHz)=69ns。DCDC手冊上要求Minimum on time 時間Typ值為50ns,沒有給出Minimum on time的最大最小值。與DCDC芯片廠家確認,這個最大值大概在75ns~80ns。與上面實際測試結果中的80ns相符。

![]()

由于實際要求的導通時間是69ns,而DCDC高側MOS至少要打開80ns(Minimum on time),幾個周期后就會把輸出沖高,但是FB比較器反饋的結果又需要關閉Switch,從而讓輸出變低,相當于引入了一個干擾源。從而導致了大的輸出波紋。

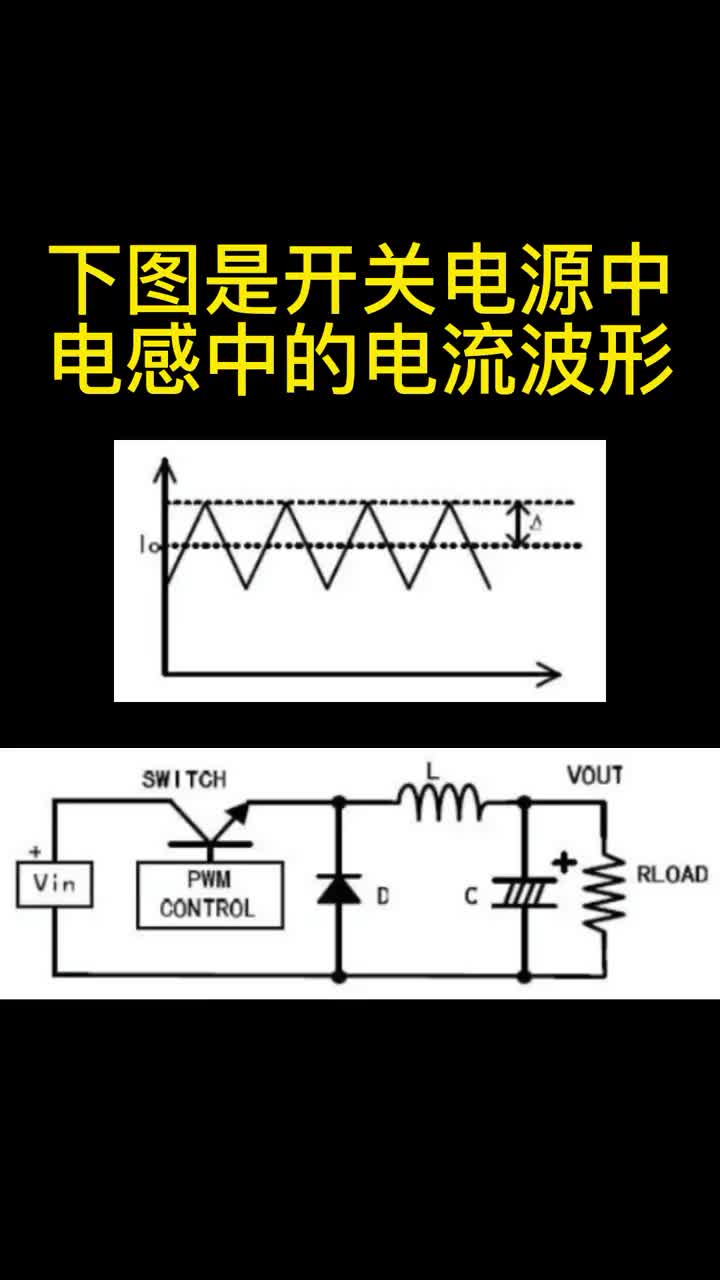

什么是最小導通時間,為什么需要有最小導通時間? 在許多開關模式電源轉換器中,電感電流是在導通時間內測量的。此電流用于過流保護,并用于根據電流閉環控制原理(電流模式控制)工作的穩壓器中,環路調節也需要測量電感電流。在開關瞬變后,必須先降開關過程中產生的噪音才能進行準確的電流測量。這需要一些時間,也稱為消隱時間。而這段時間內內置的電流限制比較器也不會工作,高側MOS的Gate輸出驅動也就不會被關斷。

解決方案:

根據上述的分析結論,做了一些驗證:

1、提高輸出電壓,增大高電平占空比---輸出電壓紋波消失

2、降低輸入電壓,增大高電平占空比---輸出電壓紋波消失

3、降低開關頻率------輸出電壓紋波消失

上述驗證結果證實了前面的分析結論。但由于輸入電壓和輸出電壓都不能改變,所以最終選擇降低開關頻率。

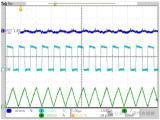

開關頻率由2.1M變成1.38M,SW脈沖寬度理論值為:0.75V/(5V*1.38MHz)=108ns,大于Minimum on time要求的最大值80ns。

總結:DCDC電源電路設計的時候需要考慮電源IC的最小導通時間(Minimum on time或者稱為消隱時間),而且要保證實際需要的導通時間大于Minimum on time的最大值,如果芯片中沒有體現最大值要求,需要找廠家確認清楚。否則電源輸出會有問題。

-

DC-DC電源

+關注

關注

2文章

64瀏覽量

17935 -

輸出紋波

+關注

關注

0文章

30瀏覽量

6162

原文標題:DC-DC電源電路最小導通時間不足引起輸出紋波過大問題分析

文章出處:【微信號:zfdzszy,微信公眾號:張飛電子實戰營】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DC-DC Boost電路外圍元器件如何選擇?

DC-DC電源轉換,是否夠進一步優化降低紋波?

DC-DC電源設計分析及使用注意

簡述DC-DC開關電源小型化發展中的不足

DC-DC電源輸出紋波測量的方法

評論