1.1 課程介紹

這一章開(kāi)始主要介紹 XILINX FPGA PICE IP XDMA IP的使用。XDMA IP使用部分教程分LINUX 篇和WINDOWS篇兩個(gè)部分。通過(guò)實(shí)戰(zhàn),面向應(yīng)用,提供給大家 XILINX FPGA PCIE 應(yīng)用解決方案。

本教程以MZ7035FA作為樣機(jī)測(cè)試。在正式開(kāi)始教程內(nèi)容前,有必要把MZ7035FA開(kāi)發(fā)板的特點(diǎn)說(shuō)明下。這是一款高性價(jià)比的FPGA開(kāi)發(fā)板。帶PCIE接口,SFP光通信接口,3路千兆以太網(wǎng)口,2路SATA接口,1路HDMI輸出,1路串口,1路TF卡接口。支持MSXBO(米聯(lián)客)FEP標(biāo)準(zhǔn)擴(kuò)展接口。采用的CPU型號(hào)為XC7Z035-FFG676。PL端搭載32bit 1024MB DDR3內(nèi)存,PS端搭載32bit 1024MB DDR3內(nèi)存,F(xiàn)PGA讀寫(xiě)DDR支持的最大數(shù)據(jù)時(shí)鐘為1600M,可以進(jìn)行很多復(fù)雜的開(kāi)發(fā)任務(wù)。

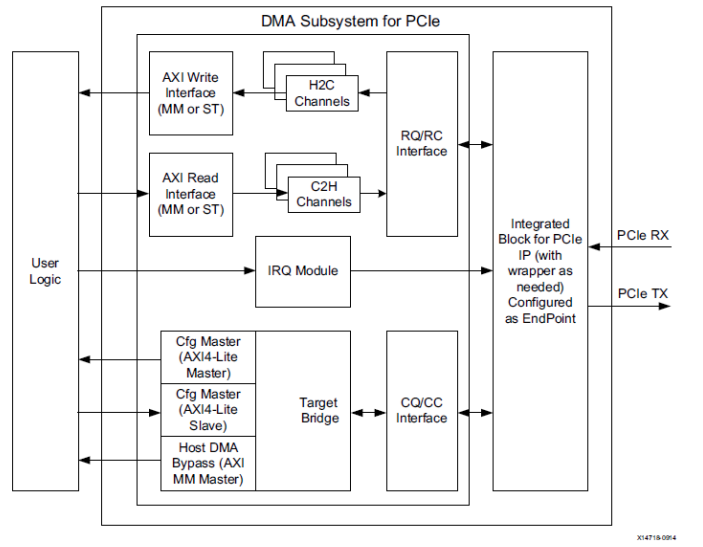

1.2 XDMA 概述

Xilinx 提供的DMASubsystem for PCIExpressIP是一個(gè)高性能,可配置的適用于PCIE2.0,PCIE3.0 的SG 模式 DMA,提供用戶可選擇的 AXI4 接口或者 AXI4-Stream接口。一般情況下配置成 AXI4 接口可以加入到系統(tǒng)總線互聯(lián),適用于大數(shù)據(jù)量異步傳輸,通常情況都會(huì)使用到 DDR,AXI4-Stream 接口適用于低延遲數(shù)據(jù)流傳輸。

XDMA 是SGDMA,并非Block DMA,SG 模式下,主機(jī)會(huì)把要傳輸?shù)臄?shù)據(jù)組成鏈表的形式,然后將鏈表首地址通過(guò)BAR 傳送給XDMA,XDMA 會(huì)根據(jù)鏈表結(jié)構(gòu)首地址依次完成鏈表所指定的傳輸任務(wù)。

1.3 XDMA 提供如下接口:

AXI4、AXI4-Stream,必須選擇其中一個(gè),用來(lái)數(shù)據(jù)傳輸

AXI4-Lite Master,可選,用來(lái)實(shí)現(xiàn)PCIE BAR 地址到AXI4-Lite 寄存器地址的映射,可用來(lái)讀寫(xiě)用戶邏輯寄

存器

AXI4-Lite Slave,可選,用來(lái)將XDMA 內(nèi)部寄存器開(kāi)放給用戶邏輯,用戶邏輯可以通過(guò)此接口訪問(wèn)XDMA

內(nèi)部寄存器,不會(huì)映射到BAR

AXI4 Bypass 接口,可選,用來(lái)實(shí)現(xiàn)PCIE 直通用戶邏輯訪問(wèn),可用于低延遲數(shù)據(jù)傳輸

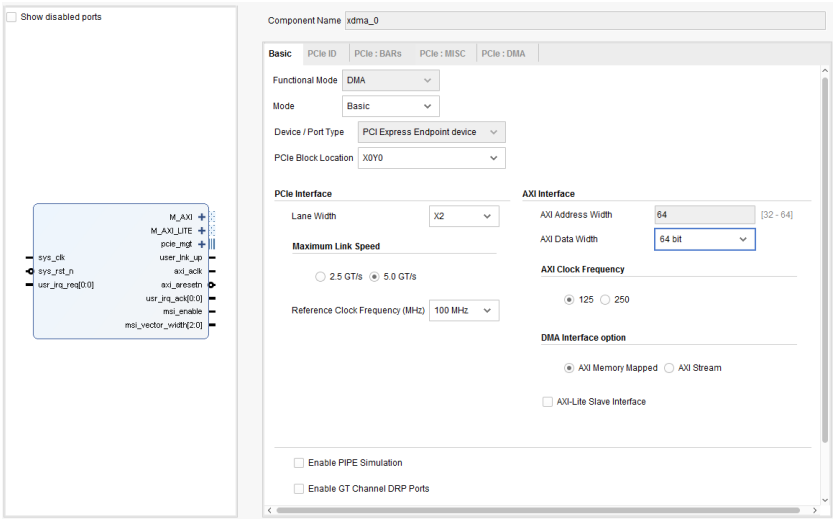

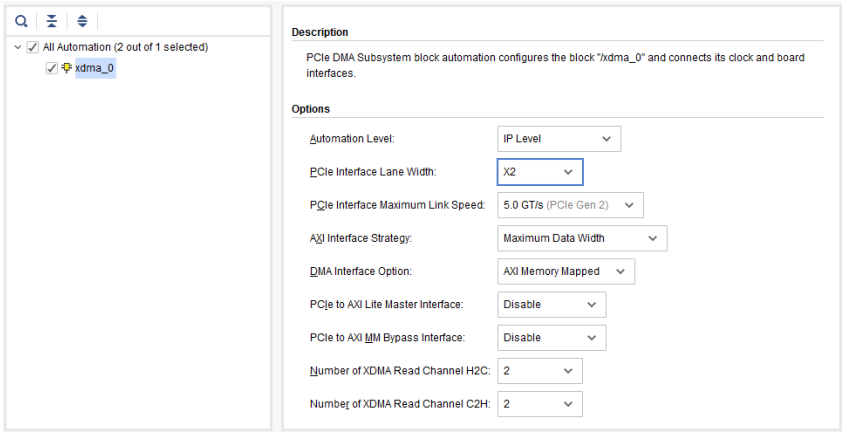

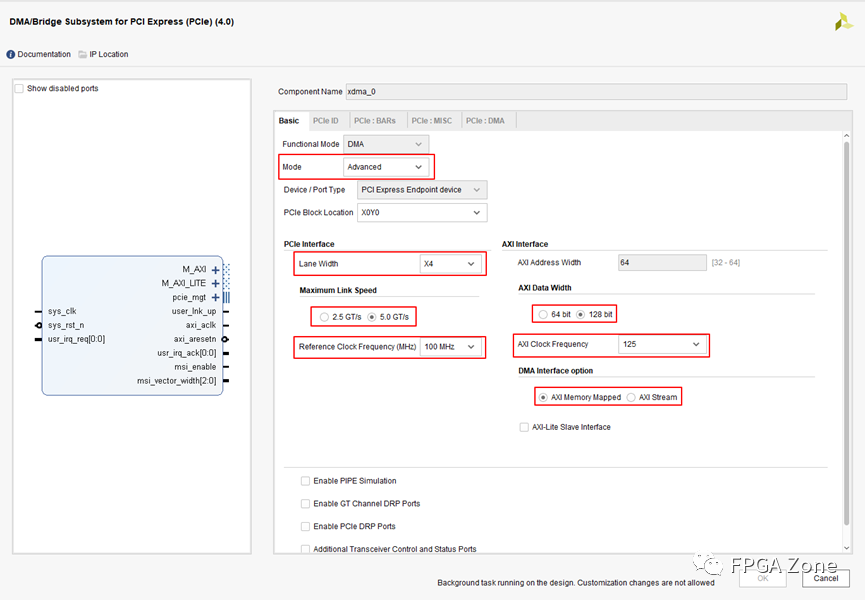

1.4 XDMA IP 配置

Mode:配置模式,選擇 Advanced 高級(jí)配置

Lane Width:MZ7035 支持X4

Max Link Speed:選擇5.0GT/s 即PCIE2.0

Reference Clock :100MHZ,參考時(shí)鐘 100M

DMA Interface Option:接口選擇 AXI4 接口

AXI Data Width:128bit,即 AXI4 數(shù)據(jù)總線寬度為128bit

AXI Clock :125M,即AXI4 接口時(shí)鐘為 125MHZ

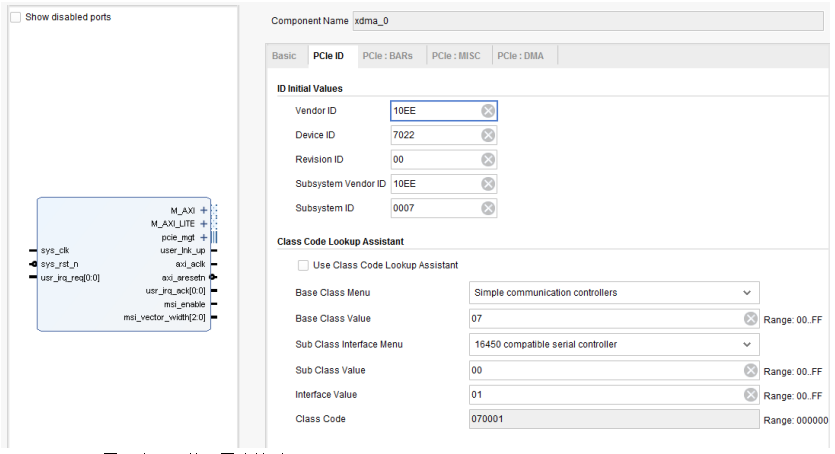

PCIE ID 配置

我們配置成Memory controller 讓IP 自動(dòng)選擇VID 等

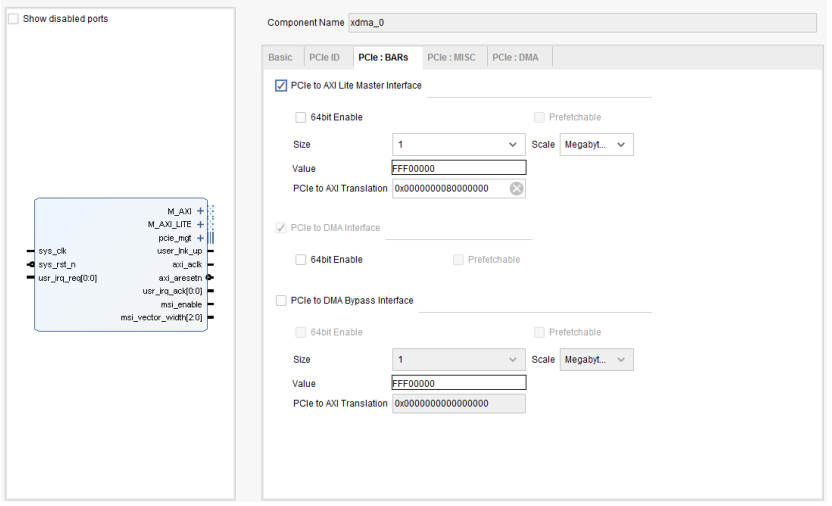

PCIE BAR 配置,這里面的配置比較重要

首先使能PCIE to AXI Lite Master Interface ,這樣可以在主機(jī)一側(cè)通過(guò)PCIE 來(lái)訪問(wèn)用戶邏輯側(cè)寄存器或者其他AXI4-Lite 總線設(shè)備

映射空間選擇 1M,當(dāng)然用戶也可以根據(jù)實(shí)際需要來(lái)自定義大小。

PCIE to AXI Translation:這個(gè)設(shè)置比較重要,通常情況下,主機(jī)側(cè)PCIE BAR 地址與用戶邏輯側(cè)地址是不一樣的,這個(gè)設(shè)置就是進(jìn)行BAR 地址到AXI 地址的轉(zhuǎn)換,比如主機(jī)一側(cè) BAR 地址為0,IP 里面轉(zhuǎn)換設(shè)置為0x80000000,則主機(jī)訪問(wèn) BAR 地址0 轉(zhuǎn)換到AXI LIte 總線地址就是0x80000000

PCIE to DMA Interface :選擇64bit 使能

DMA Bypass 暫時(shí)不用

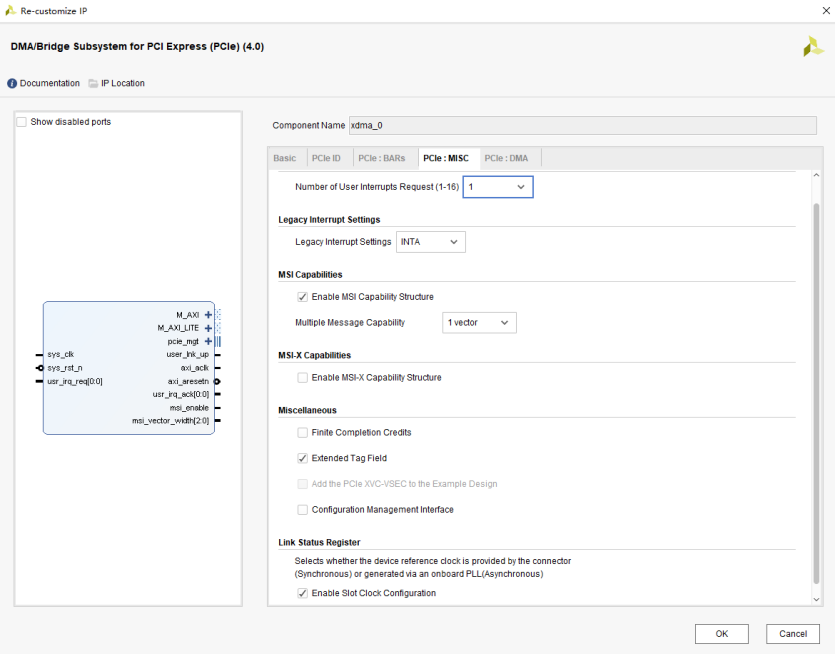

PCIE 中斷設(shè)置

User Interrupts:用戶中斷,XDMA 提供16 條中斷線給用戶邏輯,這里面可以配置使用幾條中斷線。

Legacy Interrupt:XDMA 支持 Legacy 中斷

選擇MSI 中斷

注意:MSI 中斷和 MSI-X 中斷只能選擇一個(gè),否則會(huì)報(bào)錯(cuò),如果選擇了 MSI 中斷,則可以選擇 Legacy 中斷,如果選擇了 MSI-X 中斷,那么 MSI 必須取消選擇,同時(shí)Legacy 也必須選擇None。此 IP 對(duì)于7 系列設(shè)置有這么個(gè)問(wèn)題,如果使用Ultrascale 系列,則可以全部選擇

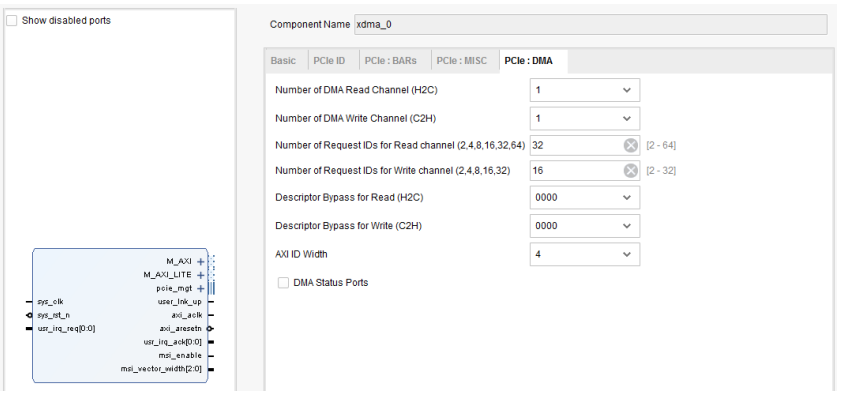

配置DMA 相關(guān)內(nèi)容

Number of DMA Read Channel(H2C)和Number of DMA Write Channel(C2H)通道數(shù),對(duì)于PCIE2.0 來(lái)說(shuō)最大只能選擇 2,也就是 XDMA 可以提供最多兩個(gè)獨(dú)立的寫(xiě)通道和兩個(gè)獨(dú)立的讀通道,獨(dú)立的通道對(duì)于實(shí)際應(yīng)用中有很大的作用,在帶寬允許的前提前,一個(gè)PCIE 可以實(shí)現(xiàn)多種不同的傳輸功能,并且互不影響。這里我們選擇1

Number of Request IDs for Read (Write)channel :這個(gè)是每個(gè)通道設(shè)置允許最大的 outstanding 數(shù)量,按照默認(rèn)即可

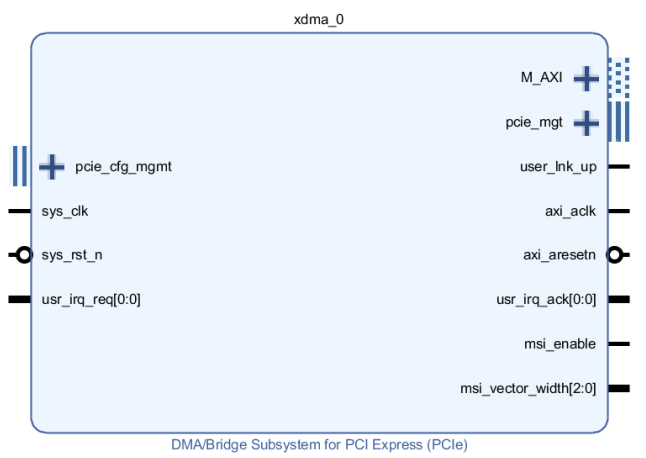

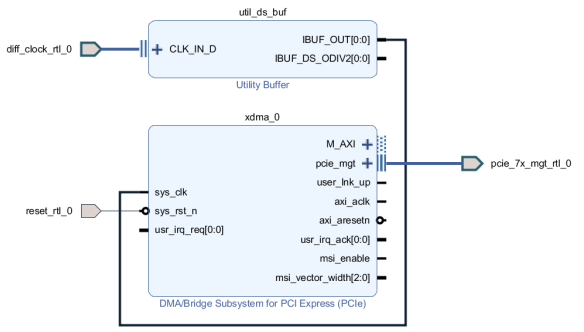

配置完成以后,點(diǎn)擊Run Block Auto,可以看到之前的配置信息,如果有發(fā)現(xiàn)和目標(biāo)配置不一樣的,需要手動(dòng)修改,點(diǎn)擊OK,完成配置

配置完成以后,VIVADO 會(huì)自動(dòng)進(jìn)行必要的連接

到此為止,XDMA IP 配置就完成了只要再進(jìn)行時(shí)鐘和 GTP 約束即可。

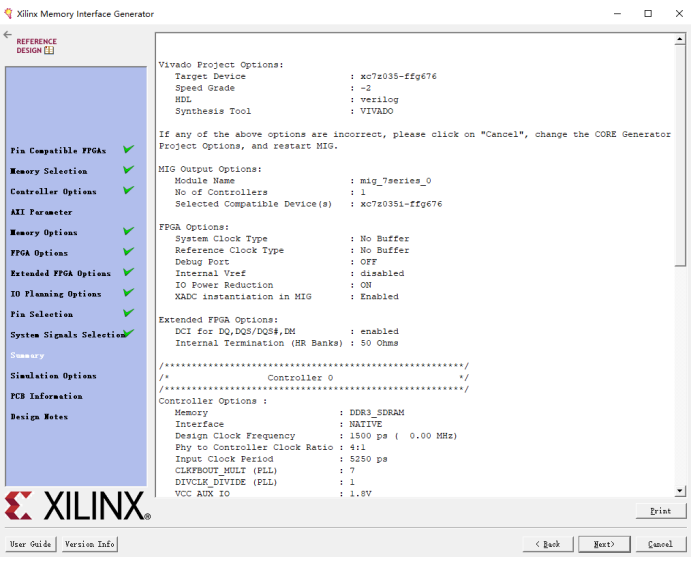

1.5 MIG 7 SERIES 的配置

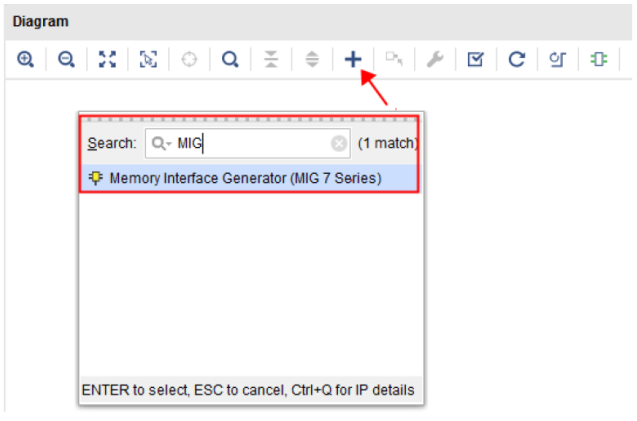

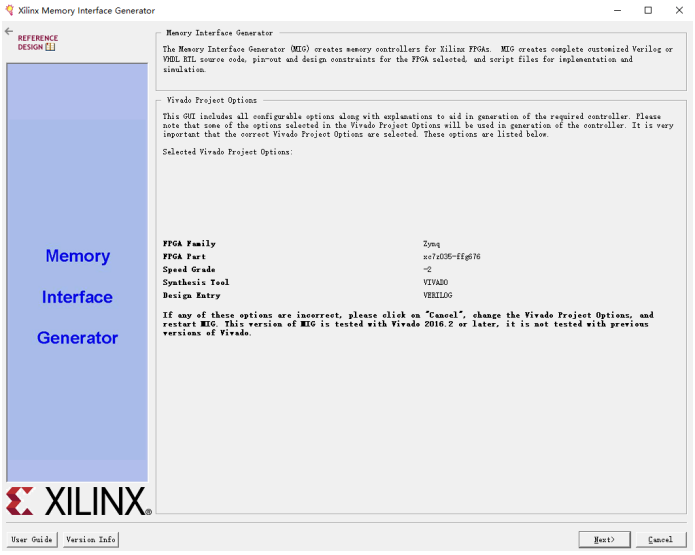

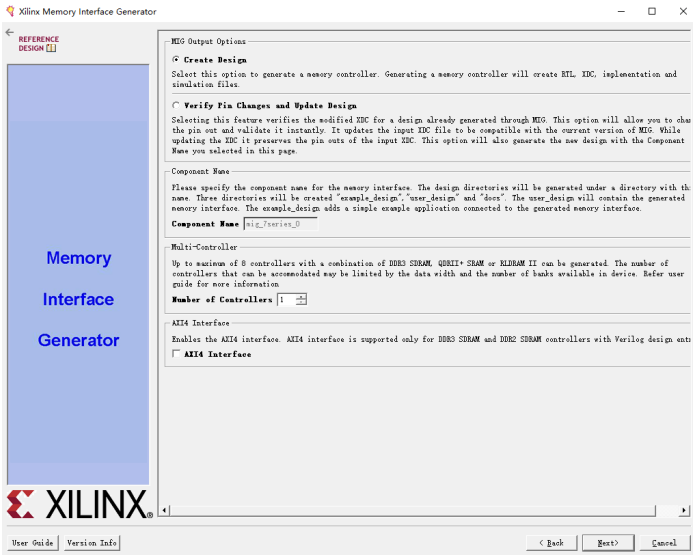

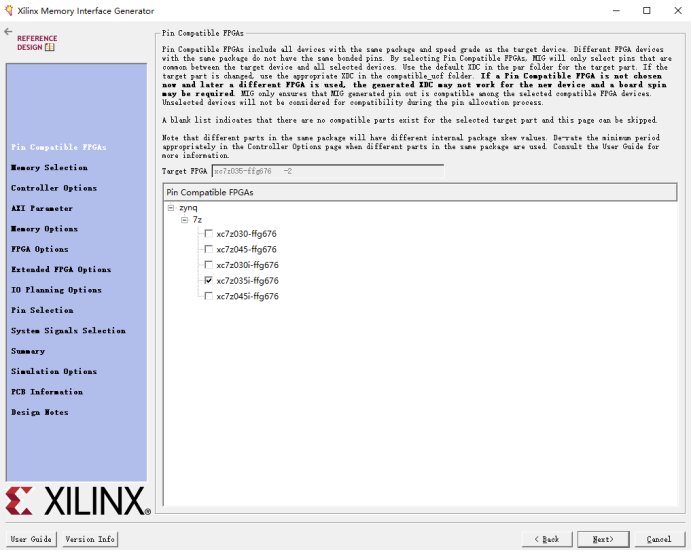

Step1:任單擊 IP Catalog,選取 Memory Interface Generator(MIG 7 series)IP 添加到 Block design。雙擊 MIG 7 SERIES ,對(duì)這個(gè) IP 進(jìn)行配置。

雙擊生成的IP核

單擊NEXT

繼續(xù)單擊NEXT

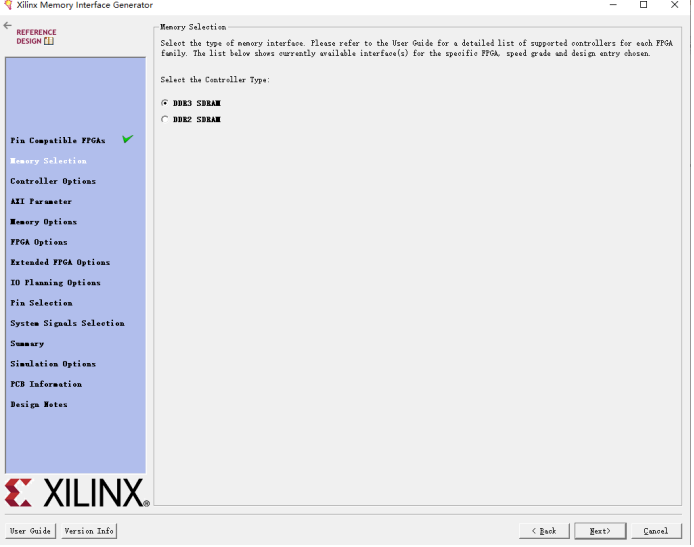

選擇DDR3 單擊NEXT

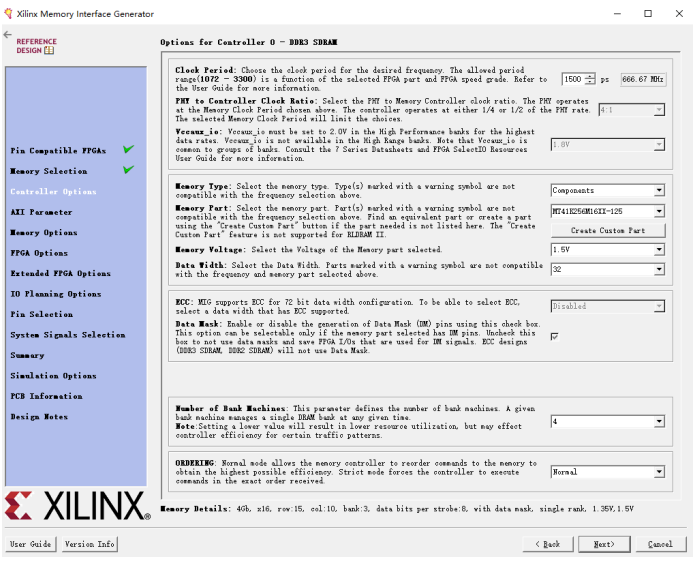

設(shè)置MIG 內(nèi)核時(shí)鐘頻率為、內(nèi)存型號(hào)、內(nèi)存的數(shù)據(jù)位寬

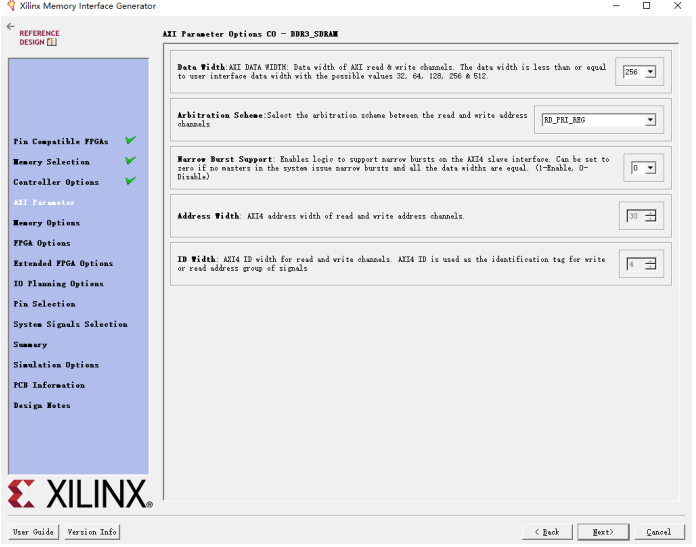

設(shè)置MIG AXI4 最大支持的位寬,對(duì)于2片DDR 最大位寬為256bit

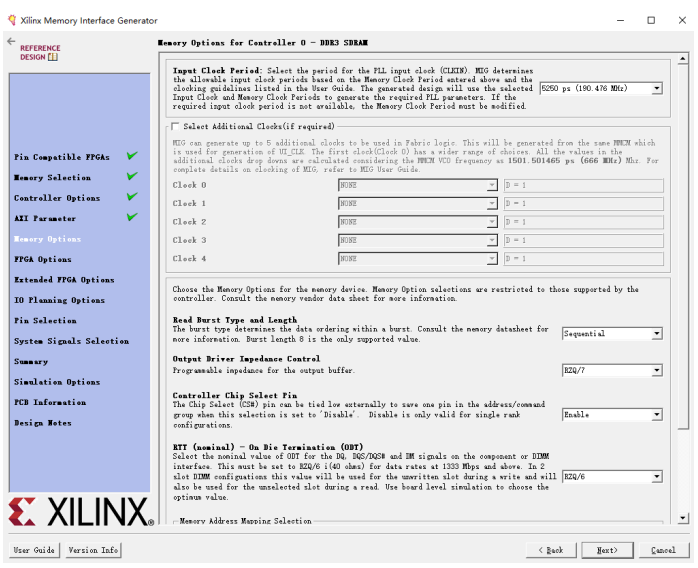

設(shè)置輸入頻率

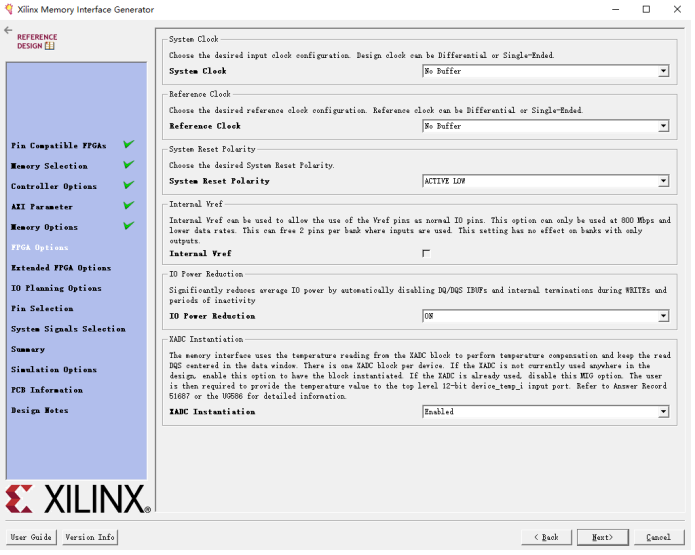

系統(tǒng)和參考時(shí)鐘時(shí)鐘選擇no buffer,MIG低電平復(fù)位

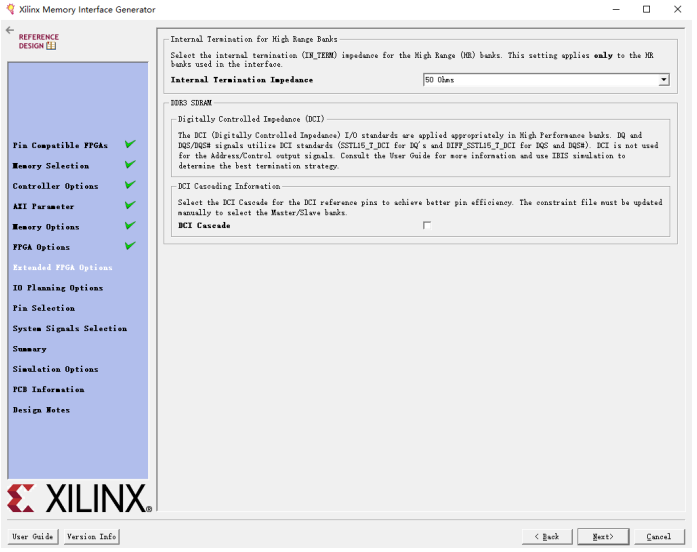

Step9:終端阻抗選擇50hms,設(shè)置DCI

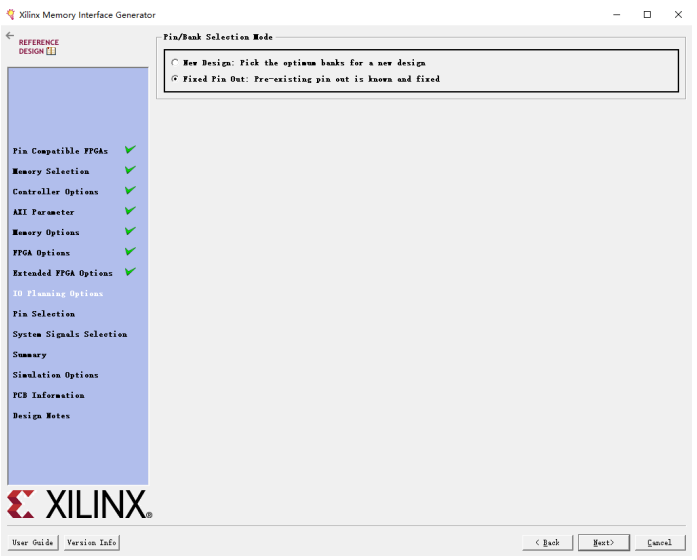

選擇Fixed Pin Out

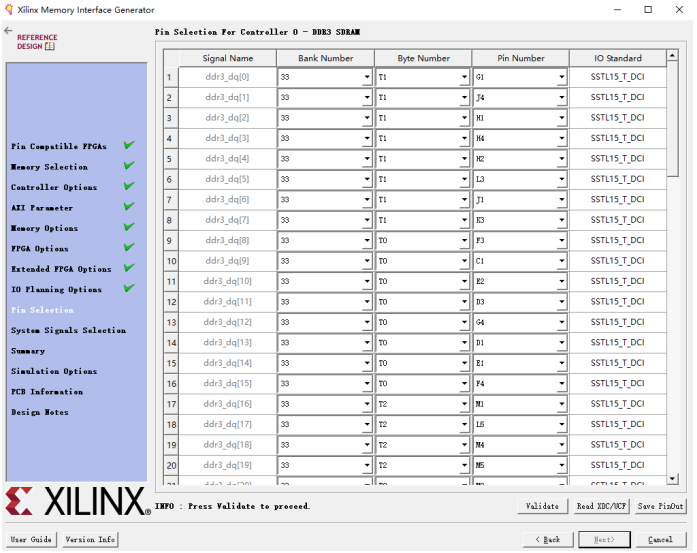

根據(jù)原理圖手動(dòng)填寫(xiě)PIN 腳定義,或者選擇Read XDC/UCF直接讀入pin腳定義,本課程下提供了MZ7035.ucf 的DDR 配置文件,直接讀入既可。

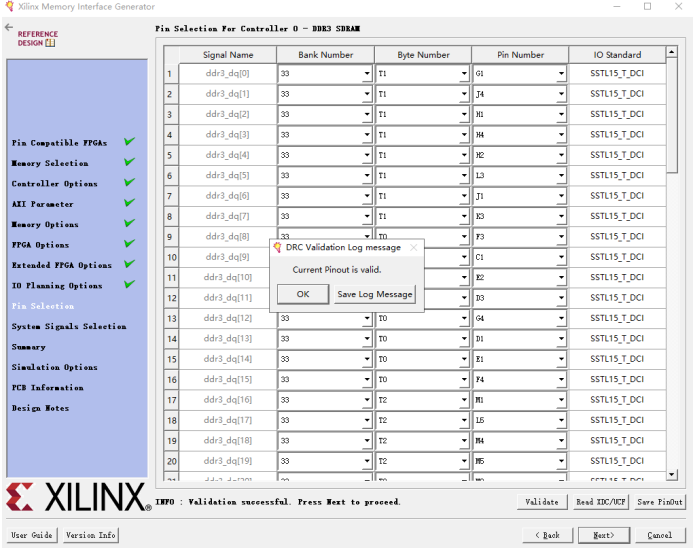

填寫(xiě)完成后,先單擊Validate再單擊NEXT

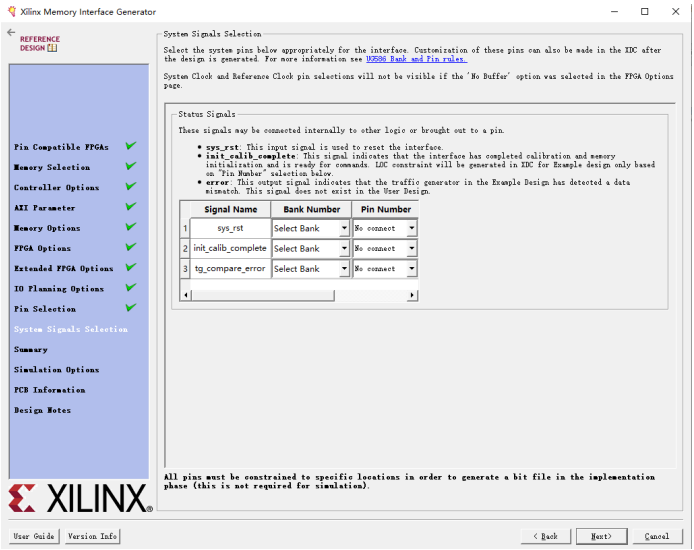

繼續(xù)單擊NEXT

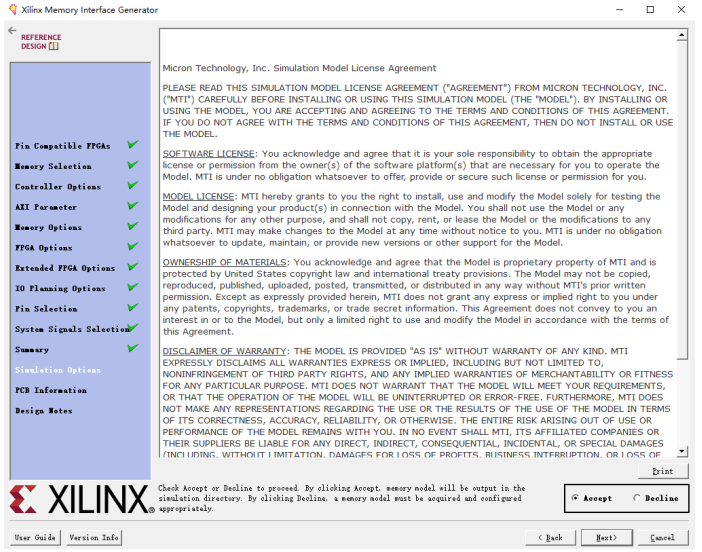

繼續(xù)單擊NEXT

繼續(xù)單擊NEXT

繼續(xù)單擊NEXT

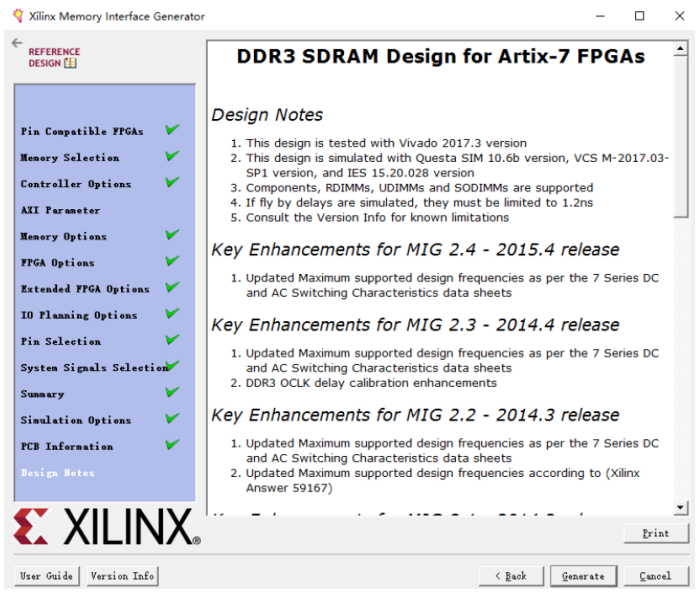

最后單擊Generate,至此MIG的配置完成

1.6基礎(chǔ)測(cè)試系統(tǒng)搭建

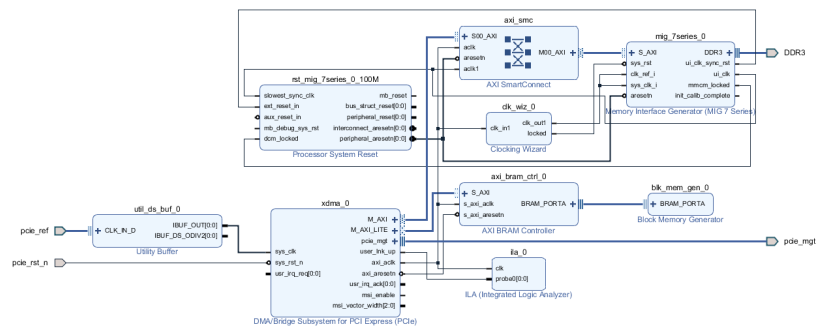

我們的測(cè)試目標(biāo)是進(jìn)行PCIE AXI4總線與外設(shè)進(jìn)行讀寫(xiě)操作,PCIE AXI4-Lite 總線進(jìn)行用戶邏輯寄存器或者其他 AXI4-Lite 總線設(shè)備訪問(wèn)操作。AXI4總線上掛載到MIG控制器DDR上去,實(shí)現(xiàn)對(duì)DDR的讀寫(xiě)控制。

為此搭建系統(tǒng)為下圖所示:

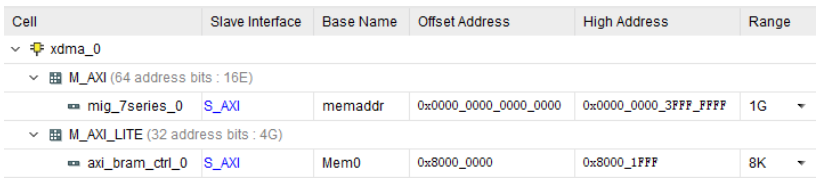

進(jìn)行地址分配:

這里我們把掛在M_AXI上的DDR地址分配從0開(kāi)始(對(duì)于widnows系統(tǒng)必須為0), M_AXI是需要進(jìn)行DMA操作的。而M_AXI_LITE掛載的BRAM是需要進(jìn)行BAR空間操作,所以地址設(shè)置為0x80000000和XMDA IP里面設(shè)置的地址對(duì)應(yīng)。

1.7LINUX下驅(qū)動(dòng)程序編譯安裝測(cè)試1.7.1 驅(qū)動(dòng)編譯和安裝(下必須重新編譯)

官方驅(qū)動(dòng)包選擇 2017 版本以后的,注意 2016 版本的有 BUG!!!

在終端進(jìn)入到xdma 目錄,輸入make ,進(jìn)行驅(qū)動(dòng)編譯

執(zhí)行以下指令:

- Change directory to the driver directory.

cd driver

- Compile the kernel module driver.

make

- Change directory to the tests directory.

cd tests

- Compile the provided example software.

make

- Copy the provided driver rules from the etc directory to the

/etc/ directory on your system.

cp ../etc/udev/rules.d/* /etc/udev/rules.d/

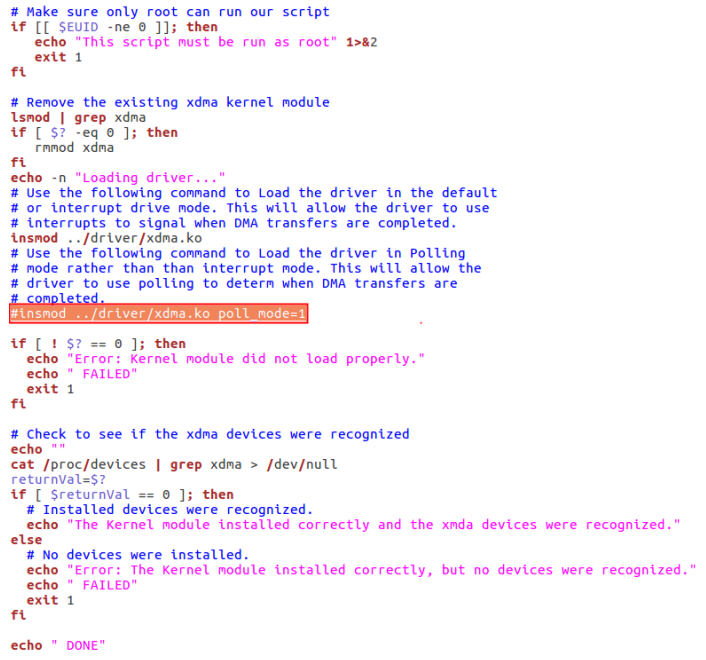

關(guān)于驅(qū)動(dòng)加載,這里有兩點(diǎn)要說(shuō)明一下,首先是在驅(qū)動(dòng)加載之前,如果檢測(cè)到系統(tǒng)中已經(jīng)加載過(guò)驅(qū)動(dòng),那么它會(huì)將已經(jīng)加載的驅(qū)動(dòng)卸載,然后再加載。然后就是PCIe DMA的工作方式可以通過(guò)加載驅(qū)動(dòng)傳輸參數(shù)進(jìn)行修改。默認(rèn)情況下DMA工作在中斷模式,可以通過(guò)修改load_driver.sh腳本改為輪循模式如下圖所示,但是可能驅(qū)動(dòng)有問(wèn)題,實(shí)際測(cè)試輪詢模式有些程序無(wú)法正常執(zhí)行,所以建議大家不要使用輪詢模式。

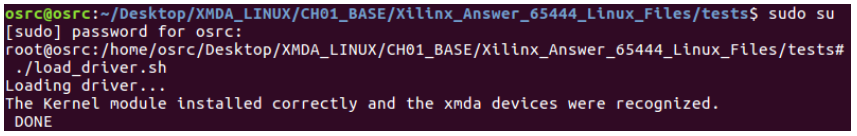

在準(zhǔn)備加載驅(qū)動(dòng)前,確保你的開(kāi)發(fā)板已經(jīng)下載PCIE工程的bit文件,而且已經(jīng)重啟過(guò)電腦。好了,現(xiàn)在加載驅(qū)動(dòng)。

./load_driver.sh

如下顯示驅(qū)動(dòng)安裝成功

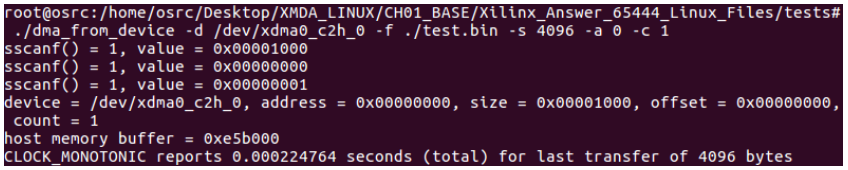

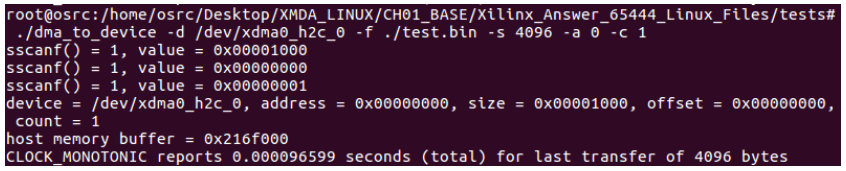

在終端執(zhí)行命令:

./dma_from_device -d /dev/xdma0_c2h_0 -f ./test.bin-s 4096-a 0 -c 1

./dma_to_device -d /dev/xdma0_h2c_0 -f ./test.bin-s 4096-a0-c 1

-d:device 設(shè)備.

-f:file 文件

-s:size 大小

-a:addr 起始地址

-c:count

這兩個(gè)操作分別是從板卡讀 4096 Bytes 數(shù)據(jù)到文件 test.bin 以及從 test.bin 讀出4096 Bytes 數(shù)據(jù)發(fā)送給板卡。

原文鏈接;

https://openatomworkshop.csdn.net/674532733a01316874d81597.html

-

PCIe

+關(guān)注

關(guān)注

15文章

1244瀏覽量

82863 -

環(huán)路測(cè)試

+關(guān)注

關(guān)注

0文章

9瀏覽量

5923

原文標(biāo)題:PCIE XDMA 開(kāi)發(fā)環(huán)境搭建以及環(huán)路測(cè)試

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】+02.PCIE接口測(cè)試(zmj)

ZYNQ調(diào)用XDMA PCIE IP同時(shí)讀寫(xiě)PS DDR,導(dǎo)致藍(lán)屏問(wèn)題。

本地測(cè)試環(huán)境搭建

測(cè)試環(huán)境的搭建和維護(hù)_軟硬件測(cè)試環(huán)境

搭建測(cè)試環(huán)境常用linux命令_linux下web測(cè)試環(huán)境的搭建

arm的開(kāi)發(fā)環(huán)境有哪些_使用Eclipse搭建ARM架構(gòu)MCU開(kāi)發(fā)環(huán)境

如何搭建鴻蒙開(kāi)發(fā)環(huán)境

XDMA/PCIE IP的定制和Block Design的搭建

高頻探針如何搭建測(cè)試環(huán)境及下針

基于FPGA的PCIE通信測(cè)試

PCIE XDMA開(kāi)發(fā)環(huán)境搭建以及環(huán)路測(cè)試

PCIE XDMA開(kāi)發(fā)環(huán)境搭建以及環(huán)路測(cè)試

評(píng)論