一 傅里葉變換FFT

想必大家對傅里葉老人家都不陌生了,網上也有這方面的很多資料。通過FFT將時域信號轉換到頻域,從而對一些在時域上難以分析的信號在頻域上進行處理。在這里,我們需要注意采樣頻率、FFT采樣點數這兩個參數:

根據奈奎斯特采樣定理,采樣頻率需大于信號頻率的兩倍;

FFT采樣點數,代表對信號在頻域的采樣數;

采樣頻率Fs和采樣點數N決定了信號的頻域分辨力,即分辨力=Fs/N,即N越大,頻域分辨力越好,反之頻域分辨力越差。

二 Xilinx FFT v9.0

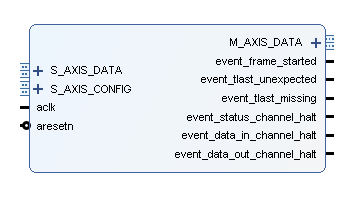

1.輸入輸出端口

如上圖所示,左側的端口均為輸入端口,右側端口均為輸出端口,其中,S_AXIS_DATA為輸入數據端口,我們要進行FFT的數據需要通過這根線輸入給IP核;S_AXIS_CONFIG為輸入配置端口,這個信號包含了對數據進行FFT還是IFFT、縮放因子、FFT變換點數等信息;FFT變換后的數據從M_AXIS_DATA端口輸出。這些端口的具體功能可以參見pg109手冊。

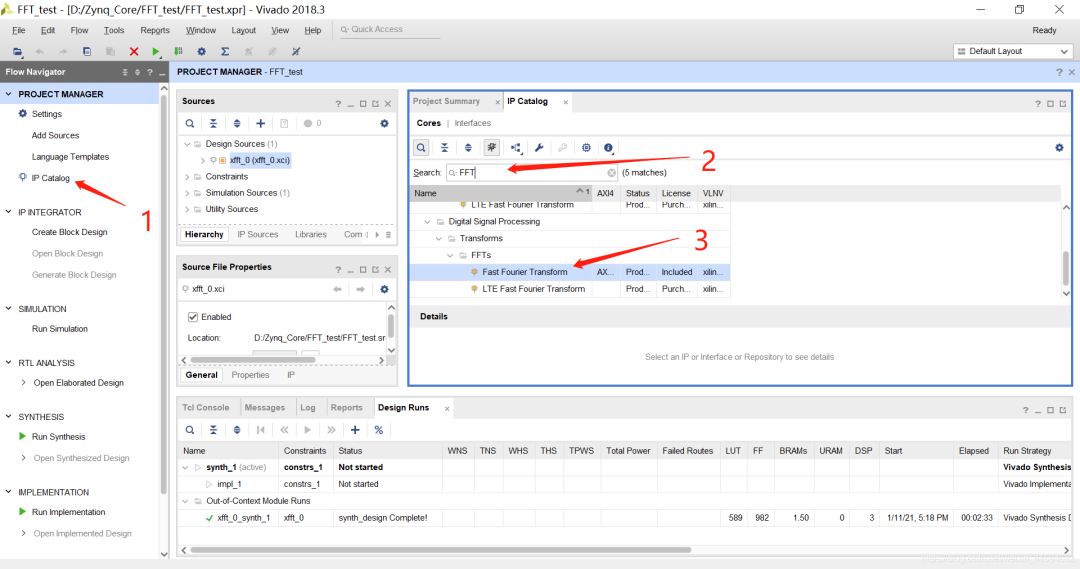

2.Vivado中IP核的配置

打開Vivado軟件,我的版本是2018.04

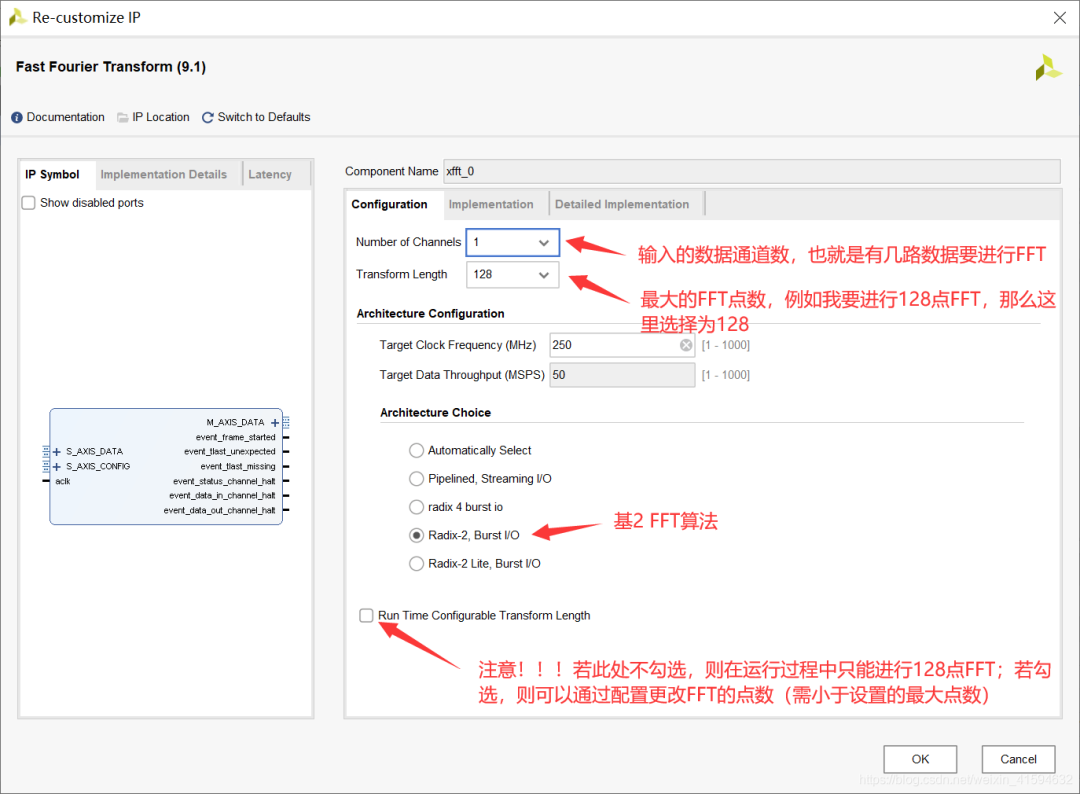

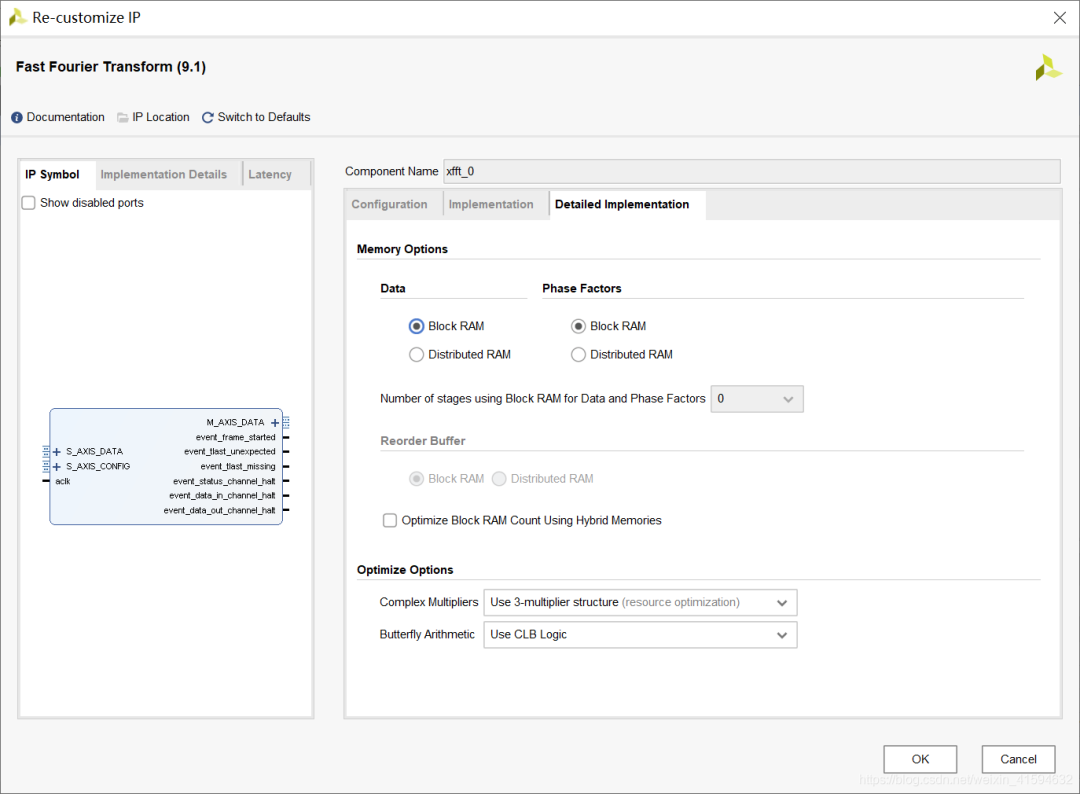

找到FFT IP核后,雙擊,彈出如下對話框:

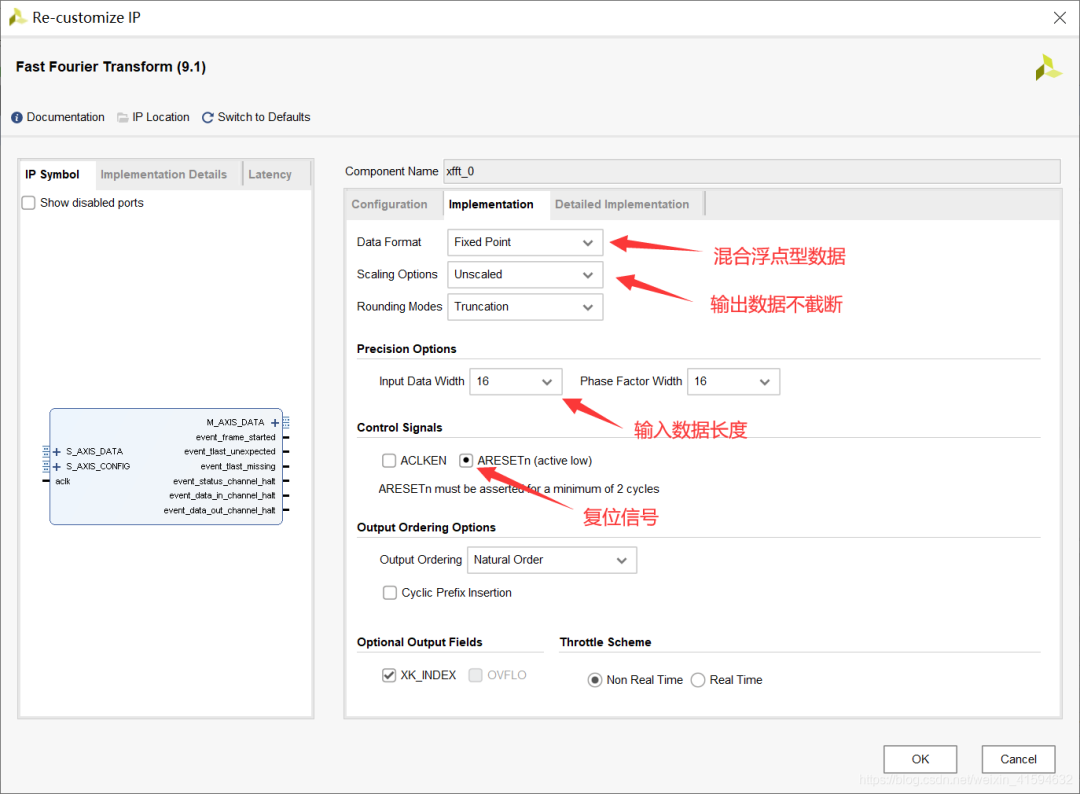

第二頁implementation

第三頁

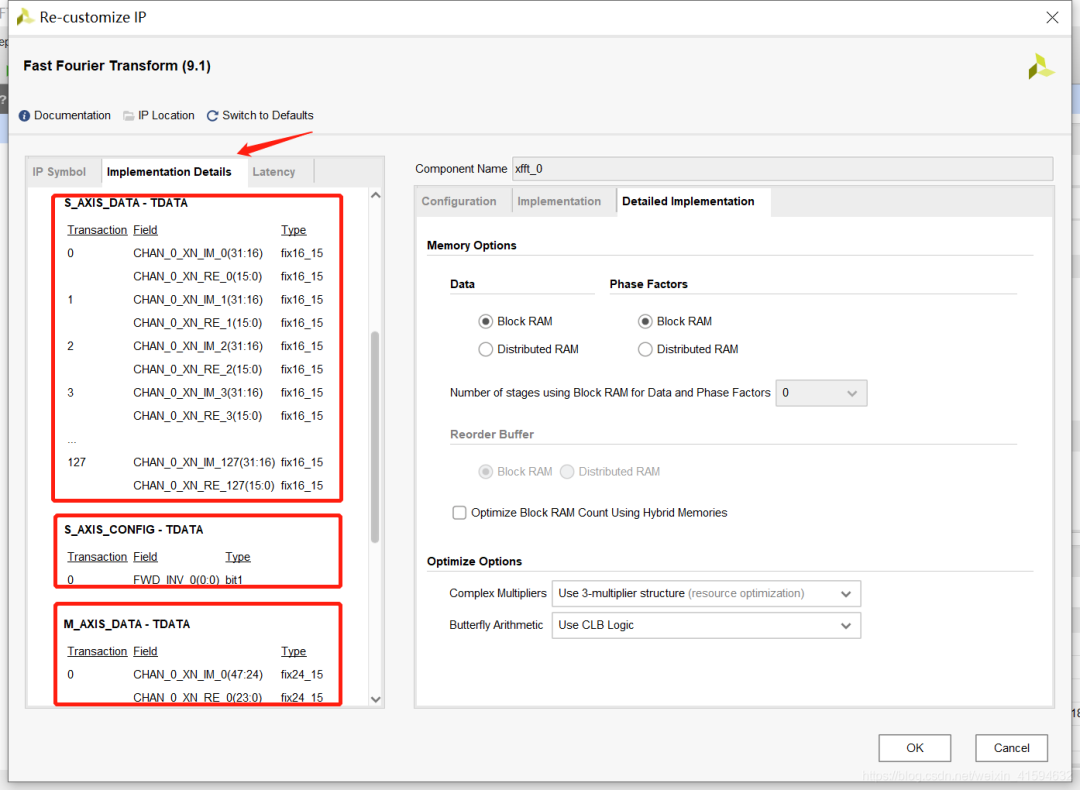

配置完成后,我們可以點擊左側的implementation detail選項卡,看到IP核的具體信息:

其中包含了S_AXIS_DATA_TDATA、S_AXIS_CONFIG_TDATA以及M_AXIS_DATA_TDATA的數據格式,我們需要加以關注:

S_AXIS_DATA_TDATA:共32位,其中低16位為輸入數據的實部,高16位為輸入數據的虛部(但在實際使用中,高16位才是實部,低16位是虛部,如果有大神明白是咋回事兒,歡迎留言)

S_AXIS_CONFIG_TDATA:最低位第0位,決定對數據進行FFT還是IFFT,置1時FFT,清零時IIFT,由于要進行補零操作,因此在最終寫入S_AXIS_CONFIG_TDATA時,除了最低位以外,還要再補七個零,補到8位

M_AXIS_DATA_TDATA:48位數據輸出,低24位為實部,高24位為虛部

3.軟件仿真

IP核配置完成后,下面開始編寫我們的TestBench文件。

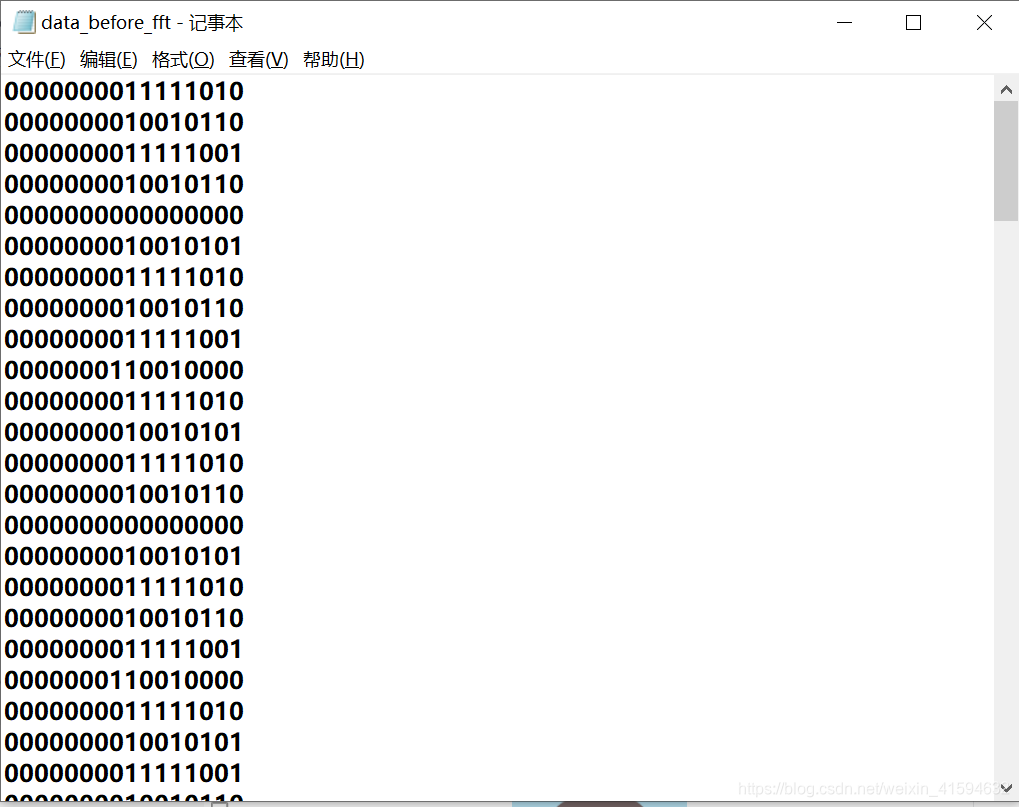

我們通過matlab對F(t) = 200 + 100cos(2pi10t) + 100cos(2pi30t)這個信號以Fs = 100HZ進行采樣,采樣點數N = 128,采樣完成后,將數據轉換為16位二進制,并存入txt文件中。matlab程序如下:

clear Fs=100; %采樣率1ns一個點 %t=0:1/Fs:63/Fs; %數據時長:64個采樣周期 N = 128; n = 1:N; t = n/Fs; % 生成測試信號 f1 = 10; % f2 = 30; % s1 = cos(2*pi*f1*t); s2 = cos(2*pi*f2*t); signalN = 2 + s1 + s2 ; data_before_fft = 100*signalN; %系數放大100倍 fp = fopen('D:ynq_Coredata_before_fft.txt','w'); for i = 1:N if(data_before_fft(i)>=0) temp= dec2bin(data_before_fft(i),16); else temp= dec2bin(data_before_fft(i)+2^16+1, 16); end for j=1:16 fprintf(fp,'%s',temp(j)); end fprintf(fp,' '); end fclose(fp); y = fft(data_before_fft,N); y = abs(y); f = n*Fs/N; plot(f,y);

程序執行結束后,我們可以看到在指定目錄下新建了一個txt文件,內容如下所示:

由于我們在配置IP核的時候配置了數據位寬為16位,因此我們存入的數據也要設置為16位的。采樣點數N=128,因此一共有128個這樣的數據。

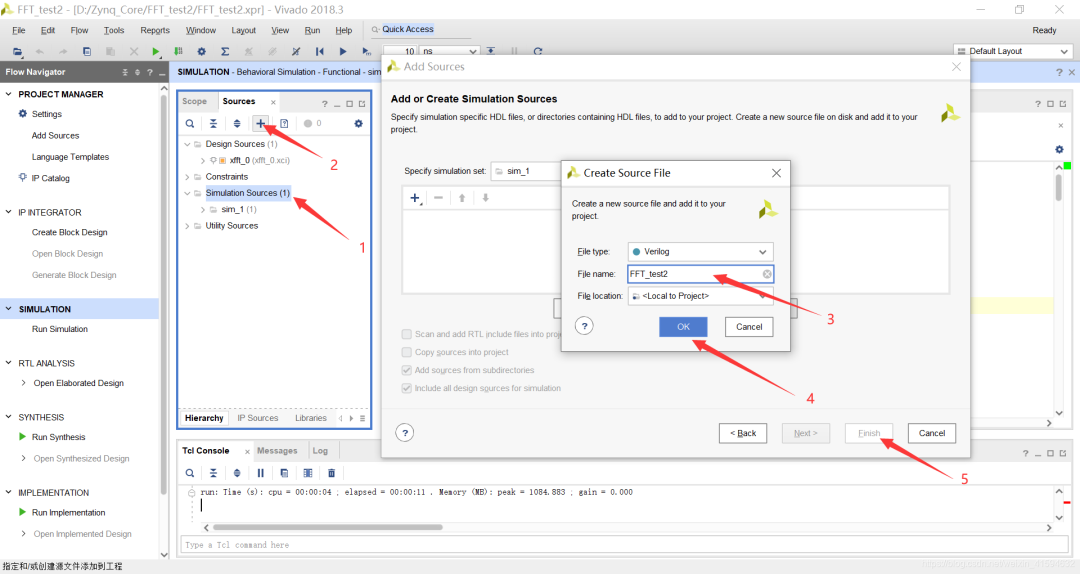

得到采樣數據后,在vivado中新建一個sim文件:

TB文件代碼如下:

`timescale 1ns / 1ps module FFT_test2(); reg clk; reg rst_n; reg signed [15:0] Time_data_I[127:0]; reg data_finish_flag; wire fft_s_config_tready; reg signed [31:0] fft_s_data_tdata; reg fft_s_data_tvalid; wire fft_s_data_tready; reg fft_s_data_tlast; wire signed [47:0] fft_m_data_tdata; wire signed [7:0] fft_m_data_tuser; wire fft_m_data_tvalid; reg fft_m_data_tready; wire fft_m_data_tlast; wire fft_event_frame_started; wire fft_event_tlast_unexpected; wire fft_event_tlast_missing; wire fft_event_status_channel_halt; wire fft_event_data_in_channel_halt; wire fft_event_data_out_channel_halt; reg [7:0] count; reg signed [23:0] fft_i_out; reg signed [23:0] fft_q_out; reg signed [47:0] fft_abs; initial begin clk = 1'b1; rst_n = 1'b0; fft_m_data_tready = 1'b1; $readmemb("D:/Zynq_Core/data_before_fft.txt",Time_data_I); end always #5 clk = ~clk; always @ (posedge clk or negedge rst_n) begin if(!rst_n) begin fft_s_data_tvalid <= 1'b0; fft_s_data_tdata <= 32'd0; fft_s_data_tlast <= 1'b0; data_finish_flag <= 1'b0; count <= 8'd0; rst_n = 1'b1; end else if (fft_s_data_tready) begin if(count == 8'd127) begin fft_s_data_tvalid <= 1'b1; fft_s_data_tlast <= 1'b1; fft_s_data_tdata <= {Time_data_I[count],16'd0}; count <= 8'd0; data_finish_flag <= 1'b1; end else begin fft_s_data_tvalid <= 1'b1; fft_s_data_tlast <= 1'b0; fft_s_data_tdata <= {Time_data_I[count],16'd0}; count <= count + 1'b1; end end else begin fft_s_data_tvalid <= 1'b0; fft_s_data_tlast <= 1'b0; fft_s_data_tdata <= fft_s_data_tdata; end end always @ (posedge clk) begin if(fft_m_data_tvalid) begin fft_i_out <= fft_m_data_tdata[23:0]; fft_q_out <= fft_m_data_tdata[47:24]; end end always @ (posedge clk) begin fft_abs <= $signed(fft_i_out)* $signed(fft_i_out)+ $signed(fft_q_out)* $signed(fft_q_out); end //fft ip核例化 xfft_0 u_fft( .aclk(clk), // 時鐘信號(input) .aresetn(rst_n), // 復位信號,低有效(input) .s_axis_config_tdata(8'd1), // ip核設置參數內容,為1時做FFT運算,為0時做IFFT運算(input) .s_axis_config_tvalid(1'b1), // ip核配置輸入有效,可直接設置為1(input) .s_axis_config_tready(fft_s_config_tready), // output wire s_axis_config_tready //作為接收時域數據時是從設備 .s_axis_data_tdata(fft_s_data_tdata), // 把時域信號往FFT IP核傳輸的數據通道,[31:16]為虛部,[15:0]為實部(input,主->從) .s_axis_data_tvalid(fft_s_data_tvalid), // 表示主設備正在驅動一個有效的傳輸(input,主->從) .s_axis_data_tready(fft_s_data_tready), // 表示從設備已經準備好接收一次數據傳輸(output,從->主),當tvalid和tready同時為高時,啟動數據傳輸 .s_axis_data_tlast(fft_s_data_tlast), // 主設備向從設備發送傳輸結束信號(input,主->從,拉高為結束) //作為發送頻譜數據時是主設備 .m_axis_data_tdata(fft_m_data_tdata), // FFT輸出的頻譜數據,[47:24]對應的是虛部數據,[23:0]對應的是實部數據(output,主->從)。 .m_axis_data_tuser(fft_m_data_tuser), // 輸出頻譜的索引(output,主->從),該值*fs/N即為對應頻點; .m_axis_data_tvalid(fft_m_data_tvalid), // 表示主設備正在驅動一個有效的傳輸(output,主->從) .m_axis_data_tready(fft_m_data_tready), // 表示從設備已經準備好接收一次數據傳輸(input,從->主),當tvalid和tready同時為高時,啟動數據傳輸 .m_axis_data_tlast(fft_m_data_tlast), // 主設備向從設備發送傳輸結束信號(output,主->從,拉高為結束) //其他輸出數據 .event_frame_started(fft_event_frame_started), // output wire event_frame_started .event_tlast_unexpected(fft_event_tlast_unexpected), // output wire event_tlast_unexpected .event_tlast_missing(fft_event_tlast_missing), // output wire event_tlast_missing .event_status_channel_halt(fft_event_status_channel_halt), // output wire event_status_channel_halt .event_data_in_channel_halt(fft_event_data_in_channel_halt), // output wire event_data_in_channel_halt .event_data_out_channel_halt(fft_event_data_out_channel_halt) // output wire event_data_out_channel_halt ); endmodule

由于我們設置程序一直保持正向FFT模式,因此將s_axis_config_tdata始終寫入1即可。

同時我們還要注意文件讀入函數readmemb(),這一函數是以二進制格式讀入數據,而readmemh()是以16進制讀入數據,大家不要搞混了。我就是用readmemh()弄了半天,結果數據一個也不對,找了半天才發現那是h不是b…[cry][cry][cry]

4.仿真分析

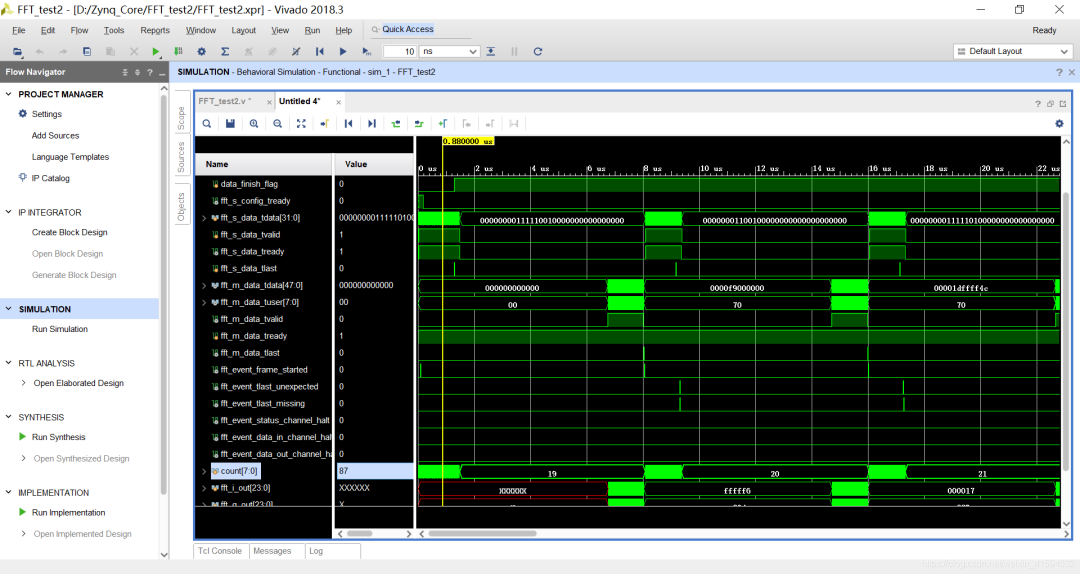

運行仿真后,時序圖如下所示:

如圖所示,首先判斷fft_s_data_tready信號是否為高電平,即IP核是否準備好了接收數據,當檢測到該信號有效后,將fft_s_data_tvalid信號拉高,準備向IP核寫入數據,并開啟count計數。在fft_s_data_tvalid有效期間內,讀出指定txt文件中的數據,并在低16位進行補零處理后,按順序寫入到fft_s_data_tdata信號線中。當count計數到127,即最后一個數據時,將fft_s_data_tlast信號拉高,代表數據寫入完成。

可以看到,在數據寫入完成后(fft_s_data_tlast出現脈沖),fft_s_data_tready變為低電平,則代表IP核此時變為忙狀態,不能再繼續寫入數據。

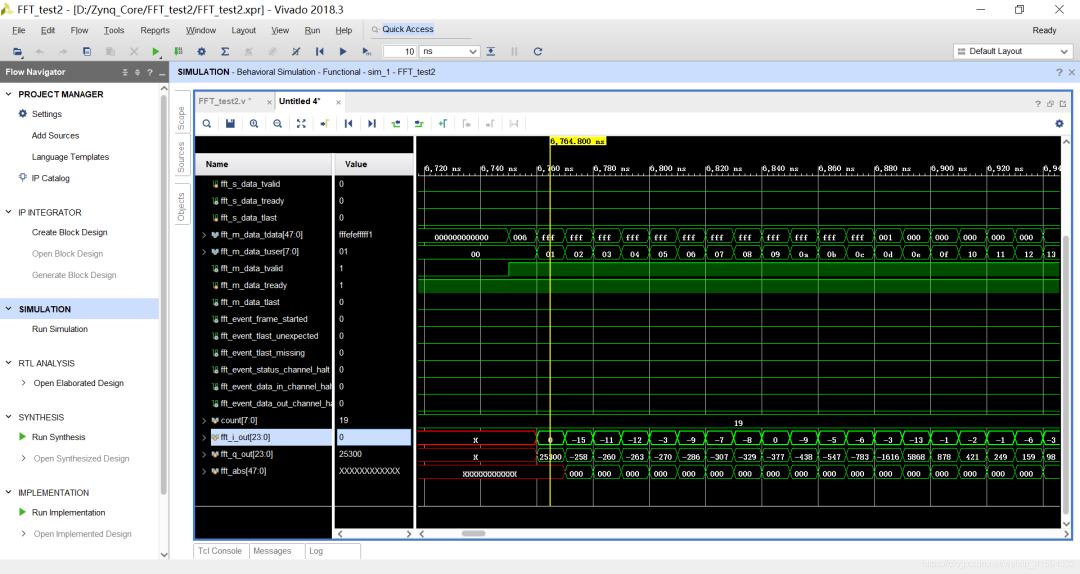

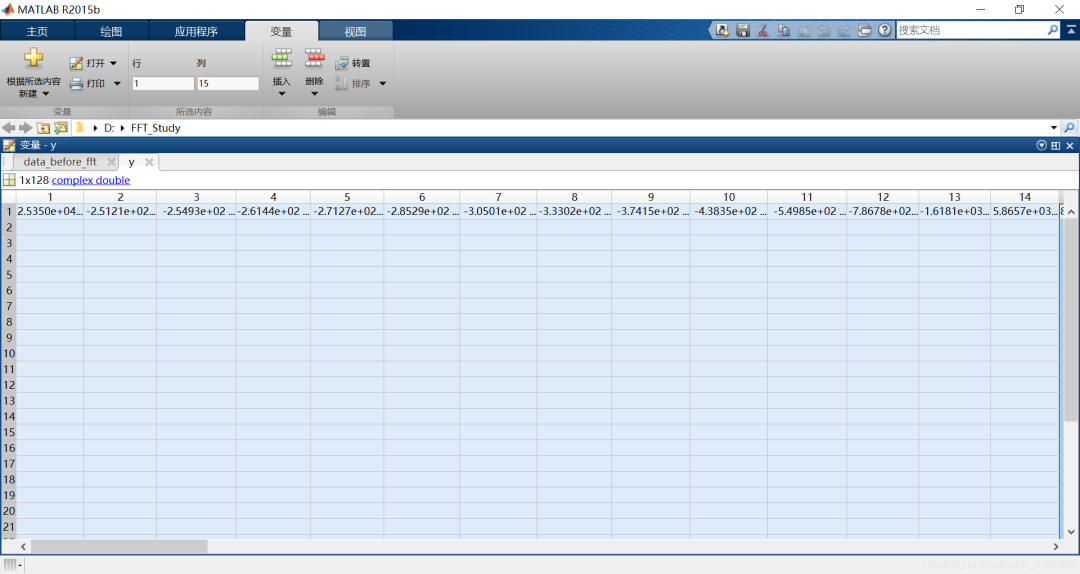

延時一段時間后,fft_m_data_tvalid變為高電平,代表fft_m_data_tdata中將輸出有效數據,即128點FFT的計算結果。結果的實部和虛部分別見上圖中的fft_q_out和fft_i_out。將IP核的計算結果與matlab的計算結果相對比,發現實部數據基本正確,虛部數據略有偏差。

通過對IP核的計算結果進行分析,發現數據在第0個、第14個和34個數據的位置出現峰值,對應0HZ、10HZ和30HZ,正代表著原始信號中的這三個頻率分量,因此FFT IP核計算結果正確無誤。

同時,從仿真中還可以看出,當FFT計算結果輸出完成后,信號fft_m_data_tlast變為高電平,代表數據輸出結束,并在延時一小段時間后,fft_s_data_tready重新變為低電平,代表IP核重新進入到空閑狀態。可以進行對IP核下一組數據的輸入。

原文鏈接:

https://gitcode.csdn.net/6628ae7c9c80ea0d22719dd0.html

-

Xilinx

+關注

關注

71文章

2168瀏覽量

121672 -

IP

+關注

關注

5文章

1712瀏覽量

149654 -

FFT

+關注

關注

15文章

436瀏覽量

59411 -

Vivado

+關注

關注

19文章

813瀏覽量

66657

原文標題:Vivado Xilinx FFT IP核v9.0 使用詳解

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于altera FFT IP核 matlab 仿真問題請教

基于FPGA的FFT和IFFT IP核應用實例

玩轉Zynq連載48——[ex67] Vivado FFT和IFFT IP核應用實例

fft核心v9.0的數據表如何實現FFT核心

Xilinx Vivado的使用詳細介紹(3):使用IP核

FFT的分析和Xilinx FFT核的介紹

ACDSee v9.0 Build 50

Vivado Xilinx FFT IP核v9.0使用說明

Vivado Xilinx FFT IP核v9.0使用說明

評論