導 讀

集成電路產業通常被分為芯片設計、芯片制造、封裝測試三大領域。其中,芯片制造是集成電路產業門檻最高的行業,目前在高端芯片的制造上只剩下臺積電(TSMC)、英特爾(Intel)和三星(SAMSUNG)了。

隨著先進封裝技術的發展,芯片制造和封裝測試逐漸融合,我們驚奇地發現,在先進封裝領域的高端玩家,竟然也是臺積電、英特爾和三星,而傳統的封測廠商,已經被他們遠遠地拋在身后。

那么,這三家的先進封裝到底有什么獨到之處呢?他們為何能超越傳統封測廠商,引領先進封裝,我們通過三期文章來解讀三家的先進封裝技術。

今天,我們詳細解讀英特爾的先進封裝技術。

在芯片發展史上,英特爾無疑是一家了不起的公司,英特爾的創立和發展記錄著芯片發展的歷史,英特爾的每一步都堪稱芯片技術史上的重要節點。

1947年,晶體管發明,這無疑是人類歷史上最偉大的發明。

信息承載量是文明先進程度的重要標志,一個文明其信息的承載量越大,文明程度就越高。

記錄和傳遞信息的基本單位稱為功能單元,晶體管是目前唯一可以不斷縮小而功能保持不變的功能單元,是信息的載體,也是文明先進程度的重要標志。

1958年,集成電路發明,晶體管的微縮之路正式踏上征程。

1965年,摩爾定律提出,指明了晶體管的尺寸微縮和數量增長是以指數方式進行。

1968年, 英特爾由諾伊斯和摩爾聯合創立,迄今已有56年。

今天,人們常說摩爾定律已經終結,難道摩爾親手創立的公司也要因此而終結了嗎?或者,英特爾輝煌時代的結束也預示著摩爾定律的最終結束?

在前面的文章中,我曾寫到:摩爾定律所預示的單位空間內的晶體管數量的增加并未結束,只是不再以指數方式增長。在系統空間內,功能單元的數量會持續增加,并且會一直持續下去,即系統空間內的功能密度會持續增加,謂之功能密度定律。

后摩爾定律時代,功能密度持續增加的原動力正是來源于先進封裝技術。

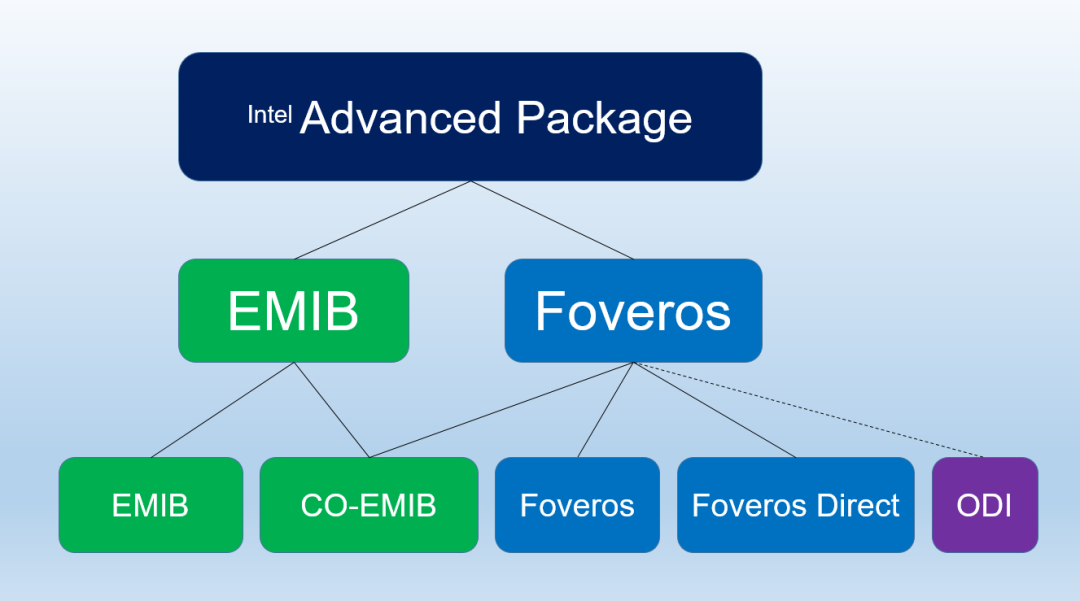

在先進封裝領域,Intel依然是技術的領導者,創造性地推出了EMIB,Foveros,Co-EMIB,ODI等先進封裝和互聯技術,繼續驅動著技術不斷向前。

英特爾的先進封裝技術主要分為兩大類:EMIB和Foveros,此基礎上又擴展出Co-EMIB,Foveros Direct, ODI等。可參考下圖。

1 EMIB

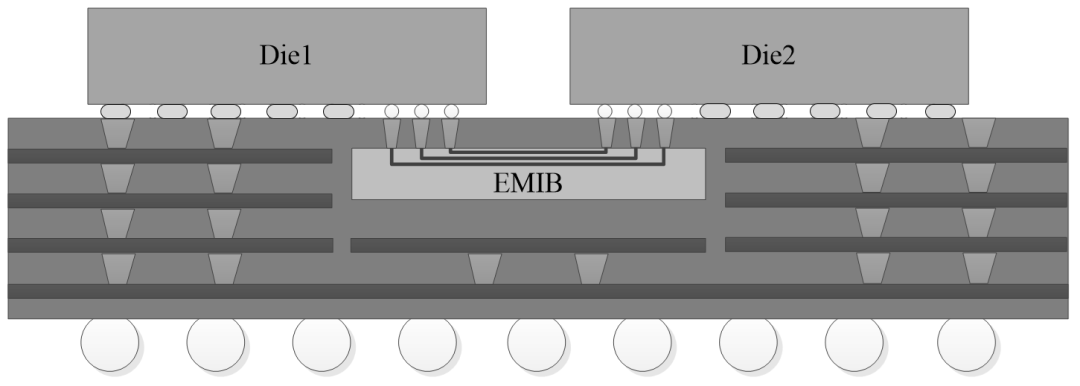

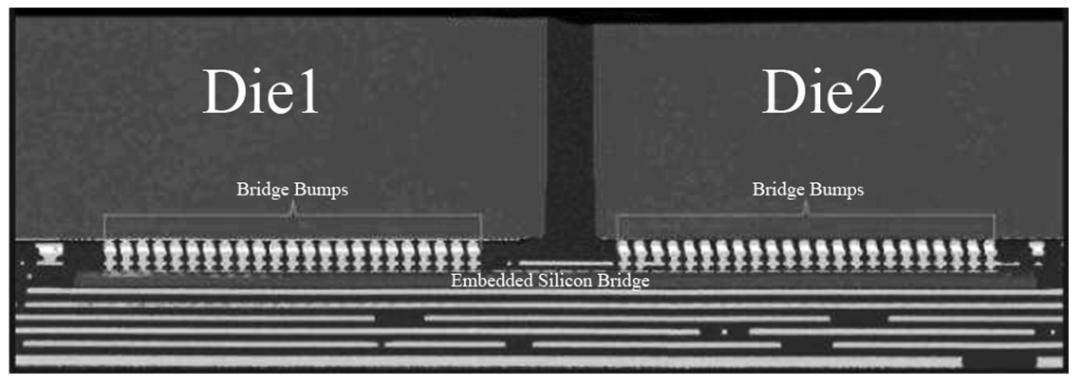

EMIB, Embedded Multi-Die Interconnect Bridge,嵌入式多芯片互聯橋,是一種聰明且靈活的先進封裝技術,在需要高密度互連的芯片部位通過將硅片嵌入基板,形成高密度互連橋。其他區域則通過基板進行互連。

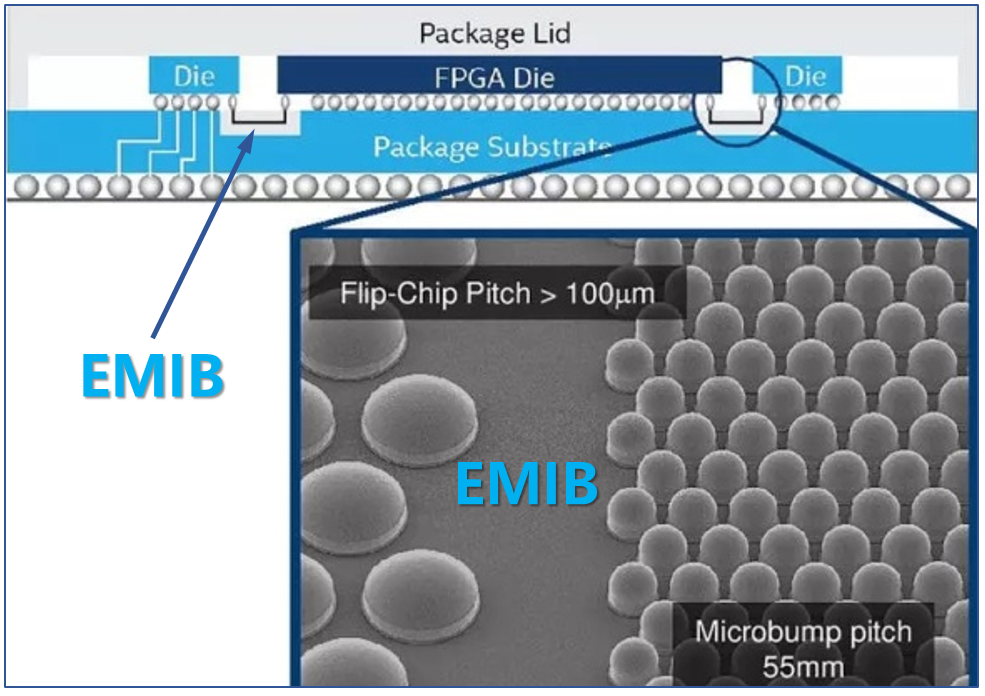

如下所示為EMIB的示意圖和剖面圖,可以看出,在密度高的互連區域,芯片上采用了小而密的凸點,采用EMIB互連,其它區域使用常規凸點,采用基板互連。

例如,常規凸點的間距100um,在EMIB區域則變為55-36um,支持更高密度的互連。

我之所以稱EMIB為一種聰明且靈活的先進封裝技術,就是在需要高密度互連的地方,才會嵌入EMIB。在同一個封裝內,甚至在同一個芯片的不同區域,EMIB互連和常規互連共存,做到了資源共享,中國有句古話,把鋼用在刀刃上,就是對EMIB技術的很好闡述。

EMIB剛推出的時候,被業界嘲笑為“膠水”,認為其將小芯片粘結在了一起。現在卻的得到了越來越多的認可,業界也認識到了EMIB的獨特價值,臺積電的CoWoS-L就是取經EMIB技術。

嚴格來說,EMIB不屬于2.5D封裝技術,因為它既無中介層,也無硅通孔,但是EMIB確實比2D封裝要復雜,在某種程度上達到了2.5D中介層的效果,所以英特爾將其稱為2.5D封裝。在我對封裝類型的定義中,EMIB此類封裝我稱之為2D+,和InFO PoP是劃歸一類的。

下面我們解讀一下Foveros。

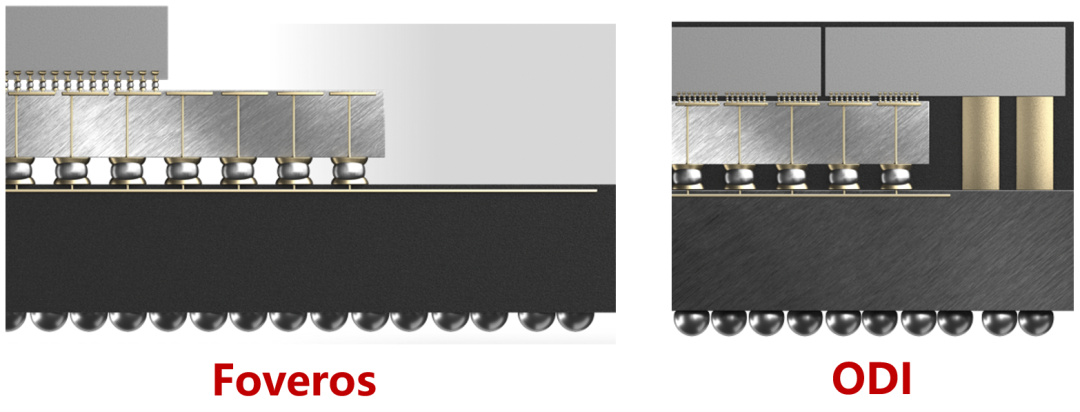

從EMIB到 Foveros,芯片開始堆疊在一起,進行橫向和縱向之間的互連,凸點間距進一步降低到25um。

2 Foveros

Foveros的名字有些繞口,不像EMIB一樣,代表著首字母縮略詞,英特爾官方也沒有給出正式的解釋。

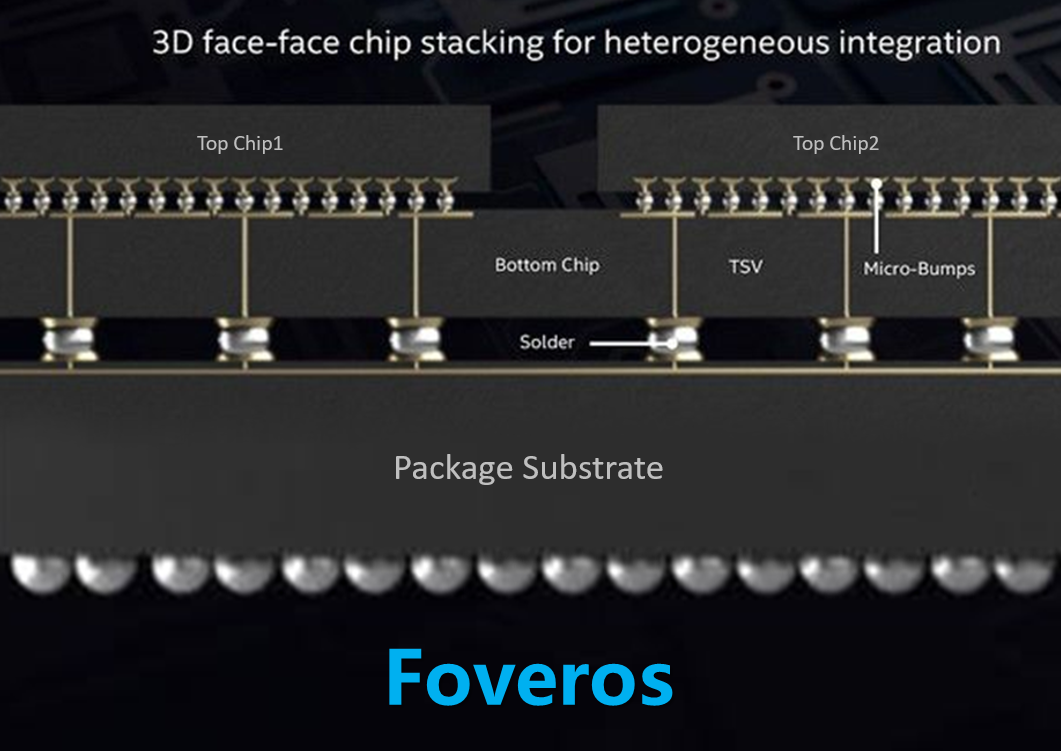

我對Foveros名稱做以下解讀,Foveros分為三部分F-over-os,其中F代表著Face-Face連接,over代表Die over Die,表明Foveros具有芯片堆疊,os代表on Substrate,表明Foveros是安裝在substsrate的。合起來就是具有面對面芯片堆疊的有基板先進封裝。

下圖所示為Foveros的典型結構圖。上方芯片和下方面對面堆疊,通過Micro-Bumps連接,然后通過TSV連接到下方的Solder Bump并安裝在基板上。

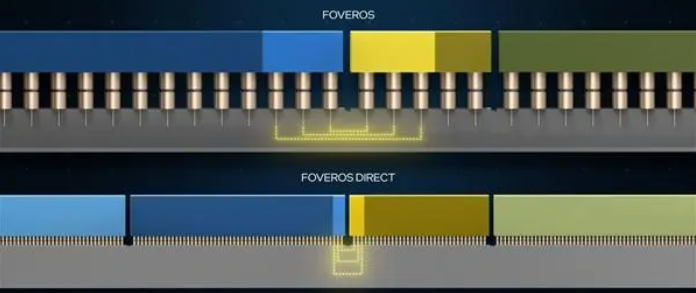

3 Foveros Direct

Foveros Direct是在Foveros的基礎上使用銅與銅的混合鍵合取代Bump,把凸點間距縮小到10微米以下,從而大幅提高芯片互連密度和帶寬。其核心技術就是混合鍵合Hybrid Bonding技術。

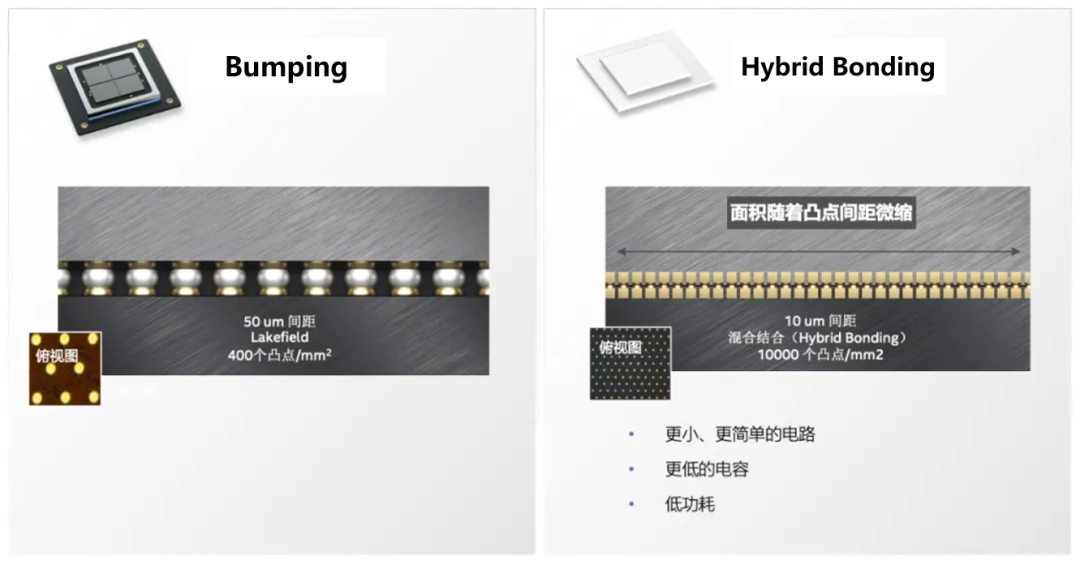

混合鍵合是一種在相互堆疊的芯片之間獲得更密集互連的方法,并可實現更小的外形尺寸。下圖左邊的技術,被稱為Bumping,凸點間距是 50 微米,每平方毫米有大約 400 個凸點。右側為混合鍵合技術,可支持到小于10微米的凸點間距,并達到每平方毫米 10,000 個凸點。

Hybrid Bonding 技術可以在芯片之間實現更多的互連,并帶來更低的電容,降低每個通道的功率,使得產品性能朝著更好的方向發展。

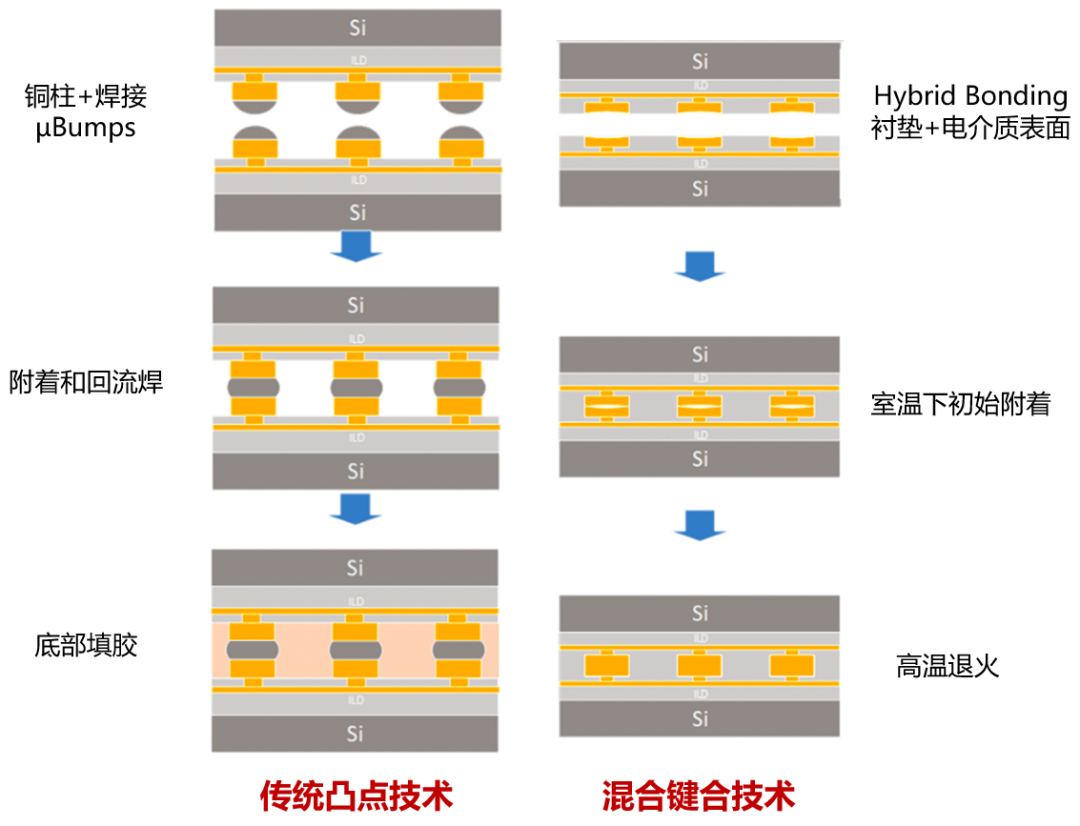

下圖是傳統凸點Bumping技術和Hybrid Bonding 混合鍵合技術加工流程的比較,混合鍵合技術需要新的制造、操作、清潔和測試方法。混合鍵合技術的優勢包括:有更高的電流負載能力,可擴展的間距小于1微米,并且具有更好的熱性能。

從圖中我們可以看出,傳統凸點Bumping技術兩個芯片中間是帶焊料的銅柱,將它們附著在一起進行回流焊,然后進行底部填充膠。

Hybrid Bonding 混合鍵合技術與傳統的凸點焊接技術不同, 混合鍵合技術沒有突出的凸點,特別制造的電介質表面非常光滑,實際上還會有一個略微的凹陷。在室溫將兩個芯片附著在一起,再升高溫度并對它們進行退火,銅這時會膨脹,并牢固地鍵合在一起,從而形成電氣連接。

混合鍵合技術可以將互聯間距縮小到10 微米以下,可獲得更高的載流能力,更緊密的銅互聯密度,并獲得比底部填充膠更好的熱性能。當然,混合鍵合技術需要新的制造、清潔和測試方法。

未來先進封裝中,互聯的密度會更大,界面間連接的凸點間距會縮小到10um 以下,每平方毫米的凸點數量會超過10,000個。

混合鍵合Hybrid Bonding技術在高密度先進封裝中的普遍應用,在混合鍵合中,凸點已經不存在,除了金屬鍵合在一起,硅體也會鍵合在一起,硅片間沒有了空隙,無需填充導熱膠,并具有更好的散熱性能,因為硅本身就是良好的導熱材料。

Hybrid Bonding已經是高端先進封裝的必備技術,TSMC-SoIC就采用了Hybrid Bonding技術,混合鍵合對目前熱度很高的3.5D先進封裝也同樣必不可少。

4 Co-EMIB

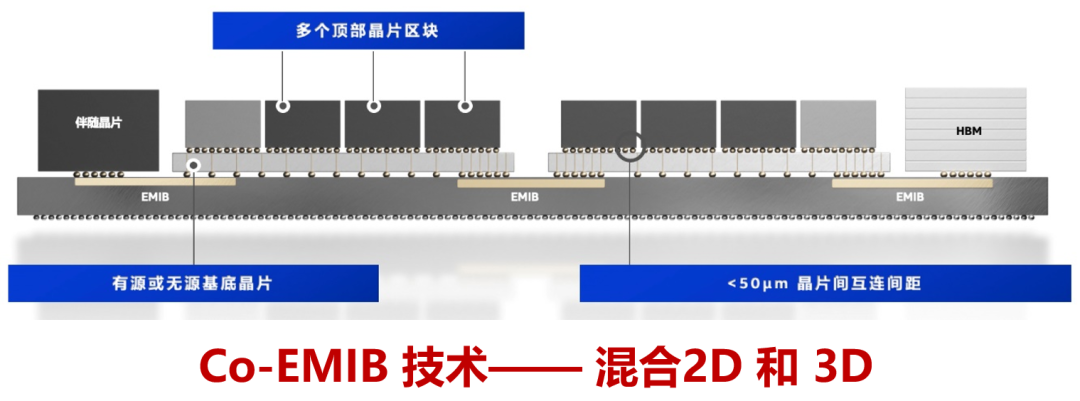

Co-EMIB技術通過使用 EMIB 和 Foveros 的組合來融合 2D 和 3D 的技術, EMIB負責提高水平互連的密度,Foveros負責打通垂直互連通道,通過 Co-EMIB技術可將多達幾十個芯片放入一個封裝中。

Co-EMIB 架構基于與配套晶片和堆疊芯片復合體的高密度連接,實現了更大范圍的互聯,下圖展示了Co-EMIB的示意圖,結合了 EMIB與 Foveros技術。

英特爾已經試圖通過很多策略來延續摩爾定律的,目前除了量子計算等革命等級的全新計算架構外,CO-EMIB可以說是在維持并延續現有計算架構與生態的最佳做法。

英特爾認為,歸根結底,我們擁有的發展機會是在每毫米立方體上提供最多的單元并獲得每毫米立方體最多的功能。先進封裝將繼續小型化和縮小尺寸,以便我們可以獲得每毫米立方體的最大功能。

5 ODI

ODI (Omni-Directional Interconnect) 全方位互連技術,這是先進封裝的一個新維度。

下圖左邊是 Intel 的 Foveros技術,垂直堆疊芯片,使用TSV在芯片和基板之間、芯片和芯片之間通信,一直到頂部芯片。在下圖的最右側,添加了金屬支柱,允許最右側的頂部芯片直接連接到封裝。

這對封裝非常有幫助,因為它可以減少下部芯片TSV的數量,這些支柱為先進封裝提供了直接向頂部芯片供電的能力。這是另一種優化,通過添加 ODI 技術為客戶進行全方位定制。

從 Intel的技術路線圖中,我們可以看出,先進封裝除了向更高密度方向發展,在擴展軸上,同樣關注集成的靈活性,Co-EMIB和ODI就體現了這樣的特點。從SoC到SiP再到Chiplet,電子集成更關注高時效、低缺陷率、高可重用性。

而達成這個技術的關鍵角色,就是Omni-Directional Interconnect (ODI) 全向互連技術,作為連接大樓不同樓層的管道,我們可以把這個部件看成是樓梯間,可以通過樓梯間,直達不同樓層。

ODI可以有兩種不同型態,除了打通不同層的電梯型態外,也有連通不同立體結構的天橋,以及每層之間的夾層,通過這個設計,讓不同芯片的組合可以有極高的彈性。

通過這些全新的3D封裝方式,芯片設計思維也從過去的平面拼圖,變成堆積木。在芯片內就能完成的異構計算,要遠比通過外部總線連接的不同計算單元更為高效,且更有利于推升算力。

EMIB、CO-EMIB、Foveros、Hybrid bonding和ODI等技術都有助于構成系統級封裝的一部分,系統級封裝更強調系統在封裝內的實現,是先進封裝的重要代表。

在《基于SiP技術的微系統》一書中,我提出了功能密度定律(Function Density Law)的概念,以單位體積內的功能單位(Function UNITs)的數量來評價電子系統的發展,將評判標準從摩爾定律的晶圓平面變成了電子系統空間,即從三維空間的角度來評判電子系統的集成度。

英特爾認為,先進封裝技術的發展是在每毫米立方體上提供最多的單元并獲得每毫米立方體最大的功能,和功能密度定律的定義是完全一致的。

Intel提出的每毫米立方體里的功能,和我在功能密度定律里描述的單位體積內的功能單位 (Function UNITs)是同樣的概念,也從側面印證了功能密度定律。

Intel致力于實現每毫米立方體里最大的功能,和功能密度定律的描述一致,所謂英雄所見略同,大致如此。

-

英特爾

+關注

關注

61文章

9978瀏覽量

171923 -

先進封裝

+關注

關注

2文章

414瀏覽量

257

原文標題:先進封裝技術解讀 | 英特爾

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

詳細解讀英特爾的先進封裝技術

詳細解讀英特爾的先進封裝技術

評論