隨著邊緣和端點對更高功能和智能的需求不斷增長,這些設備對更強處理能力和更大內存的需求也在增長。應用程序的功能更加豐富,用戶要求其產品中內置更高級別的功能,包括復雜的圖形和用戶界面、學習算法、網絡連接和高級安全性。目前,機器學習實現了語音和視覺AI功能,可幫助設備在邊緣做出智能決策,并在無需人工干預的情況下觸發操作。復雜的軟件框架是這些解決方案的重要組成部分。

雖然處理能力是所有這些類型應用程序的關鍵,但它們也推動了對代碼和數據的快速、可靠、低功耗和非易失性存儲的需求。在開發嵌入式系統時,設計人員的內存選擇會顯著影響性能、成本、設計復雜性和功耗。需要新的架構來滿足對更高性能、更大內存和更低功耗的不斷變化的需求,同時保持低成本。需要與內存制造商密切合作,以確保滿足性能要求的解決方案經過全面驗證。我們來看看各種內存架構選項及其最佳使用案例。

內部閃存或外部存儲器

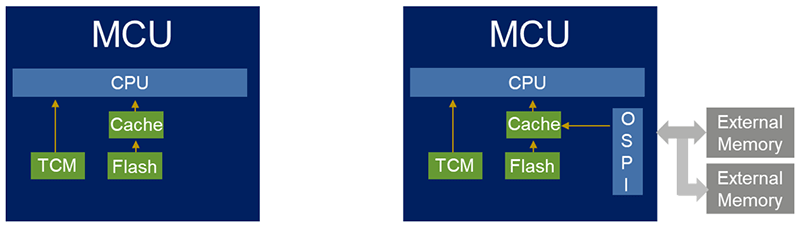

傳統上,中低性能應用中使用的通用MCU將嵌入式閃存(通常為<2MB)作為代碼的首選非易失性存儲。這些集成MCU非常適合工業或樓宇自動化、醫療、家用電器或智能家居等不同細分市場中的大多數中低端物聯網應用。嵌入式閃存具有許多優勢,包括更低的延遲、更低的功耗和更高的性能,并提供了集成度更高的方案,適用于簡化、空間有限的應用以及低復雜的設計。從安全角度來看,它消除了外部的攻擊面。因此,具有集成嵌入式閃存的MCU仍然是大多數性能和功能需求較低的應用的首選解決方案。

但是嵌入式閃存是有成本的,超過一定的內存密度(如2MB),成本開始變得高昂。嵌入式閃存成本高昂,并增加了MCU晶圓加工的復雜性和成本。嵌入閃存所需的額外制造步驟會顯著增加硅的成本。

此外,MCU制造商越來越多地轉向更先進、更精細的工藝幾何結構,如28/22nm或更低,以便擴展到更高的性能并在片上集成更多功能。現在,通常可以看到速度在 400MHz至1GHz范圍內的MCU,這些MCU支持高級圖形、模擬、連接和安全功能,以及高級安全性,以防止數據/IP被盜和篡改。雖然這解決了性能需求,但在這些設備上嵌入內存成為一個挑戰,因為嵌入式閃存在較低的工藝幾何形狀上不能很好地擴展,而且閃存單元不能有效地縮小到40nm以下。所有這些都使其在較低的工藝幾何形狀中可行性降低或成本更高。

外部存儲器

設計人員正在考慮新的架構來縮小這一差距,并越來越多地將外部閃存用于要求更高、性能更高的應用。對更復雜用例(如高端圖形、音頻處理或機器學習)的支持驅動了這一需求,而獨立內存價格的急劇下降推動了這一趨勢。使用外部存儲器可以擴展嵌入式系統中的代碼和數據空間,因為外部閃存基本上是MCU存儲器映射的一部分,可以直接讀取并用于數據記錄或軟件存儲和執行。

對于物聯網產品制造商來說,將外部閃存用于其高性能應用具有多項優勢,包括在存儲器大小選擇方面提供靈活性,以及使其設計面向未來。隨著開發人員添加更多功能,需要更大內存,將較小容量的內存換成引腳兼容的更大容量的內存是一個相當普遍的做法。它還允許他們為各種設計采用統一的平臺方法。

當然,也有缺點,例如訪問外部存儲器所涉及的額外延遲(通過使用Quad/Octal存儲器及仔細使用緩存來減輕)、略高的功率以及外部存儲器的額外成本。它還增加了電路板設計的復雜性,需要在PCB上進行額外的布線并注意信號完整性。

對于MCU制造商來說,將MCU與存儲器分離,使他們能夠轉向更先進的工藝節點,以獲得更高的性能、更高的功能和能效,并降低其器件成本。現在,大多數制造商都集成了四通道或八通道SPI接口,并支持就地執行(XiP)功能,允許與這些NOR閃存器件無縫連接。一些MCU支持動態解密(DOTF),它允許將加密圖像存儲在外部閃存中并安全地導入執行。該解決方案提供當今邊緣應用所需的高性能、低功耗和高級安全性。

圖1. 存儲器拓撲–具有內部和外部閃存的MCU

外部存儲器和環節措施的挑戰

當然,外部存儲器也存在挑戰,包括對與外部閃存相關的延遲及其對整體性能的影響的擔憂。通過使用四通道或八通道SPI接口,可以在一定程度上減輕這種帶寬限制,該接口允許通過4條或8條并行線路傳輸數據,而不是使用常規SPI的單線傳輸數據。使用雙倍數據速率(DDR),通過在時鐘的上升沿和下降沿發送數據,可以將吞吐量增加一倍。外部閃存制造商還內置了對突發讀取模式的支持,以便更快地訪問數據,并且可以使用緩存來減輕一些延遲影響,但需要仔細管理軟件以最佳方式使用緩存。系統設計人員還可以通過將代碼傳輸到內部SRAM并在SRAM外執行以獲得最高性能來緩解一些延遲問題。

還有擔心使用外部閃存會帶來更高的功耗,因此內存制造商特別注意優化這些設備的電流消耗。外部存儲器存在一些安全風險,因為它增加了外部的攻擊面,從而造成了可被黑客利用并需要保護的漏洞。這要求MCU制造商向Quad/Octal SPI接口添加加密/解密功能,以便可以安全地存儲和引入加密代碼。

將外部閃存與RA MCU配合使用

瑞薩的RA系列MCU集成了嵌入式閃存以及與外部存儲器的多個存儲器接口,以提供最大的靈活性和性能。它們支持四通道或八通道SPI接口,通過使用4條或8條數據線而不是通常的SPI接口線來提高數據吞吐量。這可以顯著提高性能,尤其是在需要快速內存訪問(如圖形、音頻或數據記錄)的應用程序中。

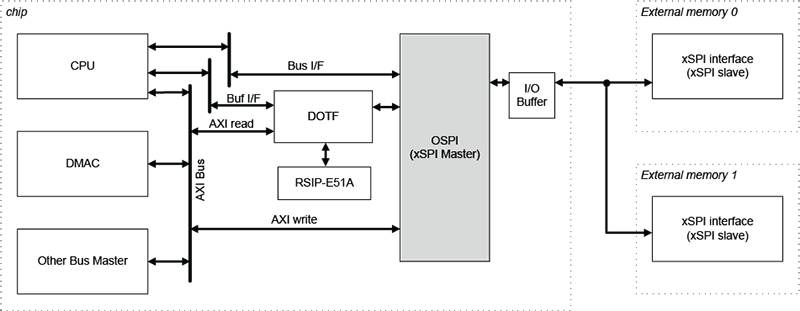

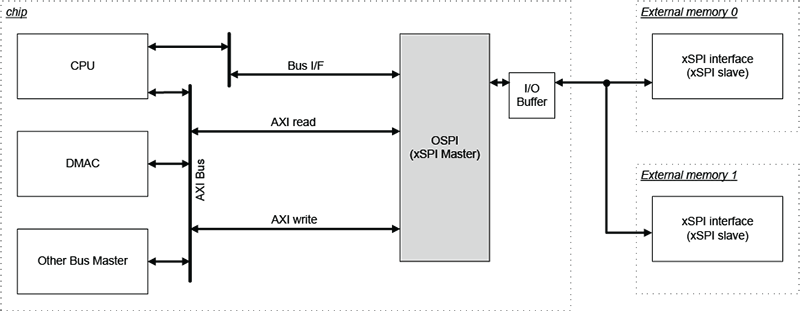

所有RA8系列MCU都包括一個符合eXpanded串行外設接口(xSPI)的八通道SPI接口。xSPI協議指定了非易失性存儲設備的接口,并實現了高數據吞吐量、低信號數以及與傳統SPI設備的有限向后兼容性。使用片選可以將兩個外部存儲器件連接到八通道SPI接口,如下所示,為設計人員提供了更大的靈活性。一些RA8 MCU還支持動態解密(DOTF),允許安全地導入存儲在外部閃存中的加密圖像進行執行。圖2和圖3顯示了RA8 MCU上的八通道SPI接口,支持和不支持DOTF。

圖2. Octal SPI支持DOTF

圖3. Octal SPI不支持DOTF

Octal SPI接口的一些功能:

協議–xSPI,符合

- JEDEC標準JESD251(Profile 1.0和2.0)

- JESD251-1和JESD252

支持的存儲器類型–八通道閃存和八通道RAM、HyperFlash和HyperRAM

數據吞吐量–高達每秒200MB

數據傳輸/接收–可以使用片選與最多2個從站通信,而不是并發

支持就地執行(XiP)操作

支持的模式

- 帶SDR/DDR的1/4/8針(1S-1S-1S、4S-4D-4D、8D-8D-8D)

- 帶SDR的2/4針(1S-2S-2S、2S-2S-2S、1S-4S-4S、4S-4S-4S)

內存映射

- 每個CS最多支持256MB地址空間

- 預取功能,用于低延遲的突發讀取

- 出色的緩沖區,用于高吞吐量的突發寫入

安全性–支持DOTF(在某些RA8 MCU上可用)

除了內部閃存和外部存儲器接口外,RA8 MCU還包括緊密耦合存儲器(TCM)和I/D緩存,有助于優化性能。TCM是零等待狀態內存,在所有片上內存中具有最低的延遲;它可以用于代碼的最關鍵部分。

使用RA8系列MCU上提供的各種存儲器和存儲器接口,可以實現多種靈活的存儲器配置。代碼可以存儲在內部嵌入式閃存中并從內部嵌入式閃存執行,從而實現簡單、低延遲、高度安全且節能的系統。然而,這不是一個可擴展的解決方案,任何超出嵌入式閃存大小的代碼大小增加都需要通過外部存儲器來解決。

在第二種配置中,代碼存儲在外部flash中并在外部flash執行。這是XiP功能,也是最靈活和可擴展的選項。隨著代碼大小的增加,外部存儲器可以簡單地換成引腳兼容、密度更高的器件,無需重新設計電路板即可輕松升級。這是以略高的功耗和更大的延遲為代價的,這可能會對整體性能產生影響。

代碼也可以存儲在外部閃存中,并引入內部SRAM或TCM執行。這提供了最高性能,因為代碼是通過快速SRAM執行的,但是根據SRAM大小對代碼大小有限制,如果代碼大小超過可用的SRAM或TCM,則會增加軟件復雜性。喚醒時間也可能增加,因為SRAM關閉時丟失的代碼需要在每次重啟時重新加載。

結論

在內存選項選擇方面,沒有單一的正確答案。雖然大多數中低端IoT應用程序可以使用內部閃存,但許多高性能應用程序需要使用外部閃存。內存選擇必須基于幾個考慮因素-應用程序要求、所需的內存大小、預期性能、系統架構、功耗目標、安全問題和未來的產品/平臺計劃等。

兩種解決選項都有優點和缺點:

| 內部閃存 | 外部閃存 |

| 提供簡單性 | 靈活性 |

| 緊密集成 | 內部擴展 |

| 高度安全的解決方案 | 可擴展性 |

| 適用于廣泛的應用 | 非常適合新興的loT和邊緣AI應用 |

通過了解這些權衡,開發人員可以做出符合其項目目標的明智決策。

在每個器件產品頁面上獲取有關RA8 MCU系列上可用的靈活存儲器選項的所有詳細信息,以及數據表、樣品和評估套件。

-

mcu

+關注

關注

146文章

17172瀏覽量

351571 -

存儲器

+關注

關注

38文章

7507瀏覽量

163963 -

內存

+關注

關注

8文章

3031瀏覽量

74121 -

瑞薩電子

+關注

關注

37文章

2867瀏覽量

72237

原文標題:工程師說 | 選擇最適合您的系統需要的內存選項

文章出處:【微信號:瑞薩電子,微信公眾號:瑞薩電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PROTEL新手最適合的教程我是受益匪淺希望對你有用

請問任何人都有過IO標準最適合LPDDR內存的經驗嗎?

嵌入式設計中,如何評估最適合應用的 RTOS?

示波器的反應特性指的是什么?如何來選擇最適合的示波器呢?

如何選擇最適合自己的筆記本電腦

什么手機最適合玩手機游戲?選驍龍痛快贏

如何選擇你的公司最適合最需求的MES制造執行系統

如何才能購買到一個最適合您的數字貨幣錢包

蘋果13最適合買的配置

如何在眾多型號中選擇最適合的SMT貼片機

如何選擇最適合你的UV LED固化機?

選擇最適合您的系統需要的內存選項

選擇最適合您的系統需要的內存選項

評論