有源電掃描陣列(AESA)技術最近的發展趨勢正在瞄準衛星和無人機(UAV)上的新型雷達有效載荷,這些載荷可以和現代化地面、機載以及艦載雷達一起,通過改良的情報、監視、偵查(ISR)系統,幫助軍事決策者應對瞬息萬變的軍事行動需求,并更好地把握戰局態勢。這些雷達載荷在尺寸規模和工作性能方面催生的需求正在逐步被新的架構設計和系統能力所解決,而正是諸如GaN功率放大器(PA)、新型微波單片集成電路(MMIC)、“extreme”MMIC器件、“超越摩爾定律”的異質集成、收發(T/R)模塊成本縮減、新型毫米波硅基集成電路(IC)、光電集成等這些微波和信號處理技術的發展使得這一切成為可能。

在這些進步的背后是大量逐步發展的電子設計自動化(EDA)技術,它們為設計者在樣機開發之前提供了系統架構、元件規格、個別元件物理設計和驗證等各方面的支持。本文將對這些技術的發展趨勢進行討論,并通過幾個例子展示EDA工具的進步是如何支撐下一代AESA和相控陣雷達發展的。

1相控陣技術

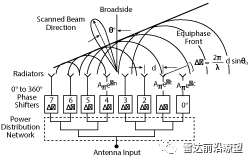

AESA雷達,也被稱作有源相控陣雷達(APAR),由獨立輻射陣元(即天線陣元,每個都帶有一個包含低噪聲接收機的固態T/R模塊)、PA以及增益和相位(或延遲)數控單元構成。陣元輸入信號的相位和幅度控制為天線波束在俯仰和方位向提供了可控的方向性,這使得雷達能夠將天線主瓣“瞄準”需要的方向。與機械掃描雷達不同,相控陣雷達能夠在空間上幾乎無延時地輪換模式,模塊收發增益和時序的數字化控制造就了具備波束指向敏捷、雷達模式交叉和極低副瓣性能的天線,相對于無源電掃描陣列(ESA)和機械掃描雷達來說,這極大地降低了天線雷達的特征。波束寬度依賴于陣列中陣元的數量,通過增加陣元(或傳感器)數量,波束能夠變窄,并且更加有效地對小目標進行探測。如今的AESA雷達通常由成千上萬的陣元組成,這些陣元通過日益復雜的結構相互連接,從而達到小尺寸、低重量和高性能(即低損耗)的目的。

當RF頻率在10GHz以下時,其波長會使得天線尺寸和間距增大,RF、中頻(IF)和基帶信號的布線通過印制電路板(PCB)上的分立元件和現貨供應的MMIC就能解決,信號路徑過長帶來的影響會被PCB在這些頻點較低的損耗所抵消,而且鑒于相對靈活的封裝需求,天線接口可以認為和IC單元無關。但是,在毫米波頻段(即30GHz以上),物理上小的天線間距(~λ/2< 5 mm)、封裝損耗和包括阻抗控制、多層封裝互聯在內的工藝挑戰使得高功能度和精密集成的IC更加具有吸引力,這些高頻信號的復雜封裝和布局設計必須依賴于針對RF和毫米波電子器件的電路仿真和電磁分析。

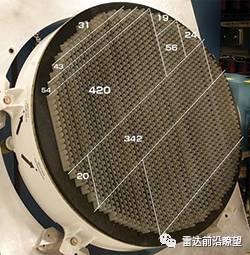

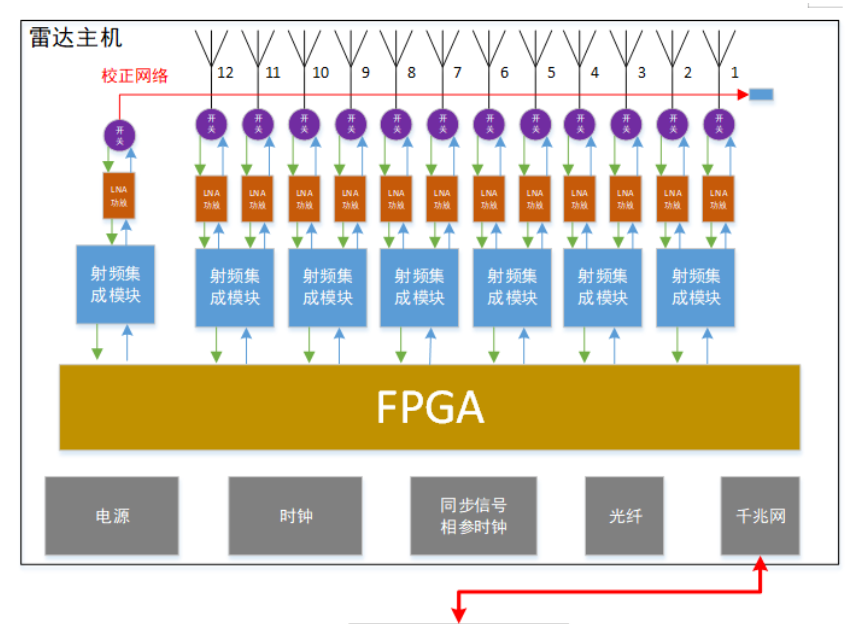

雖然有源相控陣天線具有諸多優點,但卻極其復雜,其一次性開發和制造的成本要遠遠高于普通天線設計,這是因為每個制造單元中成百上千的有源電子模塊(如圖1所示)經常都是基于定制化的GaAsMMIC設計實現的(通常每個系統5-10種設計)。

圖1 AN/APG-80 F-16 AESA雷達陣元局部視圖

2日益增長的集成度

GaAs MMIC技術最初由美國國防部(DoD)在上世紀八九十年代資助和開發,它是制造10~20GHz密集封裝(截面尺寸<1cm)T/R模塊的唯一可行選擇,強大的仿真軟件和廉價的計算資源促進了MMIC設計的進步,這使得工程師能夠設計具備更高精度的復雜電路,開發通用RF模塊庫。早期MMIC的發展解決了一些挑戰,如組合幾十上百個有源和無源元件(單片GaAs襯底上的三極管、PIN二極管、電阻、電容、電感等),在單片單通道或多通道MMIC上組合低噪聲放大器(LNA)、PA、開關矩陣和移相器等RF模塊時集成AESA功能的復雜性等。如今,基于采用新材料、新器件和先進集成技術的多芯片組件,MMIC正朝著更強大的功能和更高的集成密度發展。

美國國防高級研究項目署(DARPA)微系統技術辦公室曾經資助了兩個項目用以研究下一代器件集成技術。“硅基化合物半導體材料”(COSMOS)項目致力于發展新方法將化合物半導體(III-V族化合物)緊密集成到最先進的硅基COMS電路中,“多源可用異質集成”(DAHI)項目繼續了這項工作,開發異質集成技術將使用新興材料和器件的先進III-V族器件和高密度硅基CMOS緊密結合。

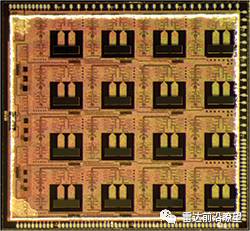

集成技術在過去10年取得了巨大發展。針對DARPA的“集成傳感器即結構”(ISIS)項目,2006年佐治亞技術研究所在單芯片上開發了一款帶有控制電路的4通道X波段SiGeT/R模塊,平均每個T/R模塊成本約為10美元;2008年,加利福尼亞圣地亞哥大學(UCSD)的研究者在性能和集成密度上取得了重大突破,他們設計和演示了第一款SiGeRF波束形成IC:一個6~18GHz,帶有5比特相位控制和片上8:1復合器的8單元相控陣接收機;2009年,UCSD緊接著又研發了第一款16單元、45~50GHz的相控陣發射機;2013年,UCSD報道了一款110GHz、4*4晶元級、帶有高效片上天線的相控陣發射機,并成功演示了其單芯片解決方案(如圖2所示)。

圖2 110GHz4*4晶元級相控陣發射機

由于相控陣天線正在逐步演變成支持多輻射單元的硅基核心芯片,首選的解決方案通常都是將硅和III-V族前端結合起來,以滿足需要盡可能最佳性能的應用,特別是對諸如噪聲系數(NF)和輸出功率等品質因數的需求。GaN正在越來越多地取代GaAs成為高功率或寬帶前端材料,對于固定的功率電平,一片GaNMMIC的大小僅有GaAs MMIC的三分之一到四分之一,這足以抵消GaN帶來的高材料成本,GaN晶元成品(包括材料)的成本是GaAs的兩倍,從而GaN解決方案平均每RF瓦特消耗的成本只有GaAs的50~66%。鑒于GaN成本的不斷降低,可以預見GaAs將在很多應用中從相控陣天線里消失。

對寬禁帶(Wide BandGap,WBG)半導體研究持續不斷的投入將有望使得“morethan Moore”功率電子器件邁上一個新臺階,研究者們正致力于通過將GaN異質集成到硅晶元上改進GaN技術,在更大的硅晶元上集成GaN和采用標準半導體工藝流程將會以更低的成本帶來更高的功能和性能,所有這些技術都需要設計者能夠有效理解獨特技術和對整體性能影響之間的均衡。

雖然GaAs MMIC的密度要比競爭的硅數字IC小很多,但高頻設計仍需要特別注意互聯技術和電磁仿真,這有助于預測可能導致性能失效的寄生行為。元件的物理布局和互聯是RF和微波電路設計的關鍵步驟,軟件應當采用統一數據模型(UDM)將基于原理圖的電子元件和經過電磁(EM)仿真的布局固有地聯系起來。隨著技術集成水平的提高,這種分析對于成功的MMIC開發至關重要。

在III-V族材料和Si集成技術解決下一代相控陣雷達尺寸和功能需求的同時,高密度IC同樣對晶元制造質量提出了要求,一百個晶體管中如果有一個因為制造缺陷而出現問題,那將意味著失去整個昂貴的模具。所以,微波RF電路的設計需要對元件的布局和互聯建立RF設計規則,基于成品率和極限條件分析的健壯性設計也必須納入到設計階段,用于研究制造工藝偏差所帶來的影響。

3仿真工具

系統工程在毫米波頻段硅技術中扮演著關鍵角色,由于產業正朝著高集成、多功能核心芯片方向發展,RFIC開發者擁有可以全面檢查架構和可用技術之間協調平衡的內部專家系統也越來越重要。系統仿真將電路仿真和輻射及信號處理行為模型聯系起來,它使得系統設計者能夠為應用選擇最佳的單片工藝,并確定早期架構定義和元件規范。

高層次系統工具無法準確對大量單獨定義的內部連接通路行為進行準確建模是導致設計失敗和高開發成本的一個原因,部分或完整地實際建造相控陣系統來研究這些不可預見的內部行為代價高昂,因為需要實現大量通路并對其行為特征進行測試,而且隨著天線陣列和波束指向控制電路集成度的提高,這個挑戰將日益嚴峻。

由于設計過程中的制造和測試迭代成本過高,開發往往只局限于第一或第二階段一個概念性驗證展示的原理樣機。與規格的不符將導致整個天線/電子系統難以接受的設計和測試迭代次數,這使得包含整個系統的仿真成為必要。考慮到相控陣的性能不僅單純取決于天線和微波電子器件的行為,仿真必要抓住它們的組合行為以便準確對整個系統進行預測。

雖然應用于單獨電路方面的EDA工具已經非常成熟,但將整體系統性能看作是所構成分系統的函數,并采用這些工具對其進行評估的做法仍不常見。高層次的系統分析通常都是通過電子數據表格(如Excel)或基于MATLAB這類產品的一般數學計算來完成的,這些個性化方法的復雜程度往往每個公司都不一樣,甚至同一個公司里不同項目之間也千差萬別,這些個性化工具一般只適用于定義基礎分系統(如MMIC、天線、RF無源和控制單元)的性能需求。

更健壯的分析方法應當將相控陣系統中每個分立組件的性能度量都結合起來,并提供一個對高層系統性能更加準確的評估。一開始,這種分析可以用來指定整個系統的元件拓撲結構和單獨分系統的性能需求,當有了更加詳盡的分系統模型后,將其整合到全系統的分析中,從而獲得對于整體系統性能的更好把握。

系統仿真允許設計者:在很大的功率和頻點范圍上評估陣列性能;執行各種預算分析測量,如級聯增益、NF、輸出功率(如P1dB)、增益與噪聲溫度比(G/T);通過成品率分析評估缺陷和硬件損傷敏感性;使用相控陣全模型進行端對端系統仿真。

參數分析使得設計者能夠有效研究系統變化以便平衡成本和性能,參數分析的例子有T/R模塊規格、移相器分辨率(即比特位數)和誤差、組合器和分頻器拓撲結構、阻性和抗性振幅形成、天線單元數量和間距等。

4基于VSS的相控陣分析

作為本方法的例子,針對AESA的全系統分析能力已經被添加到“虛擬系統仿真器”(VSS)軟件中,該仿真器運行在國家儀器(NI)的AWR設計環境平臺上,它將系統性能看作是受波束方向、天線設計和實現電子波束掃描的有源無源電路單元等因素所影響的函數。當前的VSS版本能夠對具有上千個天線單元的相控陣進行建模,支持各種標準和定制幾何布局的陣列配置。此前,軟件中相控陣基于基本獨立模塊實現,其規模限制在幾百個陣元左右,每個陣元都被建模成一個輸入或輸出模塊;現在,相控陣的行為可以方便地通過參數對話框或包含配置參數的數據文件實現,這些參數包括增益和相位偏移、入射的俯仰和方位角、X和Y向位置(絕對長度或以波長為單位)以及信號頻率等。相控陣模型既能夠設置為發射也能設置為接收,在發射模式,激勵每個陣元的信號功率基于用戶定義的設置進行計算,包括:無損,所有陣元以輸入信號功率進行激勵;功分,輸入信號功率在陣元之間均勻分配;壓分,輸入信號電壓在陣元之間均勻分配。

基于增益錐削的幅度激勵通常被用來控制波束形狀和減小副瓣,一些常用的增益錐削已經在相控陣模塊中實現,其系數處理決定了加權是否是歸一化的,如果是,錐削會歸一化到單位增益。相控陣模型中的標準增益錐削包括切比雪夫錐削、泰勒錐削和均勻錐削,用戶也可以通過指定每個陣元的增益和相位來實現定制化的錐削方式(如圖3所示)。

圖3用于波束形成、指向和副瓣控制的增益及相位錐削

除了各種信號分布電路和對頻率相關操作的支持以外,模型還允許用戶對由制造缺陷或單元失效引起的陣列瑕疵進行仿真。所有的增益和相位計算都在內部進行,用戶還可以調用成品率仿真來評估模塊對任意定義的相控陣參數方差的敏感性。

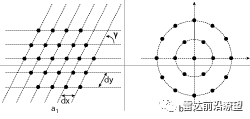

圖4網格(a)和圓環(b)相控陣布局

參數對話框允許用戶快速通過標準或自定義的幾何布局來設計天線整列架構。網格選項(如圖4a所示)中相控陣成網格分布,其布局通過X和Y軸向陣元數量(NX和NY)、軸間陣元距離(dx和dy)以及軸之間的夾角(γ)來配置,γ可以取任意正值,γ= 90°即為矩陣網格,γ = 60°即為三角網格。環形選項(如圖4b所示)將相控陣配置成一個或多個同心圓,每個同心圓上的陣元數量和圓的半徑可以通過變量NC和R定義成向量形式。同樣的,用戶自定義選擇可以通過設置陣元數量N和各自的X、Y向位置實現定制陣列架構。

設計者可以為相控陣中的每個天線陣元定義增益或全向輻射模式,這使得他們可以為內部、邊緣和角上的陣元選擇不同的輻射模式,這些模式能夠在實驗室測量得到,或者通過電磁仿真器進行計算,如用于平面電磁分析的AXIEM和3D有限元方法(FEM)分析的Analyst,這些都是NIAWR軟件自帶的仿真器。一種簡單的方法是采用3*3的相控陣并激勵其中一個陣元——內部陣元,或一個邊緣陣元,或一個角上陣元——并關閉其它陣元,從而分別得到內部、邊緣和角上陣元的輻射模式,這些模式都可以通過使用NIAWR軟件的輸出數據文件功能進行自動存儲。上述方法考慮到了一階近鄰陣元的相互耦合作用,如果要擴展到二階近鄰,可以采用5*5的陣列進行仿真。

VSS的另一個特點是可以對相控陣中獨立陣元之間的RF連接進行建模,這是一個非常重要的功能,因為RF連接并非理想,它會導致陣列行為嚴重偏離理想情況。舉個例子,相控陣中經常用到增益加權,但是,對于所有陣元都采用一樣的RF連接可能會導致某些特定的陣元(具有更高增益的陣元)工作在抑制區或其附近,而其他工作在線性區,陣列性能將受到陣元工作靠近抑制區程度的影響。反之,如果設計者根據所使用的增益加權模式,針對不同陣元選擇不同的RF連接,雖然會更加復雜,但能夠帶來更加有效的相控陣設計,而VSS建模就允許設計者做到這一點。

5結束語

隨著陣元數量和含電子器件天線集成度的提高,對獨立元件以及整個AESA雷達信號通路性能進行設計和驗證的能力變得不可或缺,通過使用集電路仿真、系統級行為建模和電磁分析于一體的設計平臺,開發團隊可以在昂貴的樣機研發之前對系統性能和元件之間的相互作用進行研究,能夠預測性能并修改RF設計以便滿足需求正是VSS建模功能所提供的能力之一。

-

雷達

+關注

關注

50文章

2937瀏覽量

117561 -

相控陣

+關注

關注

3文章

91瀏覽量

14171

原文標題:下一代有源相控陣雷達設計趨勢

文章出處:【微信號:ZGDZGCS,微信公眾號:電子萬花筒】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

下一代主流SiC IGBT模塊封裝技術研發趨勢——環氧灌封技術

相控陣雷達電源芯片詳解

下一代機器人技術:工業自動化的五大趨勢

24芯M16插頭在下一代技術中的潛力

下一代有源相控陣雷達的設計趨勢

下一代有源相控陣雷達的設計趨勢

評論