1.Pkg與PCB系統

隨著人們對數據處理和運算的需求越來越高,電子產品的核心—芯片的工藝尺寸越來越小,工作的頻率越來越高,目前處理器的核心頻率已達Ghz,數字信號更短的上升和下降時間,也帶來更高的諧波分量,數字系統是一個高頻高寬帶的系統。對于一塊組裝的PCB,無論是PCB本身,還是上面的封裝(Package,Pkg),其幾何結構的共振頻率也基本落在這一范圍。不當的電源供應系統(PDS)設計,將引起結構共振,導致電源品質的惡化,造成系統無法正常工作。

此外,由于元器件密度的增高,為降低系統功耗,系統普遍采用低電壓低擺幅設計,而低電壓信號更容易受到噪聲干擾。這些噪聲來源很廣,如耦合(coupling)、串擾(Crosstalk)、電磁輻射(EMI)等,但是最大的影響則來自于電源的噪聲,特別是同步切換噪聲(Simultaneous switching noise,SSN)。

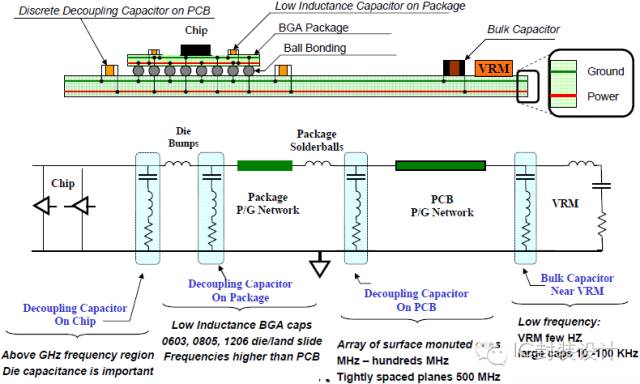

通常整個PDS系統除了包含電路系統外,也包含電源與地平面形成的電磁場系統。下圖是一個電源傳輸系統的示意圖。

圖1 典型的電源傳輸系統示意圖

2.Pkg與PCB系統的測量

一般在探討地彈噪聲(GBN)時,通常只單純考慮PCB,且測量其S參數|S21|來表示GBN大小的依據。Port1代表SSN激勵源的位置,也即PCB上主動IC的位置,而較小的|S21|代表較好的PDS設計和較小的GBN。然而一般噪聲從IC上產生,通過Pkg的電源系統、再通過基板Via和封裝上的錫球的連接,到達PCB的電源系統(如圖1)。所以不能只單純考慮PCB或Pkg,必須把兩者結合起來,才能正確描述GBN在高速數字系統中的行為。

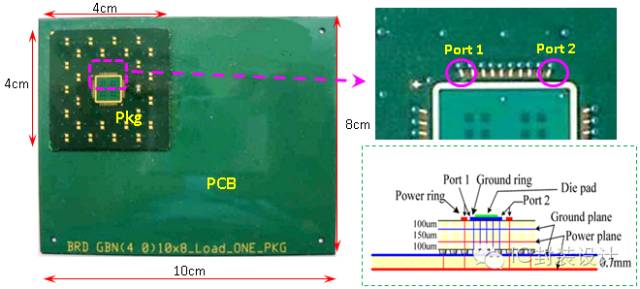

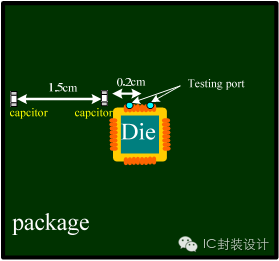

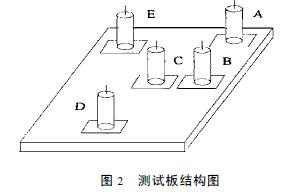

為此,我們設計一個PDS結構(如圖2),來代表Pkg安裝在PCB上的電源系統。

圖2 BGA封裝安裝在PCB上的結構和截面示意圖

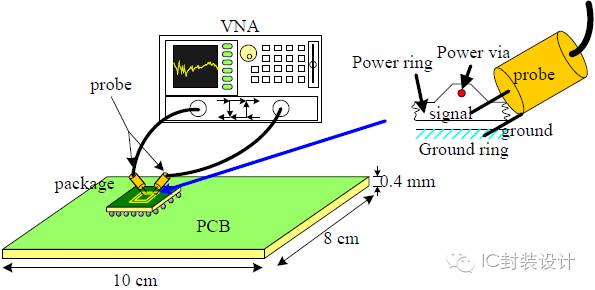

使用網絡分析儀(HP8510C)結合探針臺(Microtechprobe station),量測此結構之S參數,從50Mhz到5Ghz。測量上,使用兩個450um-pitch的GS探針,接到Pkg信號層的Powerring和Ground ring上。這個測量結構如圖3。

圖3 BGA封裝安裝在PCB上的結構測量示意圖

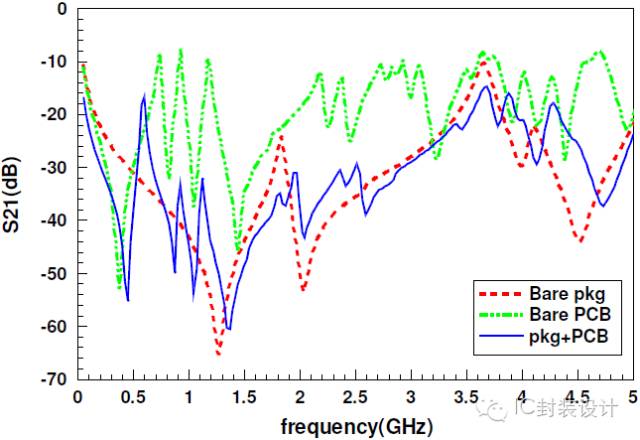

Pkg+PCB結構量測S參數的結果如圖4所示,同時我們也做了單一Pkg和 PCB的量測結果,通過對比來了解整個PDS系統和單一Pkg和PCB之間的差別。

圖4 BGA封裝安裝在PCB上的量測結果

從圖4的測量結果,我們可以考到三種結構的GBN行為有很大的差異。首先考慮只有單一Pkg時的S參數,在1.3Ghz之前的行為像一個電容,在1.5Ghz后才有共振模態產生;考慮單一PCB,在0.5Ghz后就有共振模態產生,像0.73Ghz(TM01)、0.92Ghz(TM10)、1.17Ghz(TM11),其GBN行為比單一Pkg更糟。最后,考慮Pkg結合PCB,可以看到在1.5Ghz之前,比單一Pkg多了三個共振點,這些噪聲共振來自于PCB,通過錫球、Via等耦合到Pkg的電源上,這會使Pkg里的IC受噪聲影響更嚴重,這跟只考慮單一Pkg或PCB時有很大不同。

3.去耦電容對電源噪聲的影響

對于電源平面噪聲傳統的抑制方法是使用那個耦合電容,對于去耦電容的使用已有很多研究,但電容大小、位置、以及個數基本還是基于經驗法則。

去耦電容的理想位置

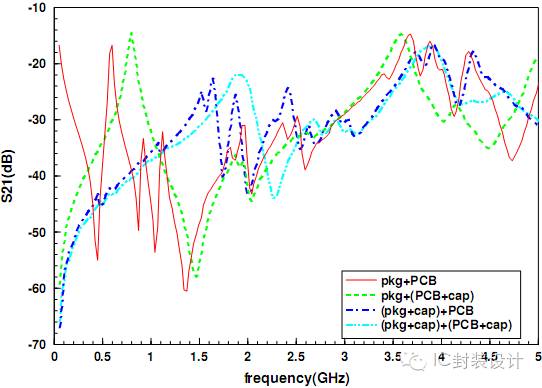

為了研究去耦電容位置PDS的影響,我們用上述Pkg+PCB結構,分別在Pkg和PCB上加去耦電容或兩者都加上去耦電容,通過量測|S21|來研究去耦電容的理想擺放位置。

圖5 去耦電容安裝在Pkg和PCB上

如圖5所示,我們擺放電容的位置分三種情況,一是在Pkg上加52顆,二是在PCB上加63顆,三是在Pkg和PCB上同時各放置52和63顆,電容值大小為100nF, ESR、ESL分別為0.04ohm、0.63nH。量測結果如圖6。

圖6 加去耦電容于不同位置的|S21|比較圖

首先,把低頻到5Ghz分成三個階段,首先,開始低頻到500Mhz左右,不管在Pkg或PCB上加去耦電容,相比沒有加電容,都可以大大降低結構阻抗,減少GBN干擾。第二,對于0.5Ghz~2Ghz,在Pkg上和同時在Pkg與PCB上加去耦電容,對噪聲抑制效果差不多。可是如果只在PCB上加電容,可以看到在800Mhz附近多了一個共振點,這比沒有加電容時更糟。所以我們只在PCB上加電容時要特別注意,可能加上電容后電源噪聲更嚴重。第三,從2Ghz~5Ghz,三種加電容方式與沒加電容相比,效果并不明顯,因為此階段超過了電容本身的共振頻率,由于電容ESL的影響,隨著頻率升高,耦合電容逐漸失去作用,對較高頻的噪聲失去抑制效果。

去耦電容ESR的影響

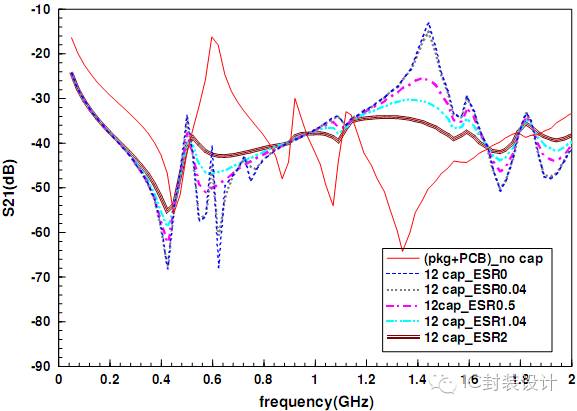

在Pkg結合PCB結構上,放置12顆去耦電容,同時改變去耦電容的ESR,模擬結果如圖7所示。可以發現,當ESR值越來越大,會將極點鏟平,同時零點也被填平,使S21成為較為平坦的曲線。

圖7 去耦電容的ESR對|S21|的影響

去耦電容ESL的影響

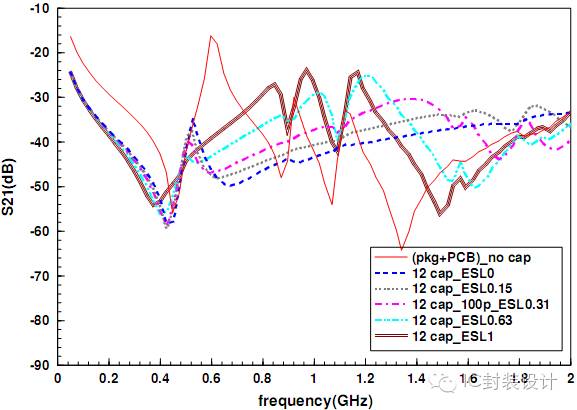

在Pkg結合PCB結構上,放置12顆去耦電容,同時改變去耦電容的ESL,模擬結果如圖8所示。從圖中我們發現,ESL越大,共振點振幅越大,且有往低頻移動的趨勢,對噪聲的抑制能力越低。

圖8 去耦電容的ESL對|S21|的影響

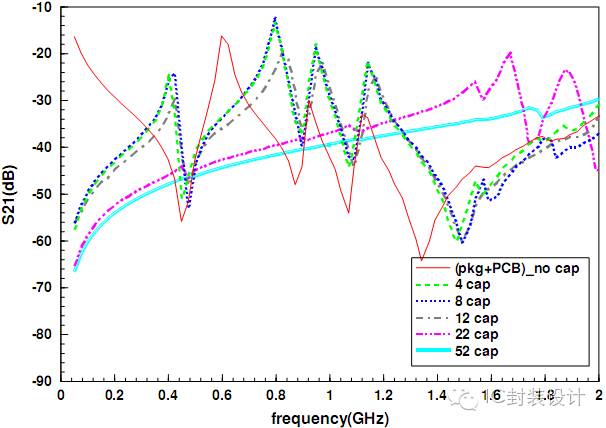

去耦電容數量的影響

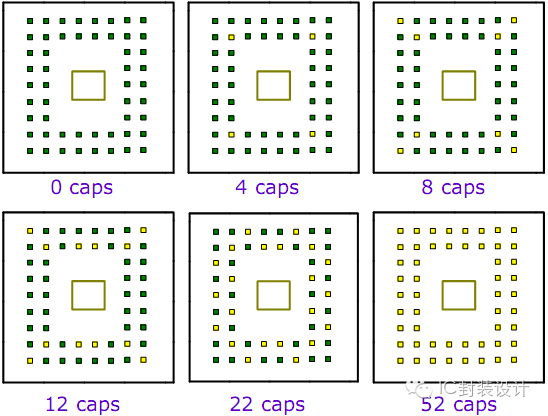

由前面的結果知道,電容放在封裝上效果更好,所以對電容數量的探討,以在Pkg上為主。在前述Pkg+PCB的結構上,Pkg上電容的放置方式如圖9,模擬結果如圖10。

圖9 封裝上電容的放置位置

圖10 電容數量對|S21|的影響

從測量結果可知,加4和8顆時,在0~200Mhz,能有效壓低|S21|,但在400Mhz附近產生新的共振點,而把之后的共振點往高頻移動。當加入12~52顆后,同樣壓低低頻|S21|,且把400Mhz附近的共振點大大消減,高頻共振點向高頻移動,且振幅大為縮減。

隨著電容數量增加,對噪聲的抑制更好,從4~8顆的300Mhz,提升到1.2Ghz(52顆),所以增加電容數量,有助于對提高電源的噪聲抑制能力。

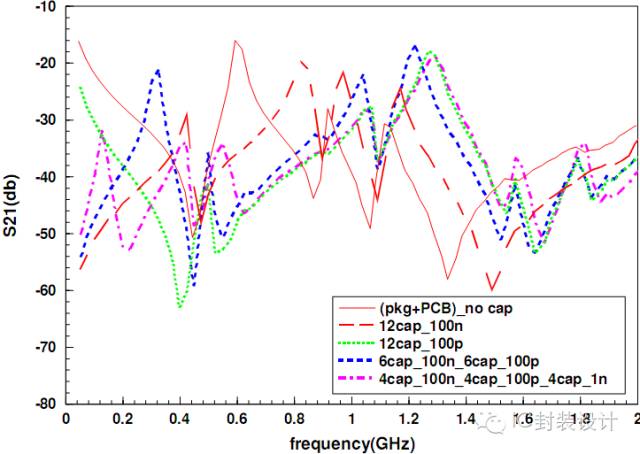

去耦電容容值的影響

在Pkg和PCB的組合結構上,放置不同容值的電容,模擬結果如圖11。

對加入100nF和100pF做比較,0~300Mhz間,100n大電容有較好的抑制效果;500~800Mhz,100p小電容有較好的效果;而加100n電容,會跟整個系統結構在400Mz產生共振;當使用100n+100p,200~600Mhz,比單純使用100n和100p差,而更低頻或更高頻也沒有單一容值好;當使用100n+1n+100p三種容值時,產生了更多共振點,在電子系統中要特別小心,如果電路產生的噪聲剛好在共振頻率點,則噪聲被放大,對信號產生影響或輻射。

所以對電容容值的選擇,應根據要抑制的頻段來決定,頻段決定后根據電容的共振點選擇電容,越低的電容ESL和ESR越好。

圖11 混合不同容值電容的模擬結果

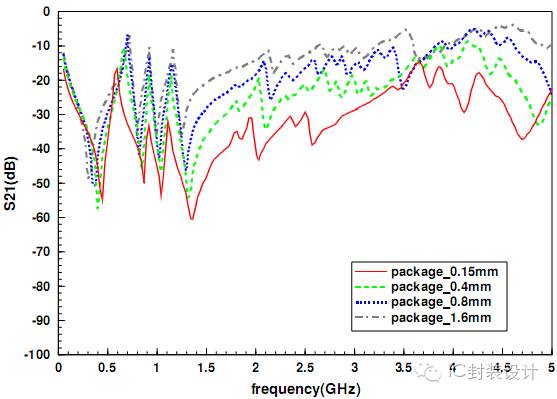

板層厚度的影響

首先,固定PCB電源與地平面之間的距離為0.7mm,改變Pkg電源層厚度依次為1.6mm、0.8mm、0.4mm、0.15mm,結果如圖12所示;當Pkg電源層厚度越來越高,第一個零點向低頻移動;從前面結論知道,2Ghz前的噪聲來自PCB,從結果來看PCB耦合上來的噪聲也變大了,而2Ghz以后主要受封裝影響,可以看到|S21|也隨厚度而變大,所以Pkg電源平面的厚度對S參數影響是很大的。

圖12 不同Pkg電源層厚度對|S21|的影響

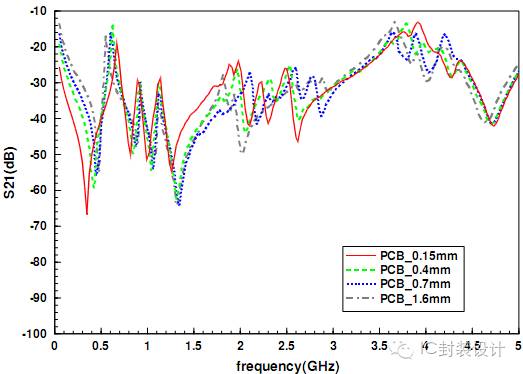

接著,我們固定Pkg厚度為0.15mm,分別改變PCB厚度為0.15mm、0.4mm、0.8mm、1.6mm,PCB厚度對S參數的影響結果如圖13所示,可以看到PCB電源層厚度對整體趨勢影響并不大,只有低頻部分少有差異,厚度增加第一個零點小高頻移動,高頻部分只稍有差異。

圖13不同PCB電源層厚度對|S21|的影響

電容擺放距離的影響

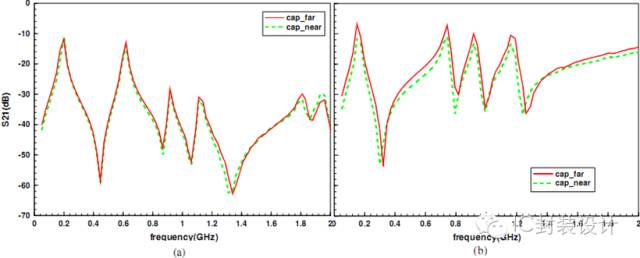

我們知道去耦電容的位置距離噪聲源越近越好,因為能減少電容到噪聲源之間的電感值,讓電容更快的吸收突波,降低噪聲,達到穩定電壓的作用。同樣降低電源層厚度能減小電源平面寄生電感,也能起到相同作用。在模擬上我們改變電容在封裝上和測試點之間的距離,分別為1.7cm和0.2cm,Pkg和PCB電源層厚度分兩種情況,第一種Pkg 0.15mm和PCB 0.7mm,第二種情況,Pkg1.6mm和PCB 0.7mm,電容100nF、ESR 0.04ohm、ESL 0.63nH。

圖14 電容與測試點的距離

圖15不同電容與測試點的距離|S21|模擬結果

由模擬結果得知,當因為封裝結構或繞線問題,不能把電容放置在噪聲源附近是,我們可以藉由減低Pkg電源層厚度,減少噪聲的影響。

4.結 論

最后,我們對高速數字電路如何中抑制噪聲做一總結。首先,去耦電容的理想位置是放置在Pkg上;ESR增大雖能把極點鏟平,但也會導致共振頻率深度變淺,電容充放電時間增大,會失去降低電源平面阻抗的功能;電容ESL增大會加快共振點后阻抗上升速度,所以ESL越低越好;電容數量越多越好,電容墻可以提高隔離效果;電容容值的選擇,需要根據噪聲頻段來選擇,盡量不要多容值混用,雖然這樣能增加噪聲抑制的頻寬,但也會增加共振點數量,如果噪聲剛好落在共振點上,疊加的效果可能會更嚴重;PCB電源平面厚度對Pkg上的S參數幾乎沒有影響,但在低頻,Pkg上板層厚度卻會影響PCB耦合上來的噪聲大小,Pkg板層越薄耦合上來的噪聲越小;高頻部分,主要受封裝影響,Pkg板層越薄,|S21|值越小。

-

pcb

+關注

關注

4322文章

23126瀏覽量

398572 -

數字電路

+關注

關注

193文章

1608瀏覽量

80689 -

去耦電容

+關注

關注

11文章

316瀏覽量

22413

原文標題:高速數字電路封裝電源完整性分析

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速數字電路設計與噪聲控制技術

數字電路中△I噪聲產生過程與其基本特點簡介及主要危害分析

總結高速數字電路如何抑制噪聲

總結高速數字電路如何抑制噪聲

評論