以下文章來源于慧智微電子 ,作者小慧

01如何僅通過EM仿真SNP文件獲取傳輸線特征阻抗?

Q:請(qǐng)問目前通過EM仿真得到傳輸線的SNP文件,僅有這個(gè)的情況下能仿真得到傳輸線的特征阻抗嗎?

A:一般來講,只在這個(gè)端口加Term,然后設(shè)置這個(gè)Term的阻抗為Zo, 之后掃描Zo, 看什么時(shí)候,這個(gè)端口的反射系數(shù)最小。這時(shí)候的Zo,就是特征阻抗。(但是需要考慮其它的端口怎么連接--這是一個(gè)問題)。如果是兩端口,兩個(gè)端口的連接傳輸線是一樣的。那就加兩個(gè)Term,兩個(gè)Term的阻抗都設(shè)置為Zo.....

Q:好的,謝謝你,我這就去試試。

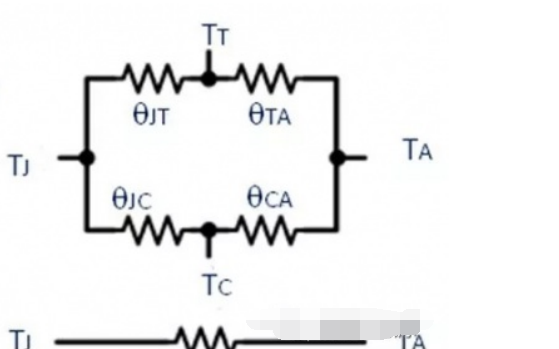

02電源芯片耗散功率與結(jié)溫關(guān)系的探討

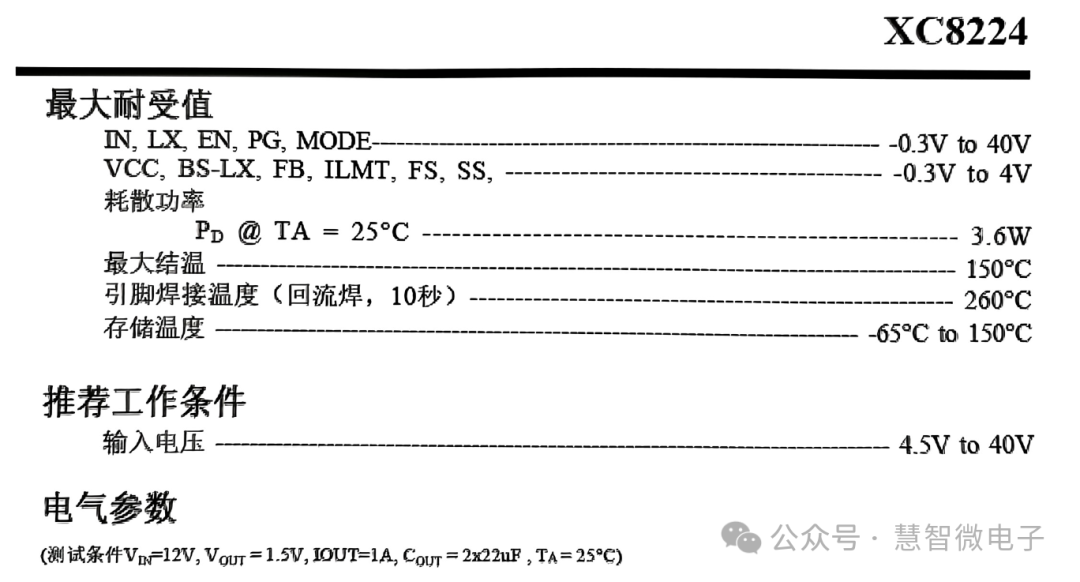

Q:請(qǐng)問下有人了解,電源芯片這個(gè)耗散功率是在結(jié)溫150°C下算出來的嗎?

A:不是,超過結(jié)溫,pn結(jié)損壞。

Q:那他這個(gè)耗散功率是,結(jié)溫多少的時(shí)候測(cè)出來的?

A:最大結(jié)溫一般是晶元廠測(cè)出來的吧。實(shí)際上使用器件也不關(guān)心結(jié)溫多少,也很難測(cè)出來。只要散熱夠好就ok。做什么產(chǎn)品啊,這么糾結(jié)功耗與結(jié)溫的關(guān)系。

Q:因?yàn)樗唤o了個(gè)耗散功率,想算他的熱阻,之前一版85度時(shí)電源自保護(hù)了,所以想先預(yù)算一下。

A:你說的這個(gè)耗散功率應(yīng)該是滿載工作時(shí)的最大熱耗。

可靠性考慮,半導(dǎo)體芯片針對(duì)結(jié)溫(TJ)規(guī)定了安全上限,通常為150°C(有時(shí)為175°C)。

裸芯片,結(jié)溫可以用顯微紅外熱像儀測(cè)試。封裝好的芯片熱阻,可以用熱阻測(cè)試儀(如t3ster)測(cè)試。

Q:好的,謝謝,多找了幾份規(guī)格書反推了一下,有的是125度,有的是150度。所以按150度推算熱阻系數(shù)保守一點(diǎn)。

03包絡(luò)阻抗、基波阻抗與二次諧波阻抗的差異

Q:請(qǐng)問大家一個(gè)問題,包絡(luò)阻抗是什么意思,和我們的基波阻抗,二次諧波阻抗區(qū)別在哪?

A:我理解包絡(luò)阻抗應(yīng)該是雙音信號(hào)或?qū)拵盘?hào)才有的概念,基波阻抗和諧波阻抗不論單音雙音和寬帶都要考慮。譬如有兩個(gè)雙音信號(hào)f1和f2,那它們的包絡(luò)阻抗就是(f1-f2)和(f2-f1)頻點(diǎn)處的阻抗,是寬帶信號(hào)記憶效應(yīng)的主要來源,可以參考下慧智微公眾號(hào)之前有篇講記憶效應(yīng)的文章。

Q:?好的,謝謝哥,我看下文章。

04功率檢測(cè)器指標(biāo)與插入損耗的關(guān)系

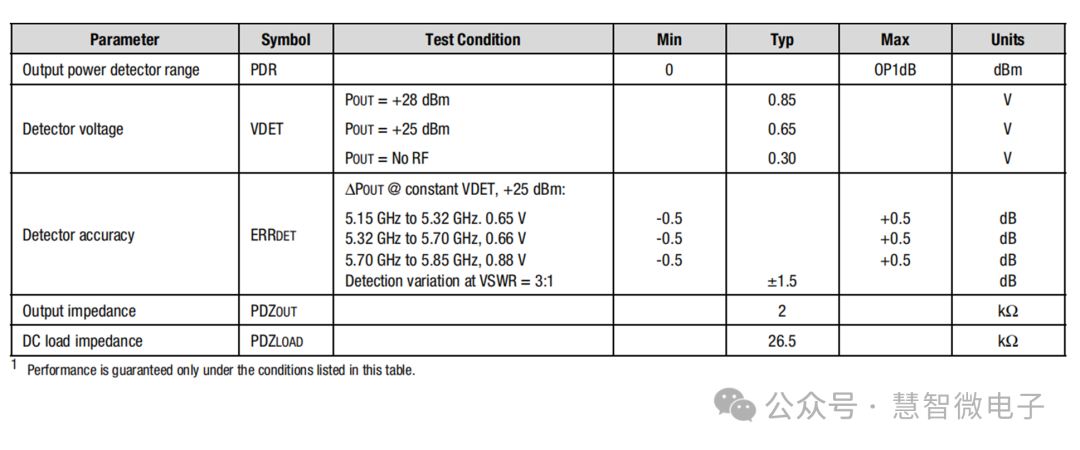

Q:有人了解功率檢測(cè)器指標(biāo)嗎,這個(gè)檢測(cè)的準(zhǔn)確度(dB)是對(duì)主路的的插入損耗嗎?

A:圖片里這是耦合功率再經(jīng)過檢波電路后的規(guī)格。

“有人了解功率檢測(cè)器指標(biāo)嗎,這個(gè)檢測(cè)的準(zhǔn)確度(dB)是對(duì)主路的的插入損耗嗎?”這里的檢測(cè)準(zhǔn)確度應(yīng)該是這樣理解:在檢測(cè)電壓為0.65v時(shí),對(duì)應(yīng)的輸出功率在25dBm+-0.5dB。

Q:一下子就懂了,感謝大佬。

05電源線對(duì)ACLR影響分析及改進(jìn)措施

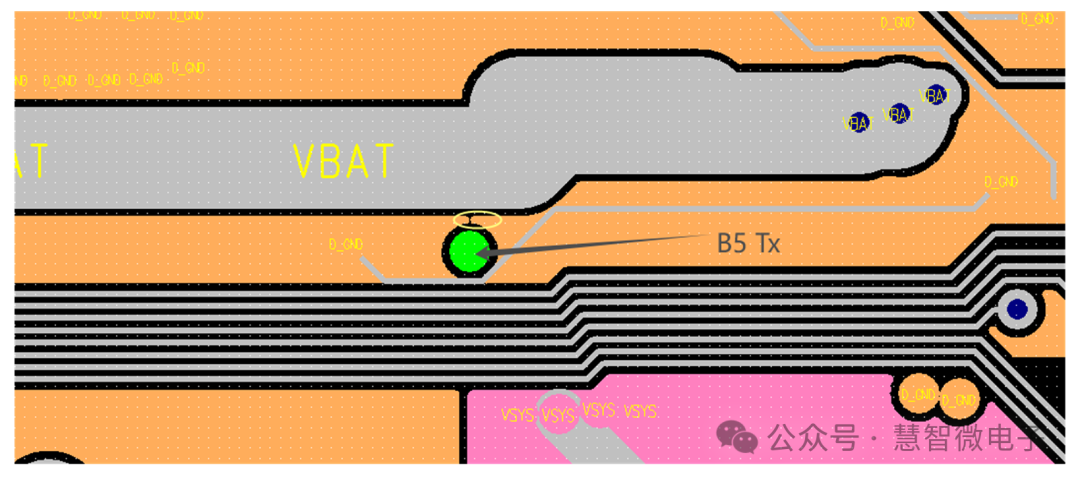

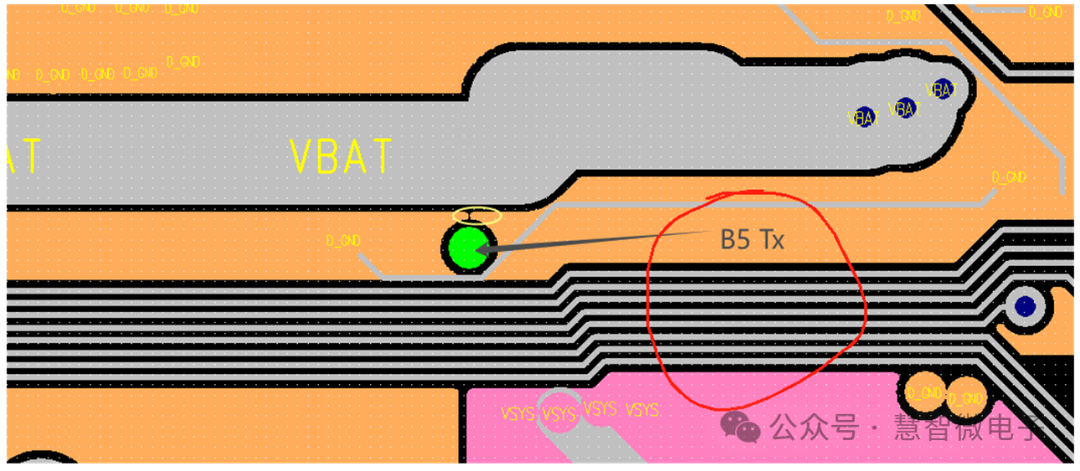

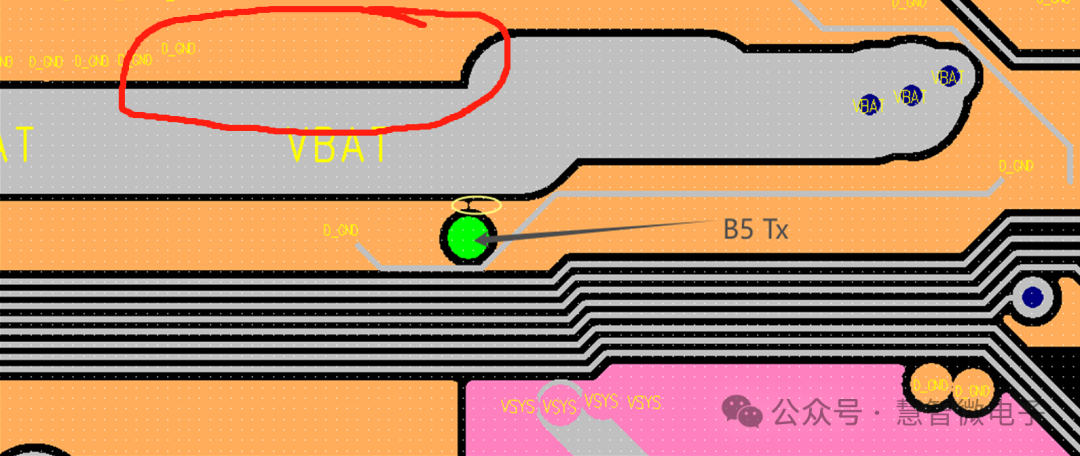

Q:B5 Tx走線這里包地沒做好的話,會(huì)被影響到ACLR嗎?

A:會(huì),靠電源這么近的嘛,要多打低孔了哦。

Q:ACLR直接掉到20了。

A:這些是什么線?

A:旁邊電源啊。

A:不會(huì)有耦合嗎?

就算地連起來了也會(huì)有影響,VBAT線應(yīng)該可以網(wǎng)上移動(dòng)一點(diǎn),然后中間打地孔呢。

Q:ok,叫人改一下,感謝大佬。

A:記得電源線和那個(gè)孔之前一定要用地孔隔開,要不還會(huì)被影響

Q:好的,為啥會(huì)被電源線影響啊?B5Tx 800MHz。

A:電能轉(zhuǎn)磁能唄。

A:電源有噪聲。

Q:是把E-UTRA1的底噪抬太高了嗎?

A:不是底噪。差的電源在被抽取電流的時(shí)候,會(huì)產(chǎn)生紋波。

Q:多謝大佬們解惑。

06功率檢測(cè)電路設(shè)計(jì)與仿真中的關(guān)鍵因素探討

Q:有人了解功率檢測(cè)電路的運(yùn)行規(guī)則嗎?是不是 PA 正常工作的時(shí)候不開啟,當(dāng) PA 出現(xiàn)異常就檢測(cè)功率(??ω??)?

A:回環(huán)檢測(cè)功率,CLPC校準(zhǔn),WIFI是這么用的。

Q:太深?yuàn)W,沒太明白。

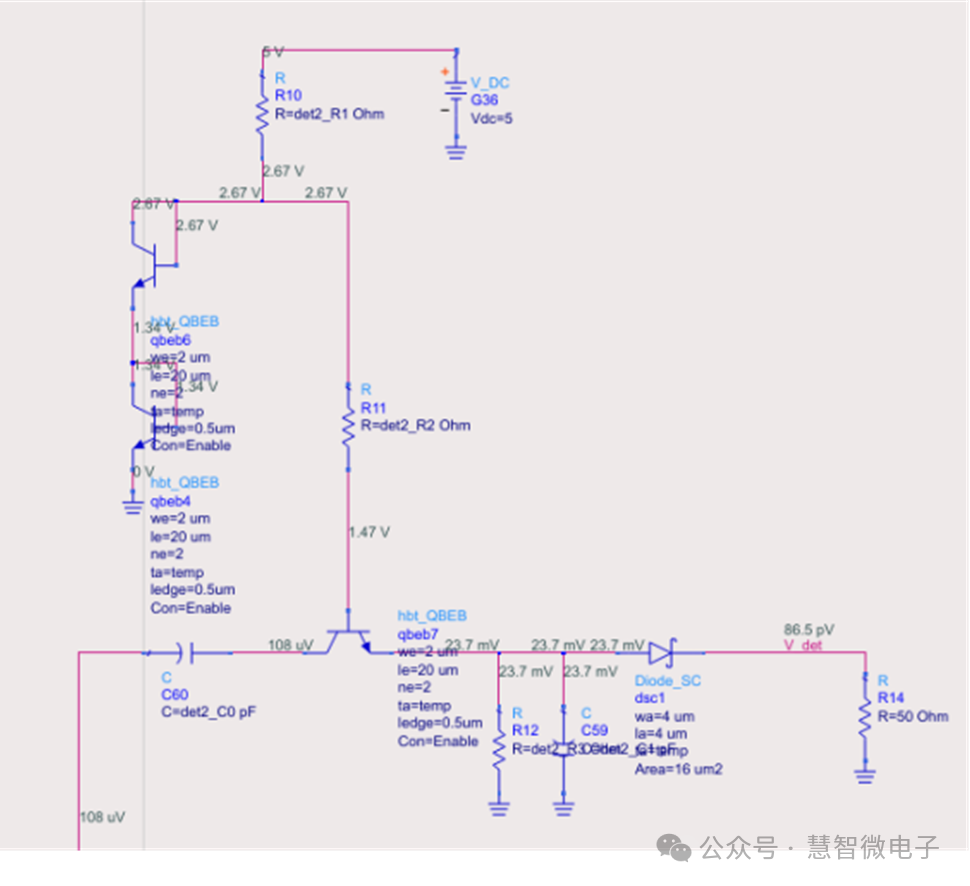

A:你就當(dāng)這個(gè)det當(dāng)成一個(gè)二極管。

Q:但設(shè)計(jì)的時(shí)候,不需要考慮檢測(cè)電路對(duì)這個(gè)的影響嗎?我仿真出來,加了檢測(cè)電路直接調(diào)了幾個(gè) dB。

A:那說明det吸收的功率太大,電路問題。

A:檢波器嗎?檢波器的話可以耦合一個(gè)線圈出來。

Q:這是我參考的電路,主要的影響還是這個(gè)耦合電容的問題,電容太小,檢測(cè)的電壓變化不大,電容太大,檢測(cè)的電壓正常,但對(duì)主路的影響很大。

A:主路耦合出來。

Q:耦合電容不行嗎?

A:做檢波器是為了做包絡(luò)跟蹤嗎?

Q:wifi-pa的功率檢測(cè),是不是包括跟蹤的話,不是特別清楚。

A:一般0.5dB,放在級(jí)間。

Q:我是吧級(jí)間和這個(gè)放在一起仿真,但損耗太大了,要不就是檢測(cè)的功率,不太對(duì)。

A:電路問題,自己想想。

Q:有沒有那種講關(guān)于這個(gè)功率檢波電路的資料什么的,感覺我現(xiàn)在已經(jīng)暈了。

A:有個(gè)log det的。好像,ieee搜一下。

Q:okok,多謝大佬。

07ADS模板仿真FT與Fmax遇到的問題及解決方法

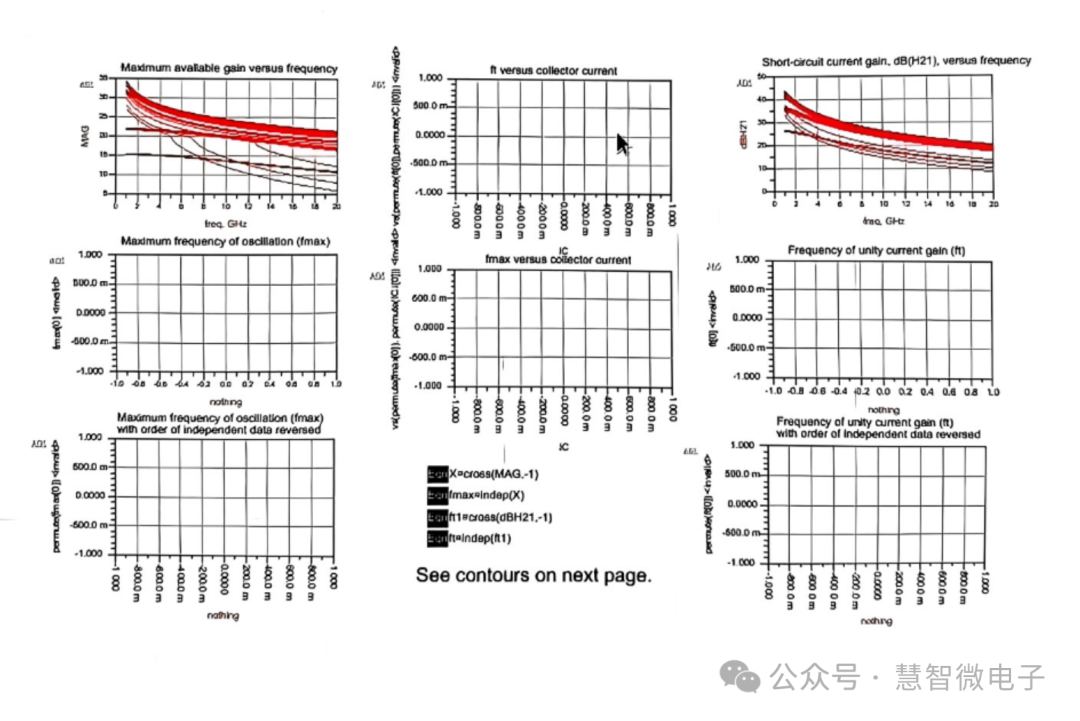

Q:有大佬用過ADS模板仿真ft與fmax,替換掉原來bjt,后沒有仿真結(jié)果呢?

A:好好研究,沒啥問題。

Q:啊?

A:看看下面的公式,分析下ADS怎么仿真ft和fmax的,你就知道為啥沒數(shù)據(jù)了。

Q:嗯嗯好嘛,從這個(gè)X開始就沒數(shù)據(jù)了。

A:哎,你把原理圖的頻率設(shè)置高一點(diǎn),300g。

Q:好嘛,多謝多謝。

08如何在芯片測(cè)試中去嵌PCB影響并精確評(píng)估芯片性能

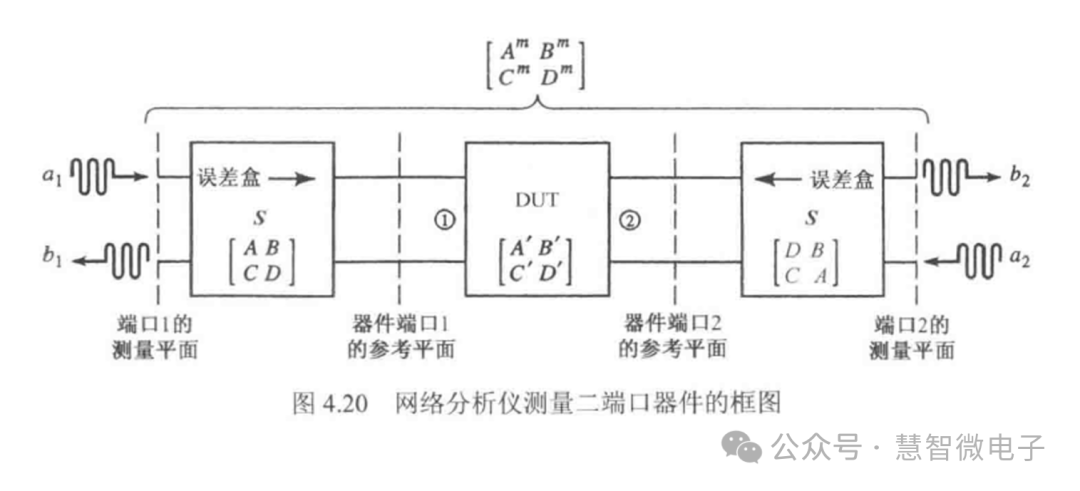

Q:咨詢一下各位大佬,一般芯片測(cè)試都是要焊接在PCB上去測(cè)試,但這會(huì)引入PCB的影響(比如損耗等),怎么能在測(cè)試中盡可能去除PCB的影響、只考察芯片本身的性能呢?

A:去嵌,你可以在你測(cè)試的PCB上做TRL校準(zhǔn)的校準(zhǔn)件然后測(cè)試的時(shí)候用TRL校準(zhǔn)去嵌就可以測(cè)試到芯片端面了。

A:去嵌入,AFR會(huì)方便一點(diǎn)。

Q:類似于這樣的原理是嗎?PCB板相當(dāng)于這里的誤差盒?

我看《微波工程》這里講TRL校準(zhǔn)是可以將校準(zhǔn)件和被測(cè)件級(jí)聯(lián),就是構(gòu)造成3個(gè)二端口網(wǎng)絡(luò)的級(jí)聯(lián),但實(shí)際的芯片是和PCB板焊在一起(PCB板上還可能有接地通孔),我就是不懂那這樣的話PCB板怎么做校準(zhǔn)件呢?

A:一般會(huì)按照PCB專門做一塊校準(zhǔn)板。

你這種夾具不好拆裝的,那就是做前處理比較合適,做個(gè)TRL校準(zhǔn)板。

Q:哦哦,好吧感覺我自己好像想復(fù)雜了。

A:你要做一塊一摸一樣的pcb做你的校準(zhǔn)件的,國外好像有人專門做這個(gè)的。

A:看看xiaoning ye的文章吧,講的很清楚。

Q:好的多謝各位大俠。

09負(fù)載牽引與功率效率圓分析及匹配策略

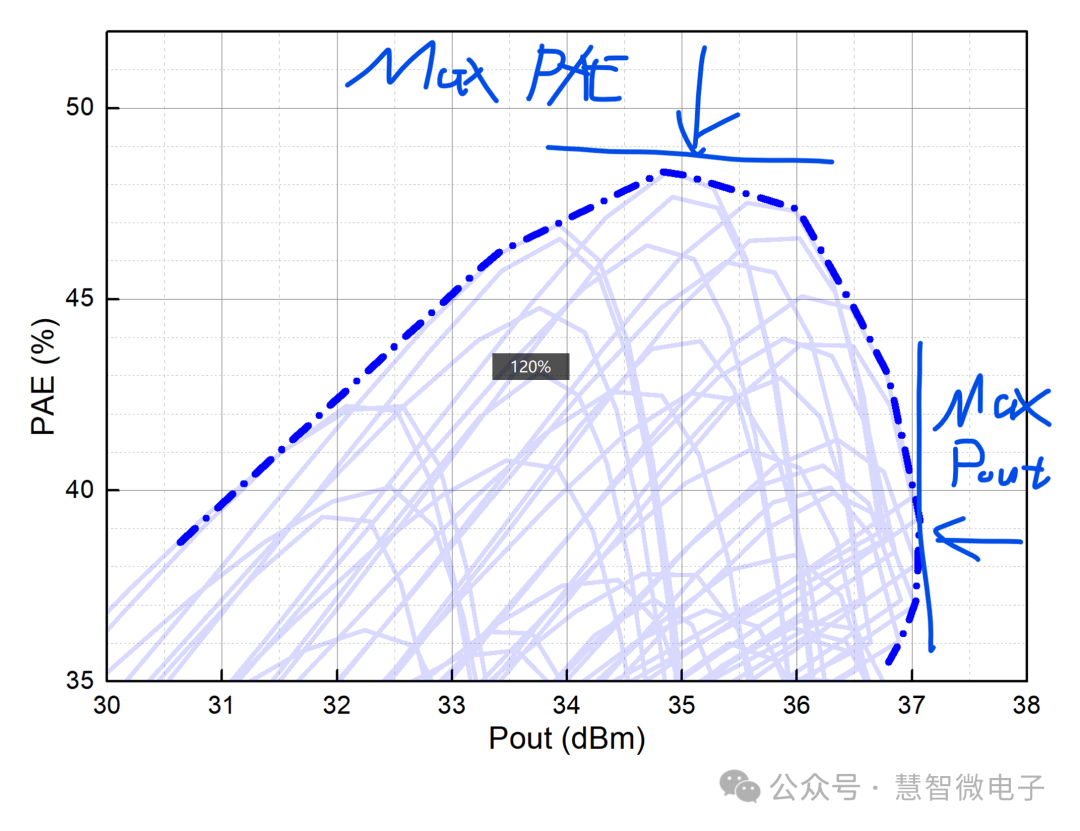

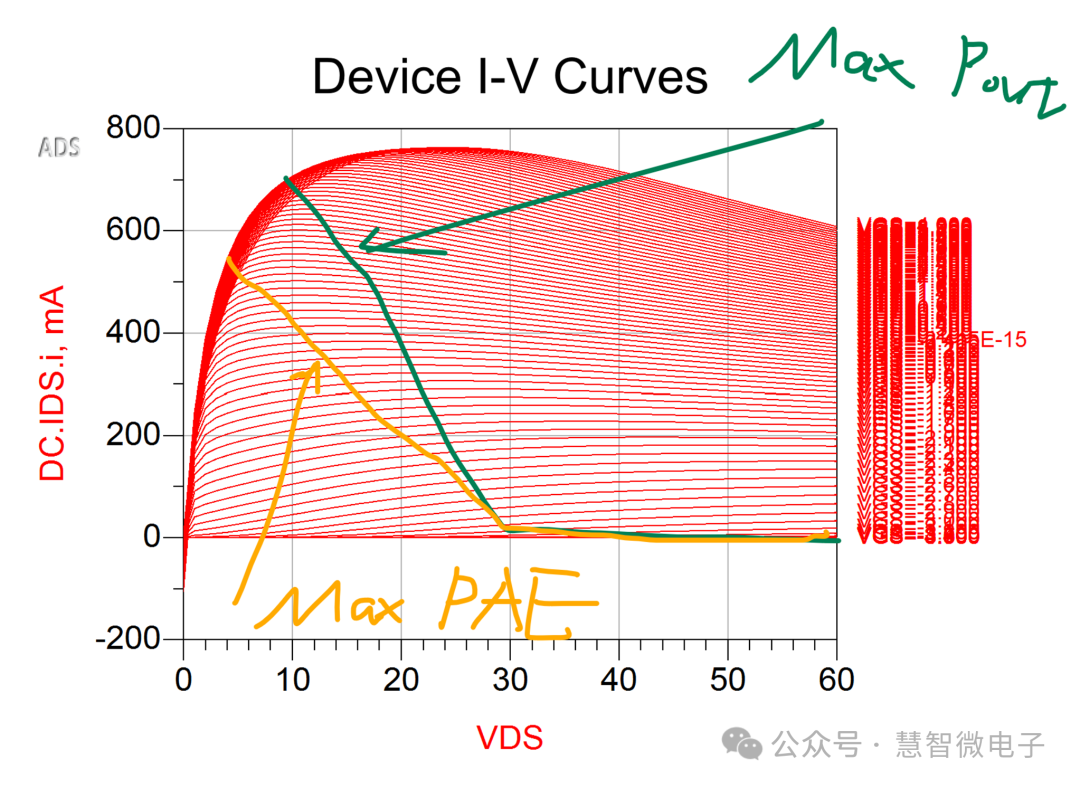

Q:求問:負(fù)載牽引得到的功率圓和效率圓為什么會(huì)錯(cuò)開,而不是重疊在一起。

A:好問題!

A:膝點(diǎn)電壓吧?

A:對(duì)的。

Q:可以展開一下嗎?大佬

A:從負(fù)載線的角度考慮唄。

Q:這個(gè)膝點(diǎn)電壓和模集里的過驅(qū)動(dòng)電壓是一個(gè)意思么?

A:顯然不是。

Q:應(yīng)該是i-v曲線里的那個(gè)Vknee吧?

A:膝點(diǎn)電壓是Vds的電流開啟電壓,過驅(qū)動(dòng)電壓是Vgs的電流開啟電壓。

A:就是功率管從線性區(qū)進(jìn)入飽和區(qū)的拐點(diǎn)電壓。

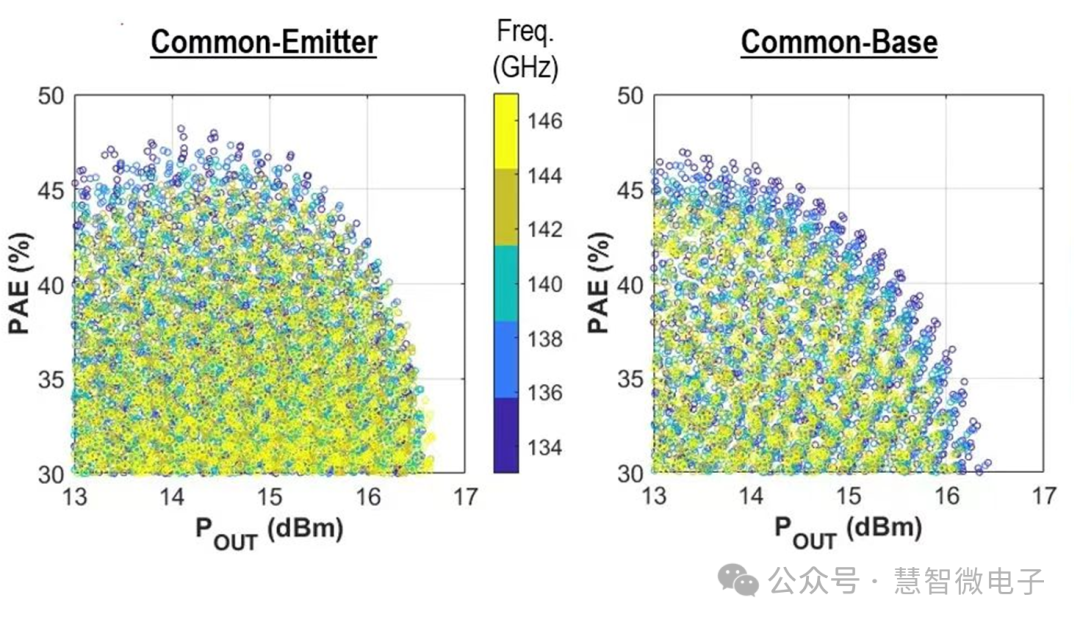

Q:前輩能詳細(xì)講講嗎?效率和功率圓怎么分析的。

A:那這數(shù)值上不就是過驅(qū)動(dòng)電壓么,就是飽和區(qū)那個(gè)分界電壓?jiǎn)h。哦沒事了,CMOS對(duì)線性飽和區(qū)的定義和模電不一樣。

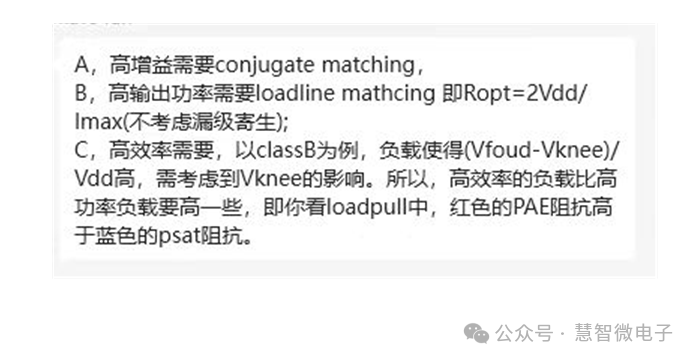

A:負(fù)載線匹配得最大功率,共軛匹配得最大效率,牽引的阻抗不同,在Smith圓上的位置不同。

A:共軛匹配不是最大功率傳輸嗎?還是我記錯(cuò)了。

Q:不是吧共軛匹配不是s11 s22最好嗎?

A:是最大功率傳輸,所以增益應(yīng)該是最大的。

A:共軛是讓功率最大化傳輸。

Q:嗷嗷但是小信號(hào)增益最大的話輸出功率也會(huì)最大嗎?

A:不會(huì)啊,這個(gè)共軛的阻抗大概率不是loadpull負(fù)載線出來的Zopt。

A:Zopt應(yīng)該是最大功率。

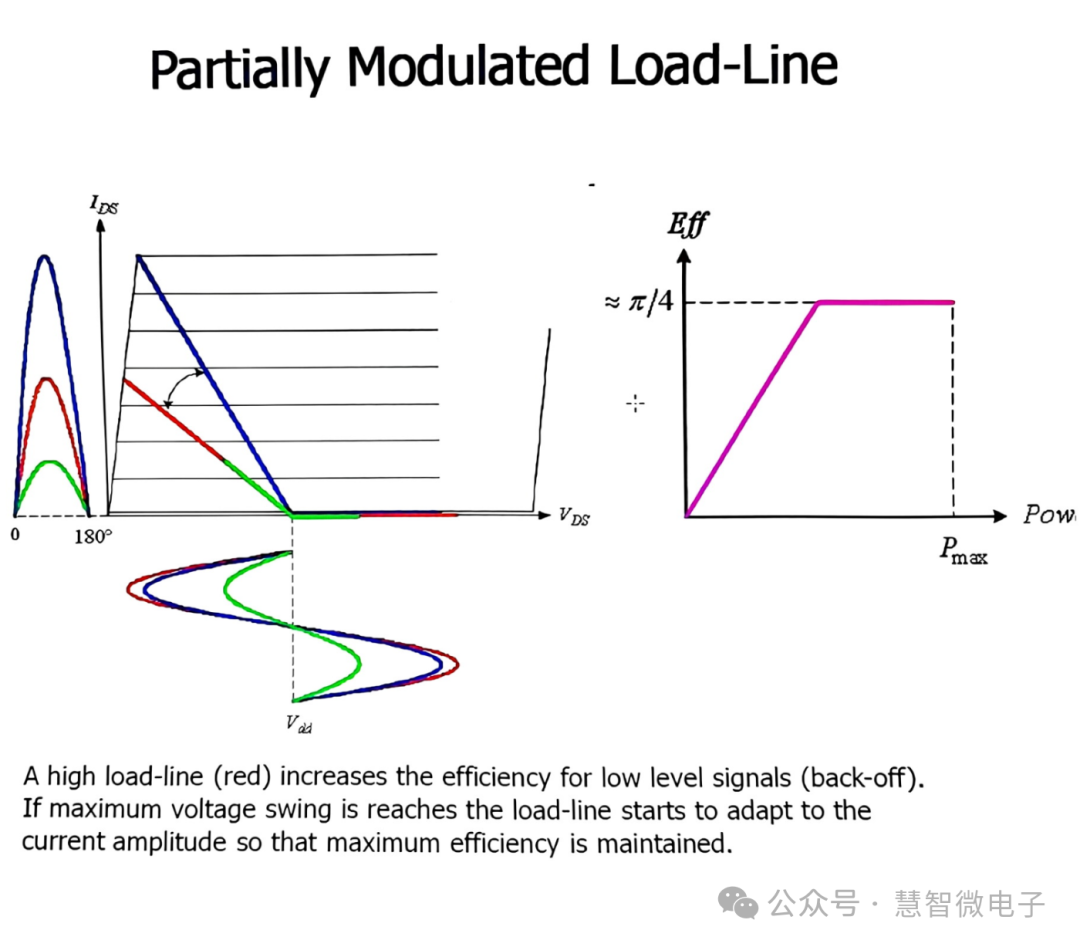

A:解釋功率圓心和效率圓心不重合的原因:

A:之前看到的一張圖:

Q:對(duì)于單級(jí)PA,高功率=高增益吧;power match獲得的最大輸出功率點(diǎn),就是最高增益點(diǎn)?所以這里的A和B說法有矛盾嗎?當(dāng)然,高功率不等于高效率;

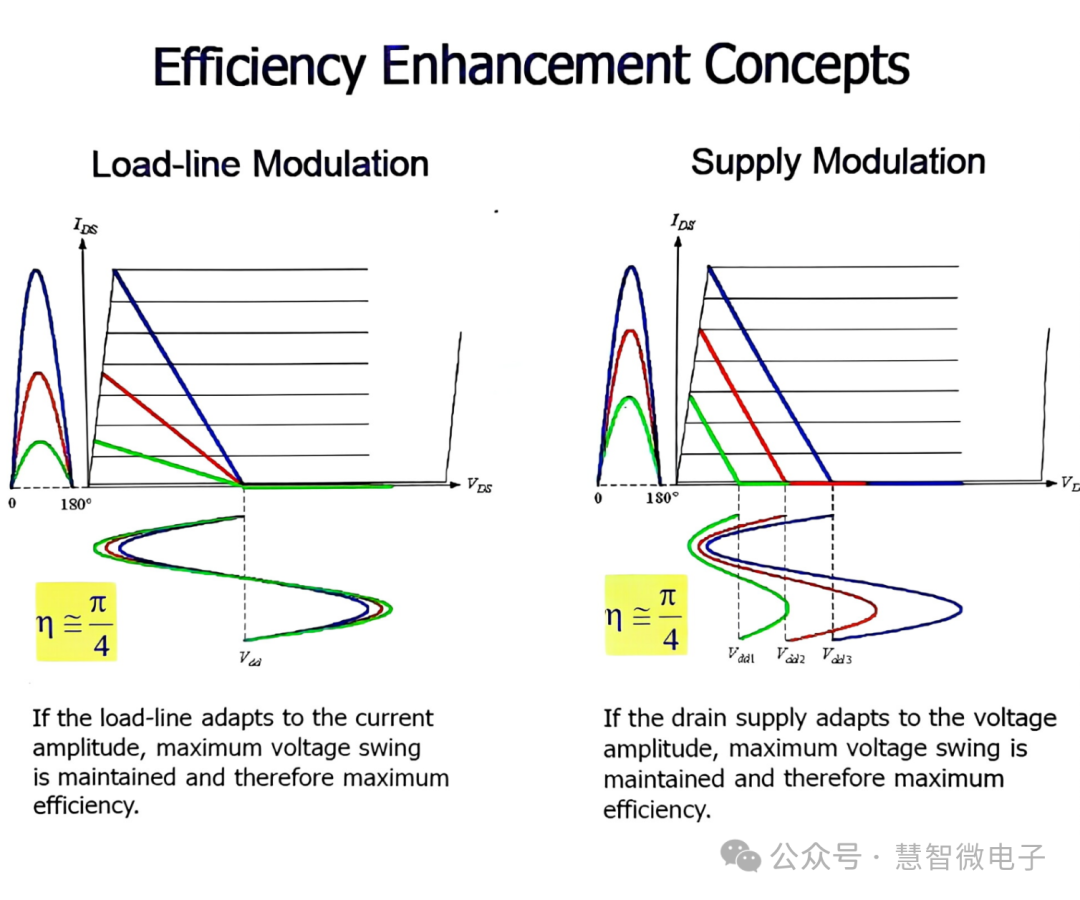

A:這張圖很明顯了,

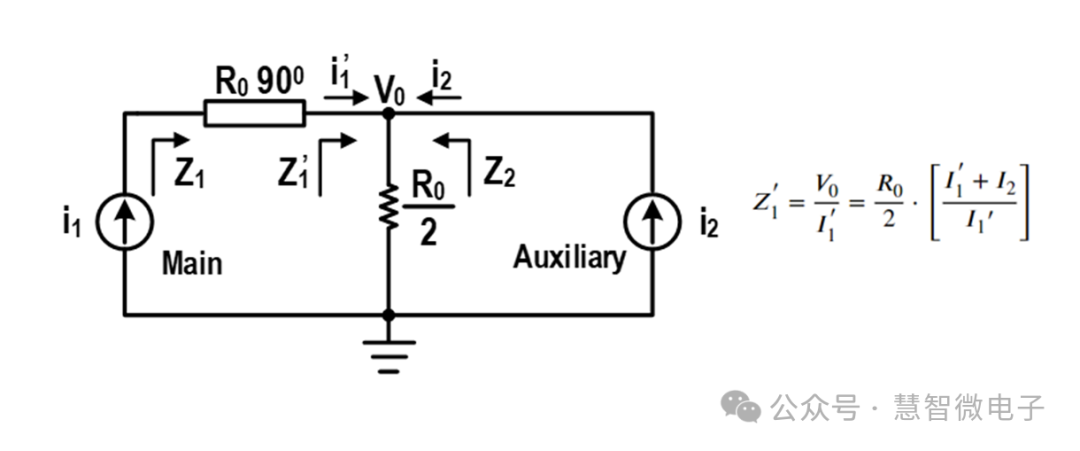

這就是負(fù)載調(diào)制

Q:是的,這張圖上,小功率下,共軛匹配下增益和輸出功率比power match的要大;但是飽和輸出時(shí),比不上power match的輸出功率;

A:個(gè)人理解負(fù)載調(diào)制是個(gè)廣泛的說法,這里的調(diào)制和doherty的負(fù)載調(diào)制不是一個(gè)東西。

A:簡(jiǎn)單來說,負(fù)載調(diào)制就是電流源控制電壓源端口看到的負(fù)載。

A:最大功率和最大PAE的圓心一般不會(huì)重合的,這個(gè)圖就能說明問題。

A:因?yàn)镻AE考慮了增益,而功率就只考慮了功率本。

A:對(duì)滴。

A:單級(jí)負(fù)載牽引增益對(duì)效率還是有點(diǎn)影響,有可能某個(gè)阻抗點(diǎn)的增益高輸出功率也比最大功率小不了多少,那那個(gè)點(diǎn)的效率就比最大功率點(diǎn)的效率高。

A:是這樣滴。

A:強(qiáng)。

A:老司機(jī)啊!

A:謬贊了各位,我只是之前想過。

10自行設(shè)計(jì)片內(nèi)電感能否優(yōu)化尺寸和Q值?

Q:有自己畫過片內(nèi)電感的同志嘛,請(qǐng)問自己畫的同樣感值的情況下能否比pdk自帶的面積小些,Q值高些?

A:什么頻段的?低頻的話好像用pdk里的說不定更準(zhǔn)些。

Q:2.4G,Pdk里的面積好大啊,tsmc65nm中電感外面還包圍著其他東西。

A:可能就是因?yàn)檫@樣才準(zhǔn)吧pdk自帶了一些處理,自己繞應(yīng)該也可以,不過可能自諧振頻率會(huì)比較低看形狀和線寬了,應(yīng)該有幾nH了吧。

Q:3.5n,Pdk的感覺也不是很準(zhǔn),和理想的ind和R串聯(lián)的模型不是很等效。

A:看你帶寬多少了,自己繞一個(gè)也行。

Q:帶寬80M,藍(lán)牙頻段。

A:有沒有可能是你這個(gè)等效太簡(jiǎn)單了,肯定pdk的準(zhǔn)啊20G以下都是實(shí)測(cè)出來的數(shù)據(jù)。

Q:啊,這樣子啊,那我打算用片外的了。

A:實(shí)際電感的等效模型很復(fù)雜的。

Q:是的,跟我算的有差距。

A:你也沒考慮寄生電容吧?

Q:沒有的,我就用串聯(lián)電阻等效的。

A:那么長的線圈走線寄生電容也不小的,片外的話就得考慮鍵合線的影響。

Q:感謝各位,Q值大一些就行,我主要是Q值對(duì)我的電路影響太大了,片內(nèi)的3.5n的電感Q值才14.5,面積還賊大356×365。

A:那就片外其實(shí)這個(gè)頻率片上電感能有十幾的Q就不錯(cuò)了,線寬都得二十um吧。

A:片上電感Q值15基本極限了。

A:那不至于,毫米波能20+。

A:對(duì)Q值要求很高,用鍵合線比較好。

Q:電感小一點(diǎn)能15以上,電感越大Q值越小。

A:pdk里能有14.5已經(jīng)不錯(cuò)了。

Q:是的。

11在諧波測(cè)試中,是否需要使用外部濾波器來濾除主頻?

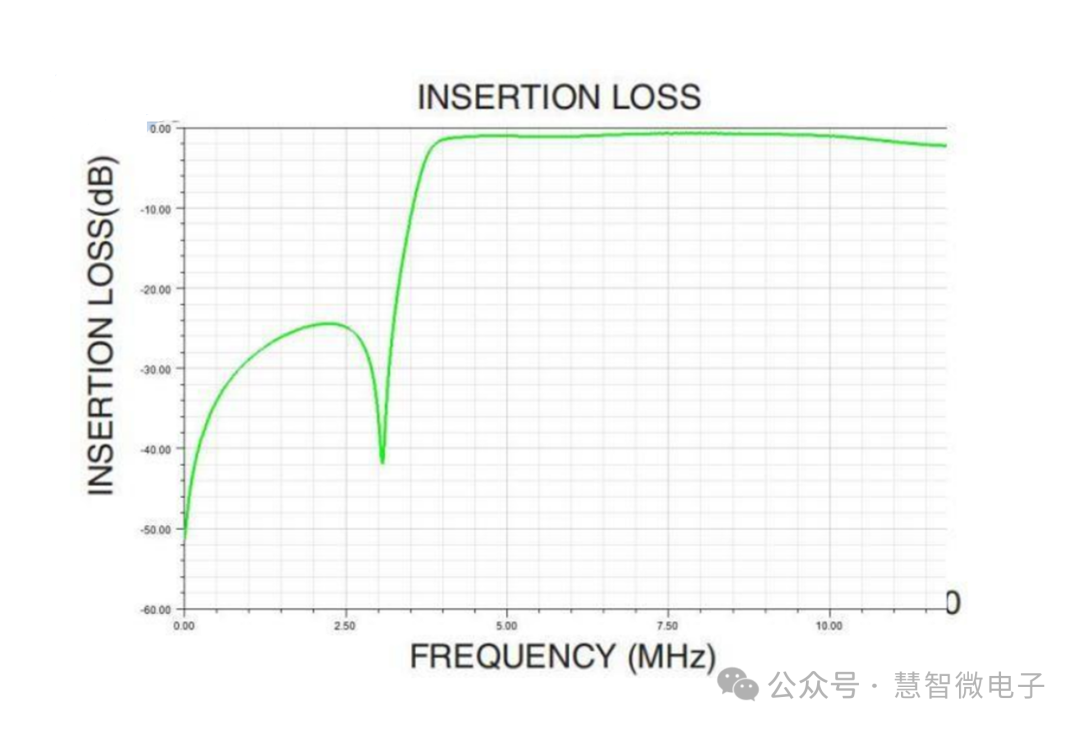

Q:請(qǐng)問各位老師,在做諧波測(cè)試時(shí),是否需要在頻譜儀前使用外部濾波器,把主頻濾除掉?按道理頻譜儀里面也有濾波器,用外部濾波器測(cè)試前后,諧波差異30dB,是不是可以判斷主頻的確在頻譜儀里面混出諧波了?

這是我用到的高通濾波器。

A:主頻肯定要濾掉的,不然主頻進(jìn)到頻譜儀里面,產(chǎn)生非線性,這個(gè)諧波能量就不一定是你這產(chǎn)品產(chǎn)生的,有可能是頻譜儀帶來的。如果你的主頻功率大,進(jìn)到頻譜儀里面,過載也會(huì)產(chǎn)生很多非線性。

A:單機(jī)+高通濾波器,中間最好再加一個(gè)隔離器。

Q:我的主頻是2.4G,頻譜儀只打4~8G看諧波,依然會(huì)有主頻在頻譜儀里面混出諧波意思是頻譜儀里面的濾波器,在Freq Range里面并不能完全把主頻能量抑制嗎?謝謝各位老師

GPT還是需要改善呀

測(cè)試諧波時(shí),需不需要加高通濾波器,把主頻濾掉?

測(cè)試諧波時(shí),通常不需要加高通濾波器來濾掉主頻信號(hào)。諧波是指在電力系統(tǒng)中,由于非線性負(fù)載的存在,電流和電壓波形發(fā)生畸變,產(chǎn)生頻率為基波頻率整數(shù)倍的額外頻率分量。這些頻率分量就是諧波。

在測(cè)試諧波時(shí),我們通常關(guān)注的是這些額外的頻率分量,而不是基波頻率分量。因此,測(cè)試設(shè)備(如頻譜分析儀、諧波分析儀等)本身就會(huì)包含高通濾波器,用于濾除基波頻率以下的信號(hào),只顯示諧波頻率分量。

高通濾波器的截止頻率設(shè)置通常會(huì)高于所關(guān)注的諧波頻率范圍,以確保只顯示諧波分量。例如,如果關(guān)注的是50Hz電網(wǎng)頻率的諧波,高通濾波器的截止頻率可能會(huì)設(shè)置在50Hz以上,比如100Hz或更高。

在實(shí)際測(cè)試中,確保測(cè)試設(shè)備正確設(shè)置,并選擇合適的諧波分析功能,就可以直接獲取諧波頻率分量的信息,而不需要額外添加高通濾波器。

所以說,在做RE,RSE等認(rèn)證測(cè)試時(shí),是需要增加陷波器,把主頻濾除,以免在頻譜儀中混出其他雜散頻點(diǎn)對(duì)嗎?

A:有條件最好用腔體的帶阻濾波器。

A:GPT回答的這個(gè),濾波器應(yīng)該不能覆蓋到你這種高頻的吧?這個(gè)就只陷掉主頻,窄帶陷波器,其他的高低頻雜散才能看到,如果用高通濾波器,低頻的雜散就看不出來了。

A:頻譜儀主頻不飽和的前提下動(dòng)態(tài)也有80左右,你是諧波抑制很大的話需要濾掉主頻再看,頻譜儀里面按頻率劃分為幾段 ,頻率低的只有低通 ,其他段有YIG電調(diào)濾波器,最好是不指望用頻譜儀的。

Q:明白了,感謝各位的指導(dǎo)!

-

阻抗

+關(guān)注

關(guān)注

17文章

960瀏覽量

46161 -

仿真

+關(guān)注

關(guān)注

50文章

4120瀏覽量

133849 -

傳輸線

+關(guān)注

關(guān)注

0文章

376瀏覽量

24076 -

電源芯片

+關(guān)注

關(guān)注

43文章

1100瀏覽量

77181

原文標(biāo)題:如何僅通過EM仿真SNP文件獲取傳輸線特征阻抗?

文章出處:【微信號(hào):射頻學(xué)堂,微信公眾號(hào):射頻學(xué)堂】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

MOS管耗散功率的計(jì)算

防止過高的 LED 結(jié)溫

詳解芯片的結(jié)溫

如何計(jì)算MOSFET的功率耗散

如何去測(cè)量功率器件的結(jié)溫?

如何計(jì)算電源方案的耗散功率?

利用仿真來估計(jì)功率半導(dǎo)體的結(jié)溫

芯片熱阻計(jì)算/熱與結(jié)溫的關(guān)系

防止過高的 LED 結(jié)溫

結(jié)溫計(jì)算與低熱阻LED探討

如何準(zhǔn)確測(cè)量到功率器件內(nèi)部硅片的結(jié)溫?

功率器件結(jié)溫和殼頂溫度有什么區(qū)別

Tvj - IGBT元宇宙中的結(jié)溫

電源芯片耗散功率與結(jié)溫關(guān)系的探討

電源芯片耗散功率與結(jié)溫關(guān)系的探討

評(píng)論