斯坦福大學(xué)的研究人員已經(jīng)證明,由單層二硫化鉬(MoS2)制成的場效應(yīng)晶體管可以成功驅(qū)動電阻式隨機存取存儲器。近日在IEEE國際電子設(shè)備會議上報告的結(jié)果代表了在單片3D集成芯片中將存儲器與邏輯混合的關(guān)鍵里程碑。

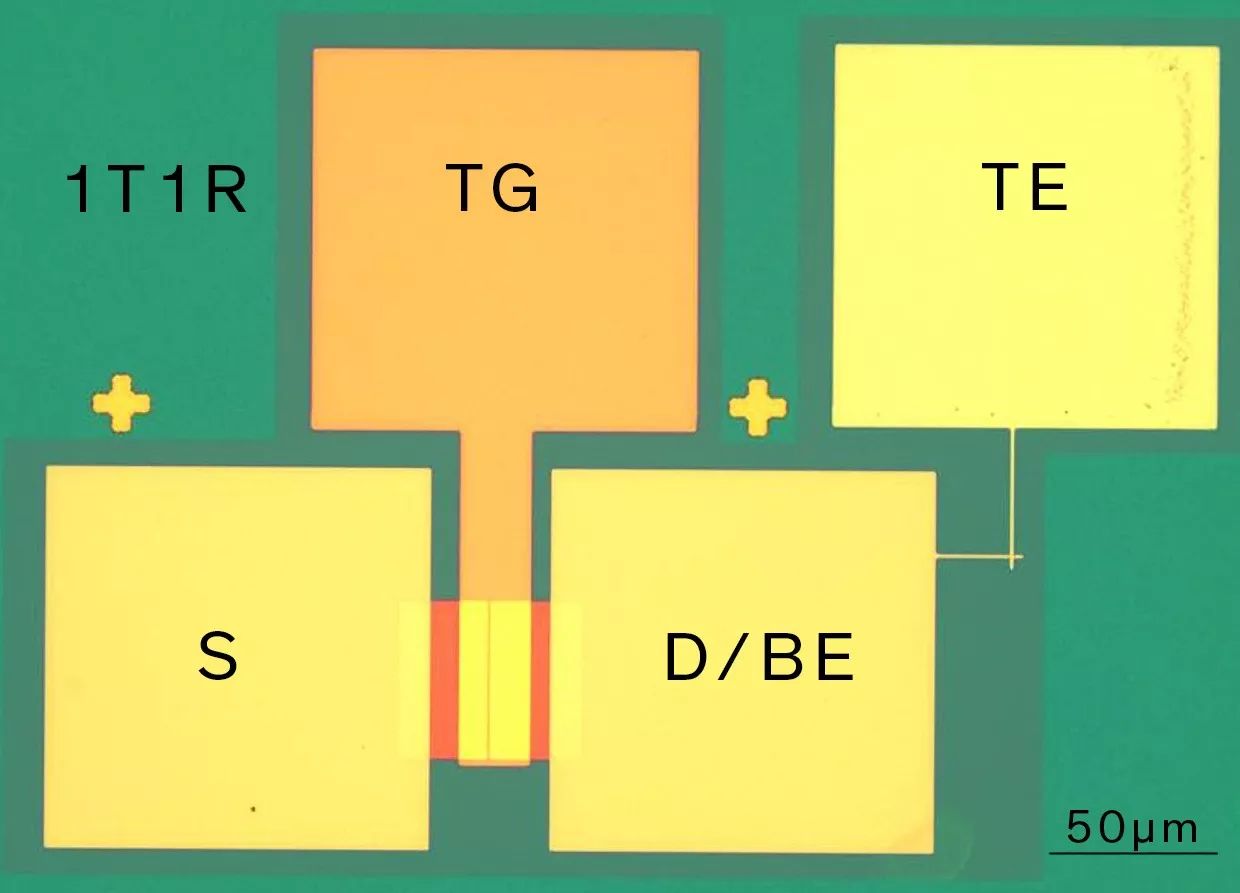

斯坦福研究人員開發(fā)的芯片被稱為“單晶體管單阻變存儲器”(1T1R)單元。這種1T1R存儲單元相對于含有阻變存儲器但沒有晶體管的存儲單元,能夠提供極大好處。

沒有晶體管的情況下,阻變存儲芯片中的所有存儲單元都被連接到不同的線路,從而使存儲陣列成為一個大電阻網(wǎng)絡(luò)。當(dāng)選擇某個存儲單元讀取其內(nèi)容時,電流不僅來自所選的存儲單元,還來自存儲陣列中所有未選存儲單元的泄漏電流。由于這些泄漏電流,被選存儲單元上的電壓將小于施加電壓。

1T1R存儲單元的好處在于,可以通過晶體管的開啟和關(guān)閉,將目標存儲單元同其他存儲單元隔離,從而抑制泄漏電流。“雖然硅場效應(yīng)晶體管也可以用于1T1R存儲單元,但單層二硫化鉬的優(yōu)點在于,其轉(zhuǎn)移工藝可以在較低溫度下進行,從而便于在單塊芯片中實現(xiàn)存儲層和邏輯層的相互三維堆疊配置。” 斯坦福大學(xué)的博士后研究員Rui Yang說。他是H.-S內(nèi)部研究的主要作者,和Philip Wong都在Nanoelectronics實驗室。

Yang補充說,“二硫化鉬場效應(yīng)晶體管的電流溝道只有原子厚度,納米級的中間層過孔可以成為連接芯片不同層的通道。這使芯片中的更多部分能夠更加有效訪問存儲器。”

在一般操作中,阻變存儲器將數(shù)據(jù)存儲為電阻阻值。對于采用1T1R存儲單元的阻變存儲器,當(dāng)存儲單元中的場效應(yīng)晶體管(本例中是基于二硫化鉬的場效應(yīng)晶體管)開啟時,存儲單元就處于寫入模式。此時,其他未被選中單元的晶體管將處于關(guān)閉狀態(tài),電壓將被施加在所選阻變存儲器的頂部電極和二硫化鉬晶體管的源電極上。

晶體管與阻變存儲器串聯(lián)在一起。當(dāng)阻變存儲器從高阻狀態(tài)轉(zhuǎn)變?yōu)榈妥锠顟B(tài)時,阻變存儲器的頂部電極就處于高電平狀態(tài),場效應(yīng)管的源電極接地。晶體管驅(qū)動電流通過阻變存儲器并控制電流,當(dāng)電壓周期性變化時,進而調(diào)控電阻值。目前,阻變存儲器的制取可以利用CMOS兼容的材料實現(xiàn)。

然而,表示,目前工業(yè)上還沒有準備在同等程度上制造二維材料。他說:“我們需要找到可靠的方法,以在晶片上生長和轉(zhuǎn)移二維材料,并在單片三維堆疊架構(gòu)上實現(xiàn)二維晶體管與阻變存儲器的集成。”Yang說。

除了在晶片上生長和轉(zhuǎn)移二維材料以外,這些器件仍有許多問題需要克服。楊認為,他們需要使器件更小,使1T1R存儲陣列更大,并進一步提高器件的一致性。他相信該技術(shù)極具發(fā)展前景。二硫化鉬和阻變存儲器不僅使平面內(nèi)電路規(guī)模的橫向擴展成為可能,而且還提供了通過三維堆疊方式使電路規(guī)模在垂直方向上實現(xiàn)擴展的可能性。Yang補充道:“為了實現(xiàn)這一目標,我們計劃在三維電路中制造多個存儲層和邏輯層,并使其具備存儲器內(nèi)計算的能力。”

-

存儲器

+關(guān)注

關(guān)注

38文章

7579瀏覽量

165477 -

晶體管

+關(guān)注

關(guān)注

77文章

9881瀏覽量

139843

原文標題:斯坦福大學(xué)開發(fā)單晶體管單阻變存儲器單元

文章出處:【微信號:IEEE_China,微信公眾號:IEEE電氣電子工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

評論