在高速實(shí)時(shí)或者非實(shí)時(shí)信號(hào)處理系統(tǒng)當(dāng)中,使用大容量存儲(chǔ)器實(shí)現(xiàn)數(shù)據(jù)緩存是一個(gè)必不可少的環(huán)節(jié),也是系統(tǒng)實(shí)現(xiàn)中的重點(diǎn)和難點(diǎn)之一。SDRAM(同步動(dòng)態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器)具有價(jià)格低廉、密度高、數(shù)據(jù)讀寫(xiě)速度快的優(yōu)點(diǎn),從而成為數(shù)據(jù)緩存的首選存儲(chǔ)介制裁。但是SDRAM存儲(chǔ)體結(jié)構(gòu)與RAM有較大差異,其控制時(shí)序和機(jī)制也較復(fù)雜,限制了SDRAM的使用。目前,雖然一些能家長(zhǎng)微處理器提供了和SDRAM的透明接口,但其可擴(kuò)展性和靈活性不夠,難以滿(mǎn)足現(xiàn)實(shí)系統(tǒng)的要求,限制了SDRAM的使用。

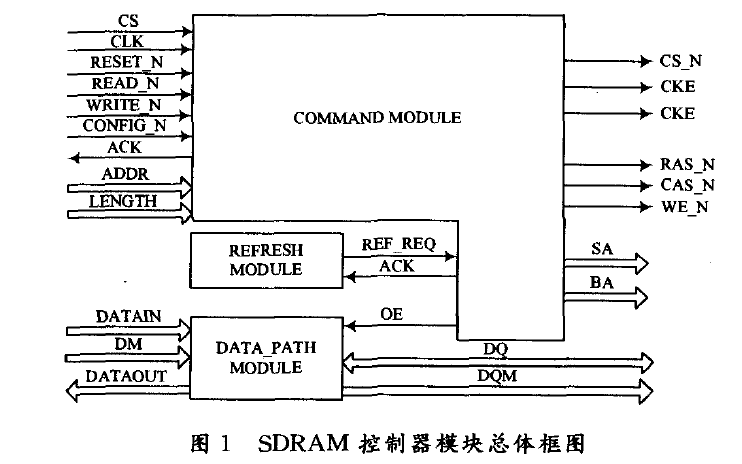

在詳細(xì)闡讀SDRAM數(shù)據(jù)文檔的前提下,參考ALTERA公司的IP core,利用可編程器件(CPLD,FPGA)設(shè)計(jì)了一種通用的SDRAM控制器。它具有很高的靈活性,可以方便地和其它數(shù)據(jù)采集分析系統(tǒng)中,如圖1所示。在該系統(tǒng)中,以SDRAM存儲(chǔ)陣列緩存中頻來(lái)的高速數(shù)據(jù)。存滿(mǎn)后,數(shù)據(jù)被慢速讀出至數(shù)據(jù)處理模塊。下面將對(duì)SDRAM控制模塊的設(shè)計(jì)進(jìn)行詳細(xì)的描述。

1 SDRAM內(nèi)存條的結(jié)構(gòu)

SDRAM內(nèi)存條由SDRAM內(nèi)存芯片構(gòu)成,根據(jù)內(nèi)存條的容量大小決定內(nèi)存條上內(nèi)存芯片的個(gè)數(shù)。現(xiàn)以MICRON公司生產(chǎn)的TIM16LSDT6464A型SDRAM內(nèi)存條為例,簡(jiǎn)要介紹SDRAM的結(jié)構(gòu)。

MIT16LSDT6464A內(nèi)存條容量為512M Byte,由16片容量為32M Byte的內(nèi)存芯片MT46LC32M8A2構(gòu)成。16片內(nèi)存芯片被分為兩級(jí),每個(gè)芯片的數(shù)據(jù)位寬為8bit.8片一組,64bit數(shù)據(jù)寬度。每個(gè)內(nèi)存芯片的數(shù)據(jù)線和控制均是復(fù)用的。對(duì)內(nèi)存條的讀寫(xiě)操作,是以?xún)?nèi)存芯片組為單位的,通過(guò)內(nèi)存條的片選信號(hào)S0、S1、S2、S3決定組號(hào)。S0、S2控制芯片組1,S1、S3控制芯片組2.

SDRAM內(nèi)存芯片的主要信號(hào)有控制信號(hào)、控制信號(hào)、數(shù)據(jù)信號(hào),均為工作時(shí)鐘同步輸入、輸出信號(hào)。

控制信號(hào)主要有:CS(片選信號(hào)),CKE(時(shí)鐘使能信號(hào)),DQM(輸入、輸出使能信號(hào)),CAS、RAS、WE(讀寫(xiě)控制命令字)。通過(guò)CAS、RAS、WE的各種邏輯組合,可產(chǎn)生各種控制命令。

地址信號(hào)有:BA0和BA1頁(yè)地址選擇信號(hào),A0~A12地址信號(hào),行、列地址選擇信號(hào)。通過(guò)分時(shí)復(fù)用決定地址是行地址還是列地址。在讀寫(xiě)操作中,在地線上依次給出頁(yè)地址、行地址、列地址,最終確定存儲(chǔ)單元地址。

數(shù)據(jù)信號(hào)有:DQ0~DQ7,雙向數(shù)據(jù)。其使能受DQM控制。

SDRAM的工作模式通過(guò)LOAD MODE REGISTER命令對(duì)工作模式寄存器進(jìn)行設(shè)置來(lái)選擇。設(shè)置參量有Reserved(備用的人)Write Burst Mode(WB,寫(xiě)突發(fā)模式)、Operation Mode(Op Mode,工作模式)、CAS Latency(CAS延遲)、Burst Type(BT,突發(fā)類(lèi)型)、Burst Length(突發(fā)長(zhǎng)度)。

2 SDRAM的基本讀寫(xiě)操作

SDRAM的基本讀操作需要控制線和地址線相配合地發(fā)出一系列命令來(lái)完成。先發(fā)出BANK激活命令(ACTIVE),并鎖存相應(yīng)的BANK地址(BA0、BA1給出)和行地址(A0~A12給出)。BANK激活命令后必須等待大于tRCD(SDRAM的RAS到CAS的延遲指標(biāo))時(shí)間后,發(fā)出讀命令字。CL(CAS延遲值)個(gè)工作時(shí)鐘后,讀出數(shù)據(jù)依次出現(xiàn)在數(shù)據(jù)總線上。在讀操作的最后,要向SDRAM發(fā)出預(yù)充電(PRECHARGE)命令,以關(guān)閉已經(jīng)激活的頁(yè)。等待tRP時(shí)間(PRECHARGE)命令,以關(guān)閉已經(jīng)激活的頁(yè)。等待tRP時(shí)間(PRECHAREG命令后,相隔tRP時(shí)間,才可再次訪問(wèn)該行)后,可以開(kāi)始下一次的讀、寫(xiě)操作。SDRAM的讀操作只有突發(fā)模式(Burst Mode),突發(fā)長(zhǎng)度為1、2、4、8可選。

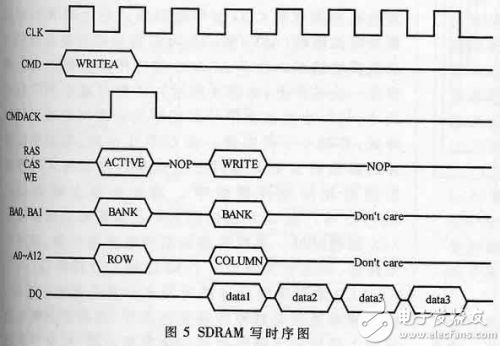

SDRAM的基本寫(xiě)操作也需要控制線和地址線相配合地發(fā)出一系列命令來(lái)完成。先發(fā)出BANK激活命令(ACTIVE),并鎖存相應(yīng)的BANK地址(BA0、BA1給出)和行地址(A0~A12給出)。BANK激活命令后必須等待大于tRCD的時(shí)間后,發(fā)出寫(xiě)命令字。寫(xiě)命令可以立即寫(xiě)入,需寫(xiě)入數(shù)據(jù)依次送到DQ(數(shù)據(jù)線)上。在最后一個(gè)數(shù)據(jù)寫(xiě)入后延遲tWR時(shí)間。發(fā)出預(yù)充電命令,關(guān)閉已經(jīng)激活的頁(yè)。等待tRP時(shí)間后,可以展開(kāi)下一次操作。寫(xiě)操作可以有突發(fā)寫(xiě)和非突發(fā)寫(xiě)兩種。突發(fā)長(zhǎng)度同讀操作。

tRCD、tRP、tWR的具體要求,詳見(jiàn)SDRAM廠家提供的數(shù)據(jù)手冊(cè)。所等待的工作時(shí)鐘個(gè)數(shù)由tRCD、tRP、tWR的最小值和工作時(shí)鐘周期共同決定。

由以上介紹可以得出,SDRAM的讀、寫(xiě)操作均由一系列命令組成,因此讀、寫(xiě)操作是有時(shí)鐘損耗的,工作時(shí)鐘速率不等于SDRAM能達(dá)到的讀、寫(xiě)速率。但是由于SDRAM有突發(fā)讀、寫(xiě)模式,也就是說(shuō)可以讀出和寫(xiě)入一串地址連續(xù)的數(shù)據(jù),從而提高了效率。當(dāng)突發(fā)長(zhǎng)度為整頁(yè)時(shí),讀、寫(xiě)速度達(dá)到最快。隨機(jī)讀、寫(xiě)速度的計(jì)算公式為:

furite/read=工作時(shí)鐘頻率(HzHzHhdkkdk ss dkkdkdkd,,,m,mddddd)×數(shù)據(jù)寬度(bytes)×突發(fā)讀寫(xiě)長(zhǎng)度/操作所需的時(shí)鐘數(shù)

為了提高存儲(chǔ)密度,SDRAM采用硅片電容存儲(chǔ)信息。電容總會(huì)有漏電流流過(guò),所以為了不使信息丟失,必須定期地給電容刷新充電。外部控制邏輯必須按要求定期向內(nèi)存條發(fā)出刷新命令,保證在規(guī)定的時(shí)間內(nèi)對(duì)每一個(gè)單元都進(jìn)行刷新。

3 初始化操作

SDRAM在上電以后必須對(duì)其進(jìn)行初始化操作,具體操作如下:

(1)系統(tǒng)在上電后要等待100~200μs.在待時(shí)間到了以后至少執(zhí)行一條空操作或者指令禁止操作。

(2)對(duì)所有芯片執(zhí)行PRECHARGE命令,完成預(yù)充電。

(3)向每組內(nèi)存芯片發(fā)出兩條AUTO REFRESH命令,使SDRAM芯片內(nèi)部的刷新計(jì)數(shù)器可以進(jìn)入正常運(yùn)行狀態(tài)。

(4)執(zhí)行LOAD MODE REGISTER命令,完成對(duì)SDRAM工作模式的設(shè)定。

完成以上步驟后,SDRAM進(jìn)入正常工作狀態(tài),等待控制器對(duì)其進(jìn)行讀、寫(xiě)和刷新等操作。

4 SDRAM控制器設(shè)計(jì)

4.1 功能說(shuō)明

在以SDRAM作為緩存的系統(tǒng)中,使用可編程器件對(duì)其進(jìn)行控制具有很強(qiáng)的靈活性。為了使設(shè)計(jì)具有模塊化和可重復(fù)使用的優(yōu)點(diǎn),設(shè)計(jì)了一個(gè)簡(jiǎn)化的SDRAM接口電路。這樣就屏蔽掉了SDRAM操作的復(fù)雜性,而其它邏輯模塊可通過(guò)接口電路對(duì)SDRAM進(jìn)行訪問(wèn)。此外,由于整個(gè)SDRAM控制器用VHDL語(yǔ)言編寫(xiě),只要對(duì)其進(jìn)行簡(jiǎn)單的修改就可以滿(mǎn)足不同的需求,具有很強(qiáng)的靈活性。

參照?qǐng)D2,SDRAM控制器完成的主要功能是對(duì)CMD[2:0]的命令字和ADDR端的地址進(jìn)行解析,產(chǎn)生相應(yīng)的SDRAM的控制時(shí)序。

CLK為輸入的工作時(shí)鐘端口。

ADDR為輸入地址端口。控制器將其解析為對(duì)應(yīng)的片選、頁(yè)以及行、列地址。以一條MIT16LSDT6464A內(nèi)存條為例,其大小為512Mbyte(2 29 byte)。數(shù)據(jù)位寬為64bit(8byte),則地址線ADDR應(yīng)為26根。可以這樣映射地址:ADDR[25]對(duì)應(yīng)內(nèi)存芯片組號(hào);ADDR[24:23]對(duì)應(yīng)頁(yè)號(hào);ADDR[22:10]對(duì)應(yīng)行號(hào);ADDR[9:0]對(duì)應(yīng)列號(hào)。

DATAIN為寫(xiě)入數(shù)據(jù)端口,64bit位寬。

DATAOUT為讀出數(shù)據(jù)端口,64bit位寬。

RD_OE為讀出數(shù)據(jù)使能端口,當(dāng)其為1時(shí),表示從下一個(gè)時(shí)鐘起,數(shù)據(jù)將依次出現(xiàn)在DATAOUT口上。

WR_OE為寫(xiě)入數(shù)據(jù)使能端口,當(dāng)其為1時(shí),寫(xiě)入數(shù)據(jù)應(yīng)該依次出現(xiàn)在DATAIN口上。

CMD[2:0]為命令輸入端口,分別表示讀、寫(xiě)內(nèi)存等待操作。其中,CMD=“000”表示無(wú)操作,內(nèi)存條交給控制器管理,定其完成刷新工作;REFRESH命令由外部邏輯指定特刷新的內(nèi)存芯片信號(hào),組號(hào)由ADDR的低位給出;LOAD_MODE命令執(zhí)行內(nèi)存條工作寄存器初始化工作,初始化值由DATAIN的低13位決定,內(nèi)存芯片組號(hào)同樣由ADDR的低位給出;同理,ADDR的低位也決定了預(yù)充電操作所對(duì)應(yīng)的內(nèi)存芯片組號(hào)。

CMDACK為命令應(yīng)答端口,表示命令已經(jīng)被執(zhí)行,使外部邏輯可以向控制器發(fā)出下一個(gè)動(dòng)作。

4.2 狀態(tài)機(jī)

圖3是SDRAM控制器的狀態(tài)轉(zhuǎn)移圖。狀態(tài)圖中的各個(gè)狀態(tài)內(nèi)均包含一系列的子狀態(tài)轉(zhuǎn)移(對(duì)SDRAM內(nèi)存條發(fā)出連續(xù)命令),每個(gè)子狀態(tài)完成一個(gè)功能操作。初始化操作包括前面介紹的內(nèi)存條初始化全過(guò)程,工作寄存器的默認(rèn)值在VHDL程序中指定。以后可以通過(guò)LOAD_MODE命令改變內(nèi)存條的工作模式。初始化結(jié)束后,內(nèi)存條進(jìn)入Idel狀態(tài),刷新計(jì)數(shù)器開(kāi)始工作,控制器開(kāi)始響應(yīng)外部邏輯的操作請(qǐng)求。

刷新計(jì)數(shù)器操作是一個(gè)獨(dú)立的進(jìn)程(process)。刷新計(jì)數(shù)器的初值由內(nèi)存芯片要求、內(nèi)存條個(gè)數(shù)和控制器工作頻率共同決定。例如,在本次設(shè)計(jì)中,所采用的MT48LC32M8A2內(nèi)存芯片要求在64ms內(nèi)夏至少刷新8196次。而MIT16LSDT6464A型內(nèi)存條共有兩組內(nèi)存芯片,也就是要求在64ms內(nèi)要發(fā)出8196×2條自刷新(AUTO REFRESH)指令。系統(tǒng)工作時(shí)鐘為46.66MHz,因此控制單條MIT16LSDT6464A時(shí),刷新計(jì)數(shù)器初值至多為(64ms/8196/2)×6、、46.66MHz,即182.開(kāi)始工作后,每當(dāng)刷新計(jì)數(shù)器值減為0,便依次向內(nèi)存芯片組發(fā)出刷新命令,保證SDRAM中的數(shù)據(jù)不丟失。刷新請(qǐng)求是內(nèi)存請(qǐng)求;讀和寫(xiě)操作是外部請(qǐng)求。在Idel狀態(tài)中有請(qǐng)求仲裁邏輯,當(dāng)內(nèi)部和外部請(qǐng)求同時(shí)出現(xiàn)時(shí),優(yōu)先保證內(nèi)部請(qǐng)求,狀態(tài)轉(zhuǎn)移至刷新操作。當(dāng)刷新操作結(jié)束時(shí),重新返回Idel狀態(tài),開(kāi)始響應(yīng)外部請(qǐng)求。響應(yīng)外部請(qǐng)求后,應(yīng)答信號(hào)CMDBAK出現(xiàn)正脈沖。它通知外部邏輯,請(qǐng)求已經(jīng)被響應(yīng),可以撤銷(xiāo)請(qǐng)求。在刷新操作狀態(tài)中,也有許數(shù)器計(jì)數(shù),其大小等于控制器管理的內(nèi)存芯片信號(hào)。記錄并判斷此次刷新操作所對(duì)應(yīng)的內(nèi)存芯片的組號(hào),產(chǎn)生相應(yīng)的片選信號(hào)。

響應(yīng)讀、寫(xiě)請(qǐng)求后,狀態(tài)從Idel轉(zhuǎn)移到讀、寫(xiě)狀態(tài)。同時(shí)讀、寫(xiě)地址和寫(xiě)入的數(shù)據(jù)鎖存至控制器。控制器由讀寫(xiě)地址解析出CS信號(hào)、頁(yè)地址、行地址、列地址。向內(nèi)存條發(fā)出一系列命令(ACTIVE,READ/WRITE with AUTO PRECHARGE),完成讀寫(xiě)操作,為了簡(jiǎn)化,此控制器向SDRAM發(fā)出的都是帶有AUTO PRECHARGE的讀、寫(xiě)指令,然后由SDRAM內(nèi)部邏輯自動(dòng)在讀、寫(xiě)過(guò)程末期發(fā)出PRECHARGE指令(在發(fā)READ/WRITE指令時(shí),地址線A10賦值1,打開(kāi)AUTO PRECHARGE功能)。圖4和圖5分別是利用該控制器完成讀、寫(xiě)操作的時(shí)序圖。讀操作的CAS延遲為兩個(gè)時(shí)鐘。

該SDRAM控制器在中頻數(shù)據(jù)海量存儲(chǔ)系統(tǒng)中已得到應(yīng)用。數(shù)據(jù)接收邏輯將接收到的中頻采樣數(shù)據(jù)整理后(拼接成64bit),通過(guò)SDRAM控制器存入SDRAM陣列。存滿(mǎn)后,數(shù)據(jù)輸出邏輯將中頻數(shù)據(jù)通過(guò)SDRAM控制器從內(nèi)存條中取出,傳輸至上位機(jī)。其VHDL代碼在ATERA公司的FPGA--EP1C6Q240中通過(guò)了Quartus II的仿真、綜合和布局、布線。占用499個(gè)logic cellk,消耗了8%的邏輯資源。留有豐富的資源可提供給其它邏輯單元使用。

上面介紹了SDRAM的基本工作原理和一種簡(jiǎn)單的通用SDRAM控制器的實(shí)現(xiàn)。SDRAM的控制機(jī)制比較復(fù)雜,具有多種突發(fā)讀、寫(xiě)方式和工作模式(詳細(xì)內(nèi)容請(qǐng)參考SDRAM的數(shù)據(jù)手冊(cè))。但是,可以根據(jù)實(shí)現(xiàn)應(yīng)用,實(shí)現(xiàn)其中的一個(gè)子集(基本讀、寫(xiě)、刷新操作)來(lái)滿(mǎn)足實(shí)際系統(tǒng)的需要。用SDRAM實(shí)現(xiàn)大容量的高速數(shù)據(jù)緩存具有明顯的優(yōu)勢(shì),使用可編程器件實(shí)現(xiàn)SDRAM控制器則使之具有更高的靈活性,其應(yīng)用前景廣闊。

-

控制器

+關(guān)注

關(guān)注

112文章

16376瀏覽量

178199 -

SDRAM

+關(guān)注

關(guān)注

7文章

423瀏覽量

55241 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2256瀏覽量

94607 -

vhdl

+關(guān)注

關(guān)注

30文章

817瀏覽量

128147

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何使用Verilog實(shí)現(xiàn)基于FPGA的SDRAM控制器?

存儲(chǔ)器接口vhdl代碼全集

SDRAM控制器參考設(shè)計(jì),Lattice提供的VHDL源代碼

SDRAM控制器的設(shè)備與VHDL實(shí)現(xiàn)

使用Verilog實(shí)現(xiàn)基于FPGA的SDRAM控制器

DDR SDRAM控制器參考設(shè)計(jì)VHDL代碼

SDRAM控制器的設(shè)計(jì)

FPGA讀寫(xiě)SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文

如何使用FPGA設(shè)計(jì)SDRAM控制器

DDR SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)簡(jiǎn)介

基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)

VHDL工具實(shí)現(xiàn)SDRAM控制器的要點(diǎn)分享

VHDL工具實(shí)現(xiàn)SDRAM控制器的要點(diǎn)分享

評(píng)論