在電子信號的精密傳輸領域,阻抗匹配扮演著至關重要的角色。當信號在傳輸過程中遭遇阻抗不匹配時,就如同水流在管道中遇到了障礙,不可避免地會產生反射現象。這種反射不僅會導致合成信號出現過沖,使信號波形在邏輯門限附近波動不定,更可能引發信號完整性受損,影響系統的整體性能。

要消除因阻抗不匹配而引發的反射問題,根本途徑在于實現傳輸信號的阻抗良好匹配。這意味著,我們需要精心設計電路,使得負載阻抗與傳輸線的特性阻抗之間的差異盡可能縮小。因為,阻抗差異越大,反射現象就越嚴重。同時,我們還需密切關注PCB上的傳輸線設計,避免出現突變或拐角等可能導致阻抗不連續的因素。只有保持傳輸線各點阻抗的連續性,才能有效減少在傳輸線各段之間可能出現的反射現象。

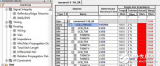

在高速PCB布線領域,為了實現良好的信號阻抗匹配,我們必須嚴格遵循一系列布線規則。以USB布線為例,要求USB信號采用差分走線方式,線寬設定為10mil,線距保持6mil,同時地線與信號線的距離也需控制在6mil。這樣的布線設計能夠有效減少信號間的串擾,提高信號傳輸的穩定性和可靠性。

對于HDMI布線而言,同樣要求采用差分走線方式,線寬和線距的設定與USB布線相似,但每兩組HDMI差分信號對的間距需超過20mil。這樣的布線規則旨在進一步降低信號間的相互干擾,確保HDMI信號的高質量傳輸。

LVDS布線則要求信號采用差分走線方式,線寬設定為7mil,線距保持6mil。這樣的布線設計旨在控制HDMI的差分信號對阻抗達到100+-15%歐姆的標準范圍內,從而確保信號的穩定傳輸和接收。

在DDR布線方面,對于DDR1而言,走線時要求信號盡量不走過孔,保持信號線等寬且等距。同時,走線必須滿足2W原則,以減少信號間的串擾。而對于DDR2及以上的高速器件而言,除了要求高頻數據走線等長以實現阻抗匹配外,還要求信號線在布局上更加精細和合理,以確保信號在高速傳輸過程中的穩定性和可靠性。

良好的信號阻抗匹配是優化電子信號傳輸質量、提升系統穩定性的關鍵所在。通過精心設計電路、遵循嚴格的布線規則以及關注傳輸線各點阻抗的連續性等措施的實施,我們可以有效消除因阻抗不匹配而引發的反射問題。

-

lvds

+關注

關注

2文章

1062瀏覽量

66745 -

PCB布線

+關注

關注

21文章

465瀏覽量

42349 -

高速PCB

+關注

關注

4文章

96瀏覽量

25223 -

信號阻抗

+關注

關注

0文章

4瀏覽量

1284

發布評論請先 登錄

相關推薦

PCB設計高速差分信號的布線技巧

高速PCB設計中的阻抗匹配

高速PCB布線技巧、EMI問題、設計規則

高速PCB信號布線的設計規范

高速PCB中的阻抗匹配

評論