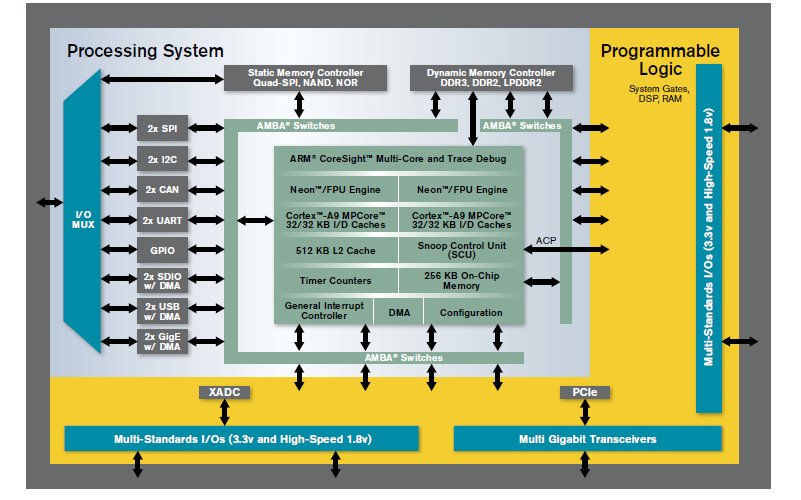

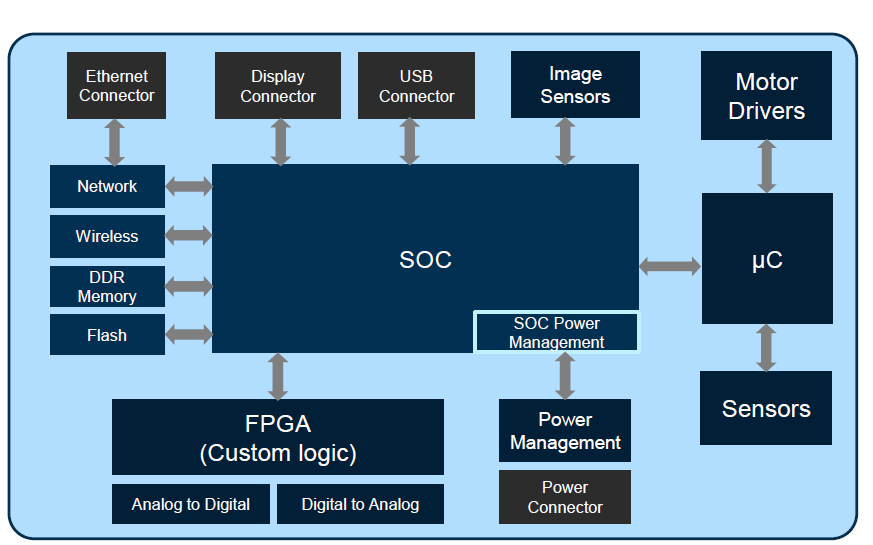

Xilinx Zynq-7000 全可編程 SoC (AP SoC) 系列集成 ARM處理器的軟件可編程性與 FPGA 的硬件可編程性,不僅可實現重要分析與硬件加速,同時還在單個器件上高度集成 CPU、DSP、ASSP 以及混合信號功能。Zynq-7000 器件配備雙核ARM Cortex-A9 處理器,該處理器與基于 28nm Artix-7 或 Kintex-7 的可編程邏輯集成,可實現優異的性能功耗比和最大的設計靈活性。這種集成在一起的CPU與FPGA之間的通訊總線,通訊速度更快,信息傳遞結構更簡單。簡單來說,就是Xilinx的這款芯片既能節省成本又能提高性能,還有這種好事?還真有,下面我來舉個例子。

鼎陽(SIGLENT)SDS1000X-E系列以及電商專供SDS1000X-C系列超級熒光示波器

2/4通道,最高帶寬200MHz

SDS1000X-E(X-C)中采用的XC7Z020 SoC芯片,具有雙核ARM Cortex-A9處理器(PS)+基于Artix-7架構的FPGA(PL),其中處理器部分支持的最高主頻為866MHz,FPGA部分則包含85k邏輯單元、4.9Mb Block RAM和220個DSP Slice,并提供對常用外部存儲器如DDR2/DDR3的支持,非常契合數字示波器中對數據進行采集、存儲和數字信號處理的需求。同時,Zynq-7000的PS(處理器系統)和PL(可編程邏輯)部分之間通過AXI高速總線互連,可以有效解決傳統數字存儲示波器中CPU與FPGA間數據傳輸的帶寬瓶頸問題,有利于降低數字示波器的死區時間,提高波形捕獲率。用單片SoC芯片替代傳統的CPU+FPGA的分立方案,也可以減少硬件布板面積,有利于將高性能處理系統向緊湊型的入門級示波器中集成。

數據采集與存儲

SDS1000X-E(X-C)中采用的高速模-數轉換(ADC)芯片,其數據接口為LVDS差分對形式,每對LVDS的速率為1Gbps。采用的Zynq-7000芯片,其可編程IO的LVDS最高速率可達1.25 Gbps,可以保證穩定可靠地接收ADC采樣到的數據。同時,FPGA接收到的高速ADC數據需要實時地寫入到存儲器中,以8-bit,1GSa/s的ADC為例,其輸出數據的吞吐率為1GByte/s。Zynq-7000支持常用的DDR2、DDR3等低成本存儲器,最高DDR3接口速率可達1066MT/s,因此,使用單片DDR3即可滿足實時存儲上述ADC輸出數據的要求。而且,Zynq-7000支持PL共享PS的存儲器,只要給PS部分預留足夠的存儲器帶寬,剩余帶寬用于存儲ADC數據,無須在PL部分再外掛存儲器,降低了成本。

更為重要的是,基于Zynq-7000中豐富的可編程邏輯資源(XC7Z020中為85k等效邏輯單元),SDS1000X-E(X-C)集成高靈敏度、低抖動、零溫漂的數字觸發系統,使得其觸發更為準確;各種智能觸發功能如斜率、脈寬、視頻、超時、欠幅、碼型等,能幫助用戶更精確地隔離出感興趣的波形;總線協議觸發甚至能直接用符合條件的總線事件(如I2C總線的起始位,或UART的特定數據)作為觸發條件,極大地方便調試。

數據交互

隨著數字示波器設計復雜性的增加和處理器處理能力的提升,總線結構日益成為系統性能的瓶頸。傳統的入門級數字示波器,采用低成本的嵌入式處理器作為控制和處理核心,采用低成本的FPGA實現數據采集和存儲,二者之間通過并行的本地總線互連,處理器作為主設備,FPGA作為從設備;總線上同時還連接其他處理器外設,如FLASH、USB控制器等,如圖4所示。

這種互連方式的最大問題是數據吞吐率低,一是因為本地總線一般是異步總線,理想的情況下一個讀/寫訪問最少需要3個周期(1個setup周期,1個access周期和1個hold周期)。以16-bit位寬,外部總線頻率100MHz的本地總線為例,其理想的最高總線訪問吞吐率為66MB/s;二是因為讀、寫操作共用一套地址、數據總線,屬于半雙工操作;三是多個從設備會競爭總線,從而降低每個從設備的有效數據吞吐率。以1GSa/s采樣率的數字示波器為例,其采樣10M點的時間僅為10ms,但用于傳輸10M點的時間(以理想的66MB/s總線吞吐率為例)至少要150ms,是數據采樣時間的15倍。換一種說法,即使不考慮數據處理的時間,死區時間也達到了15/16 = 93.75%。

SDS1000X-E(X-C)采用Zynq SoC架構,處理器(PS)和FPGA(PL)之間采用高速AXI總線互連,可以有效地解決二者間數據傳輸的帶寬瓶頸問題,大大提高數據吞吐率,降低示波器的死區時間。Zynq-7000中采用的4個AXI-HP端口,每個端口支持最大64-bit位寬,最高250MHz時鐘頻率;同時讀、寫通道分開,可執行全雙工操作;PS和PL之間屬于點到點傳輸,不存在與其它設備的總線競爭。使用單個HP端口傳輸數據,其吞吐率都可以輕易達到雙向各1GB/s的速度,4個端口總共可達到的讀、寫速率一共超過8GB/s,遠遠大于本地總線的傳輸速率。

數字信號處理

SDS1000X-E(X-C)中配備了很多實用性高、性能強大的數字信號處理功能,如支持1M點運算的FFT、增強分辨率(Eres模式,僅SDS1000X-E支持)、14M 全采樣點的串行協議解碼、14M 全采樣點的多種測量以及數學運算等,大大提高了入門級數字示波器的數字信號處理能力。

Zynq-7000豐富的硬件資源,為SDS1000X-E(X-C)的數字信號處理功能提供了強大的支撐。SDS1000X-E(X-C)中采用的XC7Z020 SoC芯片,PS部分具有雙核ARM Cortex-A9處理器,最高主頻為866MHz,并行協處理器NEON可以在軟件層面執行數字信號處理;PL部分具有220個DSP Slice和4.9Mb Block RAM;加上PS和PL之間數據接口極高的吞吐率,使得我們可以靈活地為不同的數字信號處理配置不同的硬件資源。

運算指令復雜、適合軟件實現的功能,可以在PS側實現,如信號上升沿的測量;需要使用大量乘累加運算,對硬件資源依賴度較高的功能,可以在PL側實現,如示波器中常用的插值濾波。

有些復雜的功能,則可以利用PS和PL間的高數據帶寬進行協同處理,例如FFT運算,在PL側利用豐富的DSP Slice和Block RAM資源構建協處理器對基本FFT運算進行硬件加速,PS側則實現復雜的窗函數計算、繪圖、UI等操作。基于這種協同處理的架構,SDS1000X-E(X-C)上的FFT支持高達1M點的FFT,在獲得極高的頻譜分辨率的同時,還能大大加快頻譜的刷新速度。圖6顯示了在SDS1000X-E(X-C)上分別進行16k點和1M點FFT的頻譜分辨率對比。此例中我們給示波器輸入了一個雙音信號,其頻率為100MHz和100.05MHz,從16k點FFT獲得的頻譜圖中我們無法分辨如此靠近的兩個正弦信號,信號被作為一個頻率顯示出來;而1M點FFT的頻譜圖有著明顯更細致的頻譜以及信號處理增益,從水平100倍展開的圖中可以看出,兩個相距50kHz的正弦型號能夠被很好地區分開。

類似的,在SDS1000X-E(X-C)還有諸多這種PS和PL間相互協同處理而獲得的高性能數字信號處理。例如,SDS1000X-E(X-C)可以對14M 全采樣點進行多種測量和串行協議解碼,而這是在許多中、高端示波器中都做不到的。圖7中,上方兩圖為某主流中端示波器對10ns上升沿的測量結果,下方兩圖為SDS1000X-E(X-C)對相同信號的測量結果。可以看到,在小時基下,二者的測量結果都較為精確,與實際上升時間相差不大,但在大時基下,右上圖顯示該示波器在100us/div下只能顯示"< 48ns"的測量結果,注意此時它的原始采樣率仍然有1GSa/s,這說明此時它的測量對象并不是原始波形數據,而是經過壓縮后映射到屏幕上的數據。右下圖顯示SDS1000X-E(X-C)在1ms/div的時基下的測量結果,注意此時的采樣率同樣為1GSa/s,但顯示的測量精度仍然達到了1ns,能夠較為真實地反映信號的參數。

SDS1000X-E(X-C)基于全采樣點的數字信號處理以及高達14M點的存儲深度,允許用戶在大時基下觀察信號整體的同時,仍然能獲得細節上的處理結果;同時由于其基于Zynq架構的處理方式,使得信號處理的性能和速度達到最優,具備更好的實時性和靈活性。

綜上,這個例子說明了一點,就是在原本解決方案里就采用ARM+FPGA的產品里,使用zynq不僅能降低成本,還可以大幅度提高性能。這就使得在這款市場定位于入門級示波器的SDS1000X-E(X-C)上,就能夠體現到一些中、高端數字示波器才具有的指標和功能。

-

Kintex-7

+關注

關注

1文章

27瀏覽量

16036

原文標題:淺談Xilinx ZYNQ-7000平臺的應用【文尾有福利】

文章出處:【微信號:Hardware_10W,微信公眾號:硬件十萬個為什么】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

簡談Xilinx Zynq-7000嵌入式系統設計與實現

簡談Xilinx Zynq-7000嵌入式系統設計與實現

基于Zynq-7000創龍高速數據采集處理器

Zynq-7000 SoC提供 FPGA 資源

賽靈思Zynq-7000可擴展處理平臺讓編程流程更簡單

Xilinx首款可擴展式處理平臺:Zynq-7000

使用Zynq-7000 All Programmable SoC實現DSP功能的軟件加速

Xilinx Zynq-7000的汽車可編程SOC芯片的詳細資料說明

Zynq-7000全可編程SoC產品中文簡介資料免費下載

Zynq-7000全可編程SoC ZC706評估套件(ISE Design Suite 14.5)入門指南

實現重要分析與硬件加速的可編程Xilinx zynq-7000平臺推薦

實現重要分析與硬件加速的可編程Xilinx zynq-7000平臺推薦

評論