CMOS(互補金屬氧化物半導體)和TTL(晶體管-晶體管邏輯)是兩種廣泛應用于數字電路設計中的邏輯門技術。它們在性能、功耗、速度、成本和抗干擾能力等方面存在顯著差異。

- CMOS技術概述

CMOS技術是一種使用互補型金屬氧化物半導體場效應晶體管(MOSFET)的數字邏輯技術。CMOS邏輯門由n型和p型MOSFET組成,它們在邏輯門的輸入端形成互補結構。CMOS技術具有以下特點:

1.1 低功耗:CMOS邏輯門在靜態狀態下幾乎不消耗功率,只有在輸入信號變化時才消耗少量功率。這使得CMOS技術在低功耗應用中具有優勢。

1.2 高集成度:CMOS技術可以實現高密度的集成電路設計,使得單個芯片上可以集成更多的邏輯門。

1.3 抗干擾能力:CMOS邏輯門具有較高的噪聲容限,可以在一定程度上抵抗外部干擾。

1.4 速度:CMOS邏輯門的速度受到晶體管尺寸和電源電壓的限制,通常比TTL邏輯門慢。

- TTL技術概述

TTL技術是一種使用雙極型晶體管(BJT)的數字邏輯技術。TTL邏輯門由NPN和PNP晶體管組成,它們在邏輯門的輸入端形成互補結構。TTL技術具有以下特點:

2.1 高速度:TTL邏輯門的開關速度較快,適用于高速數字電路設計。

2.2 功耗:TTL邏輯門在靜態狀態下消耗一定的功率,這使得其在低功耗應用中的性能不如CMOS技術。

2.3 抗干擾能力:TTL邏輯門的噪聲容限較低,對外部干擾較為敏感。

2.4 成本:TTL邏輯門的制造成本相對較低,適用于成本敏感的應用場景。

- CMOS和TTL的抗干擾能力比較

3.1 噪聲容限

CMOS邏輯門具有較高的噪聲容限,通常在0.7V至1.2V之間。這意味著CMOS邏輯門可以在一定程度上抵抗外部干擾,如電源波動、電磁干擾等。相比之下,TTL邏輯門的噪聲容限較低,通常在0.4V左右,對外部干擾較為敏感。

3.2 電源波動

CMOS邏輯門對電源波動的抗干擾能力較強。由于CMOS邏輯門在靜態狀態下幾乎不消耗功率,因此電源波動對其影響較小。而TTL邏輯門在靜態狀態下消耗一定的功率,電源波動可能導致其輸出不穩定。

3.3 電磁干擾

CMOS邏輯門對電磁干擾的抗干擾能力較強。CMOS邏輯門的輸入端由互補型MOSFET組成,其輸入阻抗較高,對電磁干擾的敏感度較低。而TTL邏輯門的輸入端由雙極型晶體管組成,其輸入阻抗較低,對電磁干擾的敏感度較高。

3.4 溫度影響

CMOS邏輯門對溫度變化的抗干擾能力較強。CMOS邏輯門的閾值電壓與溫度變化關系較小,因此溫度變化對其性能影響較小。而TTL邏輯門的閾值電壓與溫度變化關系較大,溫度變化可能導致其輸出不穩定。

- CMOS和TTL在不同應用場景下的抗干擾能力

4.1 低功耗應用

在低功耗應用中,CMOS技術具有明顯優勢。由于CMOS邏輯門在靜態狀態下幾乎不消耗功率,因此在低功耗應用中具有較高的抗干擾能力。而TTL邏輯門在靜態狀態下消耗一定的功率,其抗干擾能力相對較弱。

4.2 高速數字電路設計

在高速數字電路設計中,TTL技術具有優勢。TTL邏輯門的開關速度較快,適用于高速數字電路設計。然而,由于TTL邏輯門的噪聲容限較低,因此在高速應用中可能需要采取額外的抗干擾措施。

4.3 成本敏感應用

在成本敏感的應用場景中,TTL技術具有優勢。TTL邏輯門的制造成本相對較低,適用于成本敏感的應用場景。然而,由于TTL邏輯門的抗干擾能力較弱,可能需要在設計中考慮額外的抗干擾措施。

- 結論

綜上所述,CMOS和TTL技術在抗干擾能力方面存在顯著差異。CMOS技術具有較高的噪聲容限、對電源波動和電磁干擾的抗干擾能力較強,以及對溫度變化的抗干擾能力較強。然而,CMOS邏輯門的速度受到晶體管尺寸和電源電壓的限制,通常比TTL邏輯門慢。相比之下,TTL邏輯門的開關速度較快,但在抗干擾能力方面相對較弱。

-

CMOS

+關注

關注

58文章

5724瀏覽量

235707 -

TTL

+關注

關注

7文章

503瀏覽量

70311 -

晶體管

+關注

關注

77文章

9706瀏覽量

138495 -

邏輯技術

+關注

關注

0文章

3瀏覽量

5747

發布評論請先 登錄

相關推薦

電動工具直流調速專用集成電路GS069,具有電源電壓范圍寬、功耗小、抗干擾能力強等特性

如何提升無線模塊的抗干擾能力

VK1S68C是帶鍵盤掃描接口的點陣LED驅動控制專用芯片適用于要求可靠/穩定/抗干擾能力強的產品。

M451系列的抗干擾能力比M481幾乎強嗎?

LoRa模塊的抗干擾能力怎樣

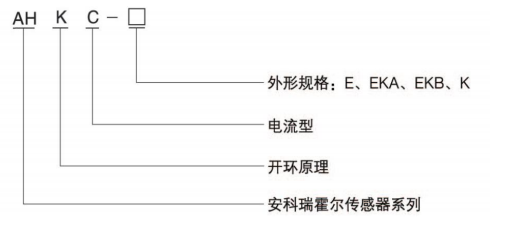

AHKC-EKBDA霍爾傳感器 響應快精度高 抗干擾能力強

cmos和ttl哪個抗干擾能力強

cmos和ttl哪個抗干擾能力強

評論