在FPGA(現場可編程門陣列)中實現狀態機是一種常見的做法,用于控制復雜的數字系統行為。狀態機能夠根據當前的輸入和系統狀態,決定下一步的動作和新的狀態。這里,我們將詳細探討如何在FPGA設計中實現狀態機,包括其基本概念、類型、設計步驟、實現方法以及優化策略。

一、狀態機基本概念

1.1 定義

狀態機(State Machine)是一種用于設計和實現算法和同步時序邏輯系統的方法。它由一組狀態、一個初始狀態、一組輸入信號、一組輸出信號以及定義狀態和輸出信號之間轉換的邏輯組成。

1.2 類型

- Mealy狀態機 :輸出不僅取決于當前狀態,還取決于輸入。

- Moore狀態機 :輸出僅取決于當前狀態,與輸入無關(但輸入影響狀態轉換)。

二、設計步驟

2.1 需求分析與規格定義

首先,明確狀態機的功能和性能要求,如輸入信號、輸出信號、狀態數量、轉換條件等。

2.2 狀態定義與轉換圖繪制

- 定義所有可能的狀態。

- 繪制狀態轉換圖(State Transition Diagram, STD),明確每個狀態轉換的條件和動作。

2.3 狀態編碼

選擇狀態編碼方式,如二進制編碼、格雷碼等。二進制編碼簡單直觀,但在狀態轉換時可能產生多個觸發器同時翻轉,導致功耗和噪聲問題;格雷碼相鄰狀態間只有一個位不同,有助于減少這些問題。

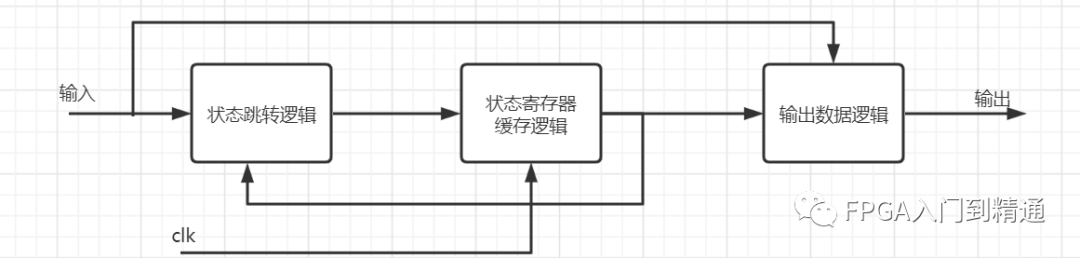

2.4 邏輯實現

- 根據狀態轉換圖和編碼方式,設計狀態轉換邏輯。

- 實現輸出邏輯,根據Mealy或Moore模型確定輸出與狀態和輸入的關系。

三、實現方法

3.1 硬件描述語言(HDL)

在FPGA設計中,主要使用VHDL或Verilog HDL來描述狀態機。以下是Verilog的一個簡單示例:

module state_machine(

input clk,

input reset,

input input_signal,

output reg output_signal

);

// 狀態定義

typedef enum reg [1:0] {

IDLE,

START,

PROCESS,

DONE

} state_t;

state_t current_state, next_state;

always @(posedge clk or posedge reset) begin

if (reset)

current_state <= IDLE;

else

current_state <= next_state;

end

// 狀態轉換邏輯

always @(*) begin

case (current_state)

IDLE:

if (input_signal) next_state = START;

else next_state = IDLE;

START:

next_state = PROCESS;

PROCESS:

// 假設處理需要一定時間或條件

if (/* some condition */) next_state = DONE;

else next_state = PROCESS;

DONE:

next_state = IDLE; // 回到初始狀態或保持當前狀態

default: next_state = IDLE;

endcase

end

// 輸出邏輯(以Moore為例)

always @(current_state) begin

case (current_state)

IDLE, START: output_signal = 0;

PROCESS: output_signal = 1; // 處理中

DONE: output_signal = 0; // 完成

endcase

end

endmodule

3.2 IP核和庫的使用

一些FPGA開發工具提供了狀態機IP核或庫函數,可以簡化設計過程。這些IP核可能已經優化過,能夠提供更好的性能和更低的資源消耗。

四、優化策略

4.1 最小化狀態數量

減少不必要的狀態可以減少邏輯復雜性和資源消耗。

4.2 優化狀態編碼

合理選擇狀態編碼方式,如格雷碼,以減少狀態轉換時的功耗和噪聲。

4.3 并行處理

如果可能,通過并行處理多個獨立的任務來加速狀態機的執行。

4.4 時鐘管理

優化時鐘頻率和時鐘樹,確保狀態機在穩定的時鐘域內運行,避免亞穩態問題。

4.5 功耗管理

通過時鐘門控、電源門控等技術降低非活動狀態下的功耗。

五、高級設計考慮

5.1 異步與同步設計

在FPGA設計中,狀態機可以是異步的也可以是同步的。然而,由于異步設計可能引入復雜的時序和亞穩態問題,大多數現代FPGA設計傾向于使用同步狀態機。同步狀態機使用全局時鐘信號來同步所有的狀態轉換和輸出更新,這有助于簡化時序分析并確保系統的穩定性和可預測性。

5.2 狀態機分解

對于復雜的狀態機,直接實現可能會變得難以管理和理解。為了解決這個問題,可以采用狀態機分解的方法。狀態機分解涉及將大型狀態機拆分成多個較小的、更易于管理的子狀態機。這些子狀態機可以在不同的模塊或進程中實現,并通過接口相互通信。通過狀態機分解,不僅可以提高代碼的可讀性和可維護性,還可以利用FPGA的并行處理能力來加速狀態機的執行。

5.3 錯誤檢測與恢復

在FPGA設計中,錯誤檢測與恢復是確保系統可靠性和穩定性的關鍵。對于狀態機而言,可以通過添加錯誤檢測邏輯來監控狀態轉換和輸出信號,并在檢測到錯誤時采取相應的恢復措施。例如,可以使用校驗和或CRC(循環冗余校驗)來驗證狀態轉換的正確性,并在發現錯誤時重置狀態機到已知的安全狀態。此外,還可以實現錯誤日志記錄功能,以便在系統出現故障時進行故障排查和診斷。

六、測試與驗證

6.1 單元測試

在FPGA設計中,單元測試是確保每個模塊或子狀態機正確工作的關鍵步驟。對于狀態機而言,單元測試應涵蓋所有可能的狀態轉換和輸入條件,以確保狀態機在各種情況下都能按預期工作。單元測試可以通過編寫測試向量和模擬輸入信號來執行,并使用仿真工具來觀察狀態機的輸出和狀態轉換是否符合預期。

6.2 集成測試

在完成所有模塊的單元測試后,需要進行集成測試以驗證整個系統或大型狀態機的協同工作。集成測試應模擬實際工作環境中的各種條件和場景,以確保狀態機在與其他模塊或子系統交互時能夠正確工作。集成測試通常需要使用更高級的仿真工具或測試平臺,以模擬更復雜的系統行為和外部接口。

6.3 硬件在環測試(HIL)

對于需要與實際硬件接口的狀態機,硬件在環測試是一種有效的驗證方法。HIL測試通過模擬實際硬件的行為并將FPGA設計與之接口連接,以驗證狀態機在實際工作環境中的性能和穩定性。HIL測試可以幫助發現由于硬件接口不匹配或信號完整性問題導致的潛在問題,并在實際部署之前進行修復。

七、實際應用案例

7.1 通信系統

在通信系統中,狀態機被廣泛用于控制數據包的接收、處理和發送過程。例如,在以太網交換機或路由器中,狀態機可以負責處理網絡幀的接收、解析、路由和轉發。這些狀態機需要能夠快速響應輸入信號(如網絡幀的到達)并根據當前狀態和網絡協議規則執行相應的操作。FPGA的高性能并行處理能力使其成為實現這些復雜狀態機的理想選擇。

7.2 工業自動化

在工業自動化領域,狀態機用于控制各種機械和設備的運動和行為。例如,在機器人控制系統中,狀態機可以負責機器人的運動規劃、路徑跟蹤和避障等功能。這些狀態機需要能夠實時處理來自傳感器和控制器的輸入信號,并根據機器人的當前位置和狀態執行相應的動作。FPGA的實時性和可編程性使得它成為實現這些高性能工業自動化控制系統的關鍵組件。

7.3 醫療設備

在醫療設備中,狀態機用于確保設備的正確操作和安全性。例如,在心臟起搏器或胰島素泵等醫療設備中,狀態機可以負責監控患者的生理參數并根據需要調整設備的輸出。這些狀態機需要具有高可靠性和低延遲的特點,以確保在緊急情況下能夠迅速響應并保護患者的生命安全。FPGA的可配置性和低功耗特性使其成為實現這些關鍵醫療設備中狀態機的理想平臺。

八、未來趨勢與展望

隨著FPGA技術的不斷發展和普及,狀態機在FPGA設計中的應用也將繼續擴大和深化。未來,我們可以期待以下幾個方面的趨勢和發展:

- 更高級的合成工具 :未來的FPGA設計工具將更加智能化和自動化,能夠自動生成優化后的狀態機代碼,并提供更全面的測試和驗證功能。

- 更強大的硬件資源 :隨著FPGA芯片制造工藝的進步和集成度的提高,未來的FPGA將擁有更多的邏輯單元、存儲資源和高速接口,這將為實現更復雜和高性能的狀態機提供有力支持。

- 更廣泛的應用領域 :隨著物聯網、人工智能和5G通信等技術的快速發展,狀態機將在更多領域中得到應用,如智能交通系統、智能家居、智能安防等。

- 安全性與可靠性 :隨著對系統安全性和可靠性的要求日益提高,未來的FPGA狀態機設計將更加注重安全性和可靠性方面的考慮。

九、結論

FPGA中的狀態機是實現復雜數字系統控制邏輯的重要工具。通過仔細規劃、設計、測試和驗證,可以構建出高效、可靠且靈活的狀態機來滿足各種應用需求。隨著技術的不斷進步和應用領域的不斷擴展,未來的FPGA狀態機設計將更加注重安全性、可靠性、高效能優化以及靈活性與可重構性等方面的考慮。這將為構建更加先進和強大的數字系統提供有力支持,并推動各個領域的技術創新和發展。

-

FPGA

+關注

關注

1642文章

21918瀏覽量

611871 -

觸發器

+關注

關注

14文章

2029瀏覽量

61755 -

狀態機

+關注

關注

2文章

493瀏覽量

27969

發布評論請先 登錄

相關推薦

FPGA工程師:如何在FPGA中實現狀態機?

如何在微型計算機中實現狀態機?

使用verilog HDL實現狀態機8位流水燈的程序和工程文件免費下載

經典雙進程狀態機的FPGA實現(含testbeach)

基于FPGA的狀態機設計

如何在FPGA中實現狀態機

如何在FPGA中實現狀態機

評論