來源:內容由RISC-V國際人才培養認證中心 編譯自DRAMSec,作者:Michele Marazzi;Kaveh Razavi。

蘇黎世聯邦理工學院的研究人員發表了一篇題為“RISC-H:針對 RISC-V 的 Rowhammer 攻擊”的新技術論文。RISC-H 將在DRAMSec(與 ISCA 2024 同期舉辦)上進行展示。

摘要:

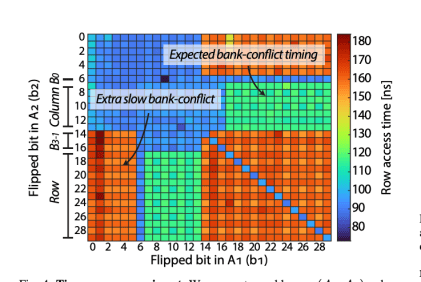

“就在幾個月前,首款支持DDR4的高端RISC-V CPU剛剛發布。目前尚無關于RISC-V設備上Rowhammer攻擊的研究,尚不清楚是否有可能在這些新架構上危害系統安全。通過RISC-H,我們旨在通過克服一系列挑戰來填補這一空白:首先,內存控制器的DRAM功能未公開,我們通過行沖突側信道進行逆向工程。其次,我們發現敲擊多行會導致激活吞吐量顯著降低,使Rowhammer攻擊失敗。

我們確定這種低性能是由內存子系統中攻擊行共享某些物理地址位和慢速排序指令時的爭用引起的。為了應對這一挑戰,我們利用不同的列地址來減少爭用,并依靠一種新穎的方法來通過在訪問模式中插入精確延遲來排序內存訪問。結合這些見解,我們新的Rowhammer攻擊,稱為RISC-H,可以觸發RISC-V CPU上的首個DDR4位翻轉。這些結果表明,RISC-V生態系統同樣受到Rowhammer的影響,并進一步強調了需要采取有效的緩解措施。”

圖 1:來源:RISC-H:Rowhammer 對 RISC-V 的攻擊。蘇黎世聯邦理工學院。

-

cpu

+關注

關注

68文章

10878瀏覽量

212169 -

內存控制器

+關注

關注

0文章

40瀏覽量

8904 -

RISC-V

+關注

關注

45文章

2292瀏覽量

46248

發布評論請先 登錄

相關推薦

麻省理工學院研發全新納米級3D晶體管,突破性能極限

麻省理工學院推出新型機器人訓練模型

美國佐治亞理工學院一行蒞臨達實智能調研

貴州理工學院采購南京大展的DZ-STA200同步熱分析儀

SynSense時識科技攜手蘇黎世聯邦理工發布Speck超低功耗眼動追蹤應用新突破

rIsc-v的缺的是什么?

麻省理工學院研發RoboGrocery系統,雜貨店自動化裝袋新篇章

淺析RISC-V領先ARM的優勢

感謝東莞理工學院對我司導熱系數測試儀的認可

RISC-V為何如此重要?

RISC-V有哪些優點和缺點

Imagination:RISC-V CPU的重要力量

瑞士蘇黎世聯邦理工學院新型四足機器人單腿完成開關門、移動任務

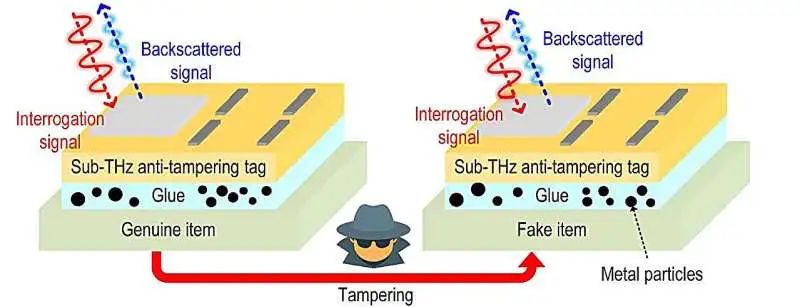

麻省理工學院開發出新的RFID標簽防篡改技術

蘇黎世聯邦理工學院報告:Rowhammer攻擊對高端RISC-V CPU的潛在風險

蘇黎世聯邦理工學院報告:Rowhammer攻擊對高端RISC-V CPU的潛在風險

評論