CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)集成電路是現(xiàn)代電子設(shè)計中使用最廣泛的技術(shù)之一,它以其低功耗、高集成度和可靠性而聞名。CMOS邏輯門,包括與非門(NAND gate),是構(gòu)成更復(fù)雜CMOS電路的基本構(gòu)建塊。與非門是一種基本的數(shù)字邏輯門,它實現(xiàn)了邏輯與和邏輯非的組合功能。

CMOS與非門的工作原理

與非門由一對互補(bǔ)的晶體管組成:一個N型MOSFET(NMOS)和一個P型MOSFET(PMOS)。當(dāng)輸入端為低電平時,PMOS晶體管導(dǎo)通,而NMOS晶體管截止;當(dāng)輸入端為高電平時,NMOS晶體管導(dǎo)通,PMOS晶體管截止。輸出端的電平由兩個晶體管的狀態(tài)決定,只有當(dāng)所有輸入端都為高電平時,輸出才為高電平;否則輸出為低電平。

CMOS與非門的輸入特性

CMOS與非門的輸入端可以接收兩種電平狀態(tài):邏輯“0”(低電平)和邏輯“1”(高電平)。邏輯“0”通常對應(yīng)于電路的地電平(GND),而邏輯“1”對應(yīng)于電源電壓(VDD)。CMOS電路設(shè)計時,輸入端的電平必須在規(guī)定的范圍內(nèi),以確保邏輯門能夠正確地工作。

CMOS與非門輸入接外部地的影響

理論上,CMOS與非門的輸入端可以直接接外部地,因為邏輯“0”就是由地電平表示的。然而,在實際應(yīng)用中,需要考慮以下幾個因素:

- 輸入保護(hù) :CMOS電路通常具有較薄弱的輸入保護(hù),直接接地可以,但需要確保輸入端不會因靜電放電(ESD)或其他瞬態(tài)電壓尖峰而損壞。

- 噪聲容限 :CMOS電路有一定的噪聲容限,即使輸入信號在邏輯“0”和邏輯“1”之間有小的波動,電路仍能正確識別電平狀態(tài)。但接地必須干凈,不應(yīng)引入額外的噪聲。

- 輸入電流 :雖然CMOS邏輯門的輸入電流非常小,但直接接地時,需要確保輸入端不會因外部電路而產(chǎn)生意外的電流。

- 電源穩(wěn)定性 :地線必須穩(wěn)定,不應(yīng)有電壓波動,否則可能影響與非門的邏輯判斷。

- 布局和布線 :在PCB設(shè)計中,與非門輸入端的接地應(yīng)盡可能短且寬,以減少阻抗并防止噪聲耦合。

CMOS與非門的典型應(yīng)用

- 數(shù)字邏輯電路 :與非門可以用于構(gòu)建各種組合邏輯電路,如解碼器、編碼器、多路復(fù)用器等。

- 信號處理 :在信號處理應(yīng)用中,與非門可以用于消除噪聲或?qū)崿F(xiàn)信號的邏輯控制。

- 接口電路 :與非門常用于微處理器和微控制器的接口電路,實現(xiàn)數(shù)據(jù)的緩沖和邏輯控制。

- 開關(guān)控制 :與非門可以用作電子開關(guān),控制其他電路的開啟和關(guān)閉。

CMOS與非門設(shè)計和使用的注意事項

- 電源管理 :確保VDD和GND的穩(wěn)定性,避免電源波動影響電路的工作。

- 輸入/輸出電平 :輸入電平必須在CMOS電路的規(guī)范范圍內(nèi),輸出電平應(yīng)適合后續(xù)電路的要求。

- 負(fù)載能力 :設(shè)計時要考慮與非門的負(fù)載能力,避免過載導(dǎo)致性能下降。

- 信號完整性 :在高速應(yīng)用中,需要考慮信號完整性問題,如反射、串?dāng)_和時序問題。

- 電磁兼容性(EMC) :設(shè)計時要考慮電磁兼容性,減少電磁干擾(EMI)的產(chǎn)生和敏感性。

- 熱設(shè)計 :CMOS電路在高頻率或高功耗下工作時,會產(chǎn)生熱量,需要適當(dāng)?shù)纳岽胧?/li>

結(jié)論

CMOS與非門是一種多功能的數(shù)字邏輯門,其輸入端可以直接接外部地,但需要考慮輸入保護(hù)、噪聲容限、電流影響、電源穩(wěn)定性和布局布線等因素。在設(shè)計和使用CMOS與非門時,還需要注意電源管理、電平匹配、負(fù)載能力、信號完整性、電磁兼容性和熱設(shè)計等方面的問題。

-

集成電路

+關(guān)注

關(guān)注

5391文章

11618瀏覽量

363018 -

CMOS

+關(guān)注

關(guān)注

58文章

5735瀏覽量

236033 -

與非門

+關(guān)注

關(guān)注

1文章

123瀏覽量

12811

發(fā)布評論請先 登錄

相關(guān)推薦

cmos和非門電路的輸入端電阻模式是什么

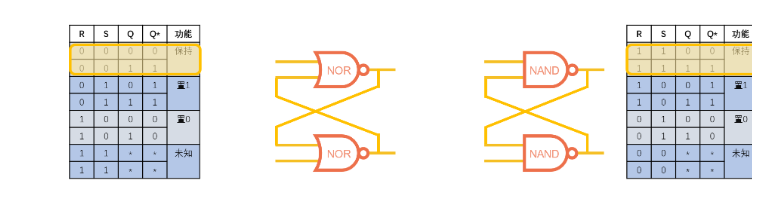

簡述基本與非門sr鎖存器的結(jié)構(gòu)及工作原理

與非門的閑置輸入端如何處理

TTL與非門閑置輸入端處理方法

為什么TTL與非門輸入端不能直接接電源或地?

CMOS集成電路的定義及特點?CMOS集成電路的保護(hù)措施有哪些?

四路2輸入正與非門數(shù)據(jù)表

CMOS 8-Input 與非門CD4068B TYPES 數(shù)據(jù)表

單電源 2 輸入正與非門 CMOS 邏輯電平轉(zhuǎn)換器SN74LV1T00數(shù)據(jù)表

基本rs觸發(fā)器與非門和或非門的區(qū)別

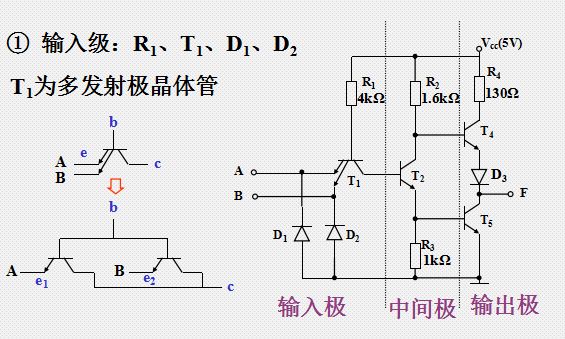

ttl與非門有哪些主要性能參數(shù) TTL與非門的工作原理

TTL與非門典型電路及其工作原理詳解

CMOS集成電路(與非門)輸入能直接接外部地嗎?

CMOS集成電路(與非門)輸入能直接接外部地嗎?

評論