I/Q原理及優(yōu)勢

對于有些通信類,光通信類以及射頻方向的同學(xué)都知道在通信的信號處理中,輸入的信號需要分成兩路(I路和Q路),也被稱作為正交調(diào)制信號。通常射頻信號需要將低頻的基帶信號搬移到高頻的載波信號上進(jìn)行傳輸,傳統(tǒng)方式是通過一個乘法器,將信號和載波進(jìn)行相乘,實(shí)現(xiàn)頻譜搬移。

cos(a)*cos(b)=1/2[cos(a+b)-cos(a-b)]

但是這樣會增加兩個多余的信號頻率。信號通常來說越純凈越好,也對后續(xù)的插值,濾波,檢波起決定性的作用。而且在濾波的過程中很難濾除另外一個頻率,也徒然增加頻帶,消耗寶貴的資源。所以I/Q正交調(diào)制技術(shù)才得以在通信領(lǐng)域大展拳腳。

Cos(a-b)=cos(a)*cos(b)+sin(a)*sin(b)

并且I/Q兩路信號可以降低采樣率,方便將信號采用復(fù)數(shù)信號的形式(z=a+bi),降低每個支路的采樣率,降低對ADC的要求,節(jié)省開發(fā)和成品的成本,很好的保留原始信號的相位信息。

FPGA中利用IP核實(shí)現(xiàn)I/Q信號的產(chǎn)生

Quartus中提供了一個IP核為DDIO IP,可供采集高速ADC傳入的數(shù)據(jù)后分成I/Q兩路信號。并且通常比數(shù)據(jù)處理時采用數(shù)據(jù)截位生成I/Q兩路數(shù)據(jù)方便高效。

DDIO IP核(雙倍數(shù)據(jù)速率IO)

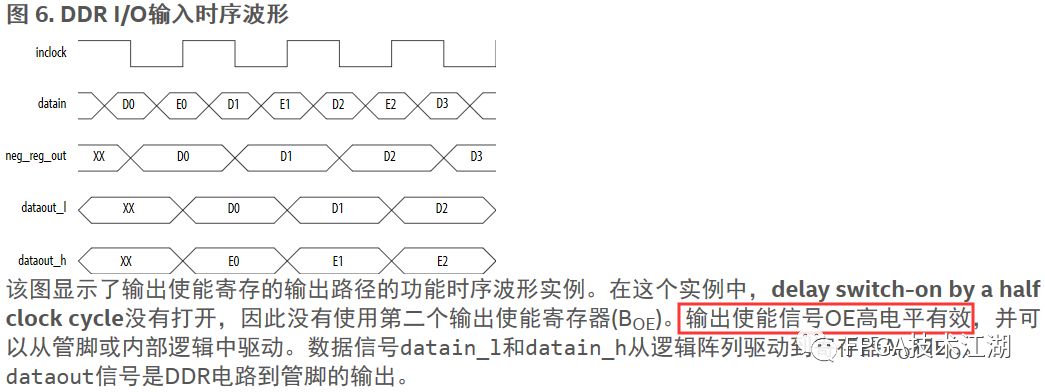

DDIO(Double Data Rate IO),IP核在邏輯單元(LE)中實(shí)現(xiàn)DDR寄存器,本程序中使用DDIO_IN實(shí)現(xiàn)一個DDR輸入接口,IP將在參考時鐘的上升沿和下降沿接收數(shù)據(jù),實(shí)現(xiàn)2倍的時鐘速率將數(shù)據(jù)鎖存。

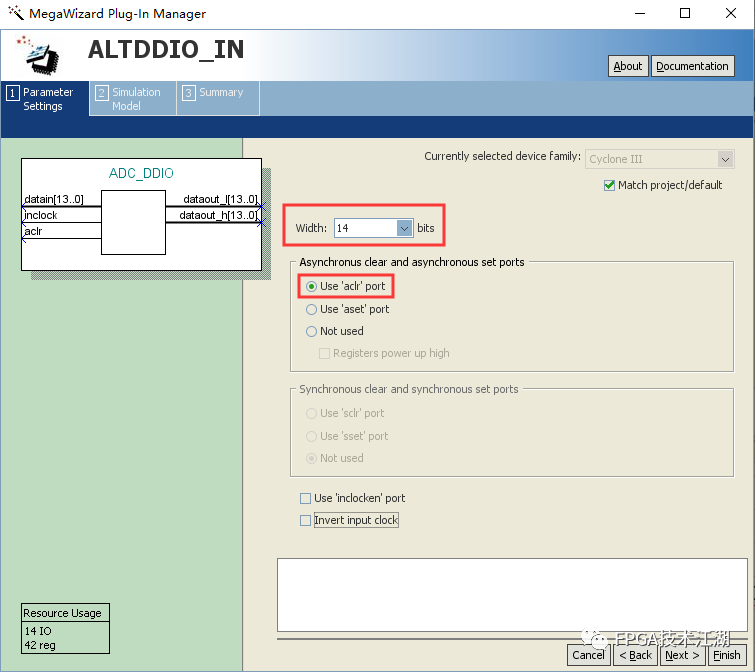

如果ADC選用的為14位,數(shù)據(jù)總線位寬選擇14bits,以及異步清零,未選擇數(shù)據(jù)使能端口,則數(shù)據(jù)的第一個bit將在輸入時鐘的下降沿被采集,反之將在上升沿被采集。

使用DDIO IP時需要注意OE信號在芯片中為低有效,但QuartusII軟件自動在輸出前添加一個反相器實(shí)現(xiàn)OE高電平有效,有需要可將OE轉(zhuǎn)換回低電平有效。

所以使用DDIO IP是通信中比較常見的一種做法,高速且精準(zhǔn)。產(chǎn)生的I/Q兩路信號可以直接傳輸數(shù)字下變頻(DDC)模塊中進(jìn)行處理,方便快捷。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1629文章

21750瀏覽量

604108 -

寄存器

+關(guān)注

關(guān)注

31文章

5357瀏覽量

120589 -

反相器

+關(guān)注

關(guān)注

6文章

311瀏覽量

43374 -

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65380 -

光通信

+關(guān)注

關(guān)注

19文章

881瀏覽量

34003

原文標(biāo)題:FPGA數(shù)字信號處理 通信類I/Q信號及產(chǎn)生

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Verilog中用*實(shí)現(xiàn)乘法和用乘法器ip核實(shí)現(xiàn)乘法的區(qū)別?

利用FPGA自帶的IP核實(shí)現(xiàn)雙口RAM用于2片MCU進(jìn)行數(shù)據(jù)交換時多次讀數(shù)據(jù)后RAM中數(shù)據(jù)變?yōu)榱?

調(diào)試一個項(xiàng)目芯片的輸入信號要用到I/Q差分輸入信號,由于設(shè)備限制不能產(chǎn)生I/Q差分輸入信號

采用PCI IP核實(shí)現(xiàn)碼流接收卡設(shè)計(jì)

一種基于FPGA的可配置FFT IP核實(shí)現(xiàn)設(shè)計(jì)

利用FPGA怎么實(shí)現(xiàn)數(shù)字信號處理?

在測控系統(tǒng)中用IP 核實(shí)現(xiàn)D/A 轉(zhuǎn)換

在測控系統(tǒng)中用IP核實(shí)現(xiàn)D/A轉(zhuǎn)換

FPGA在雷達(dá)信號模擬器中的應(yīng)用

在測控系統(tǒng)中用IP核實(shí)現(xiàn)D/A轉(zhuǎn)換

在FPGA中利用IP核實(shí)現(xiàn)I/Q信號的產(chǎn)生

在FPGA中利用IP核實(shí)現(xiàn)I/Q信號的產(chǎn)生

評論