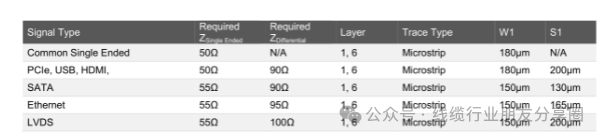

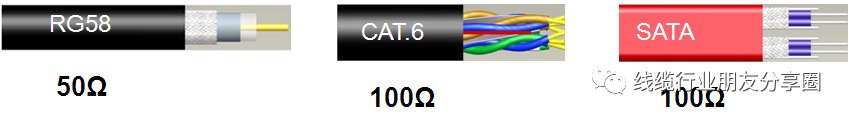

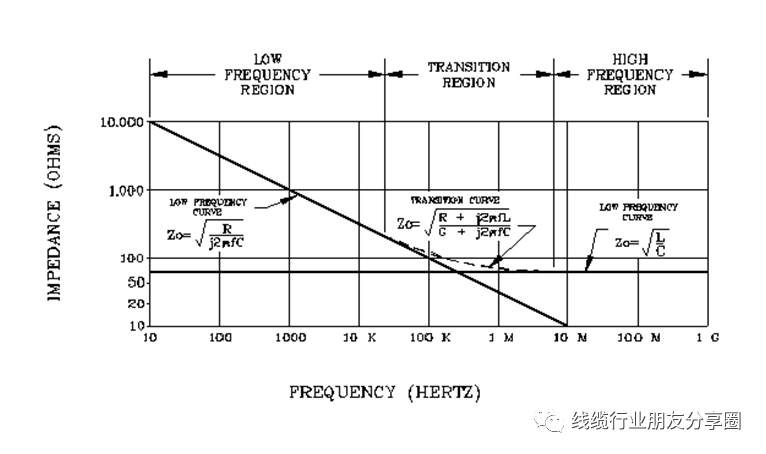

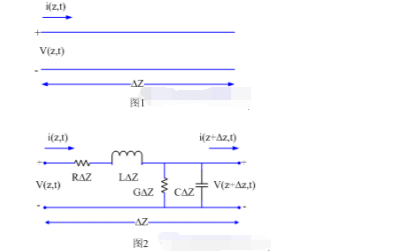

特征阻抗這個(gè)名詞是對(duì)于交流信號(hào)(或者說高頻信號(hào))來說的;特征阻抗屬于長線傳輸中的一個(gè)概念,信號(hào)在傳輸線中傳輸?shù)倪^程中,在信號(hào)到達(dá)的一個(gè)點(diǎn),傳輸線和參考平面之間會(huì)形成電場,由于電場的存在,會(huì)產(chǎn)生一個(gè)瞬間的小電流,這個(gè)小電流在傳輸線中的每一點(diǎn)都存在。同時(shí)信號(hào)也存在一定的電壓,這樣在信號(hào)傳輸過程中,傳輸線的每一點(diǎn)就會(huì)等效成一個(gè)電阻,這個(gè)電阻就是我們提到的傳輸線的特征阻抗。如今,高速系統(tǒng)面臨著許多必須在同一堆疊中實(shí)現(xiàn)的同步阻抗要求 ;如以太網(wǎng)的100歐姆差分阻抗,90歐姆的USB,85歐姆的PCIe以及無數(shù)的單端DDR要求。我們希望遵循規(guī)范,以正確的阻抗選擇組件和布線走線。然而,有時(shí)也存在一些障礙——首選元件不是85歐姆,或者上游封裝是另一種阻抗。規(guī)范怎么說?我上傳了如下圖片有常用接口的阻抗要求,可以參考一下;

什么樣的信號(hào)線需要50歐姆阻抗,85歐姆阻抗,90歐姆阻抗,100歐姆阻抗

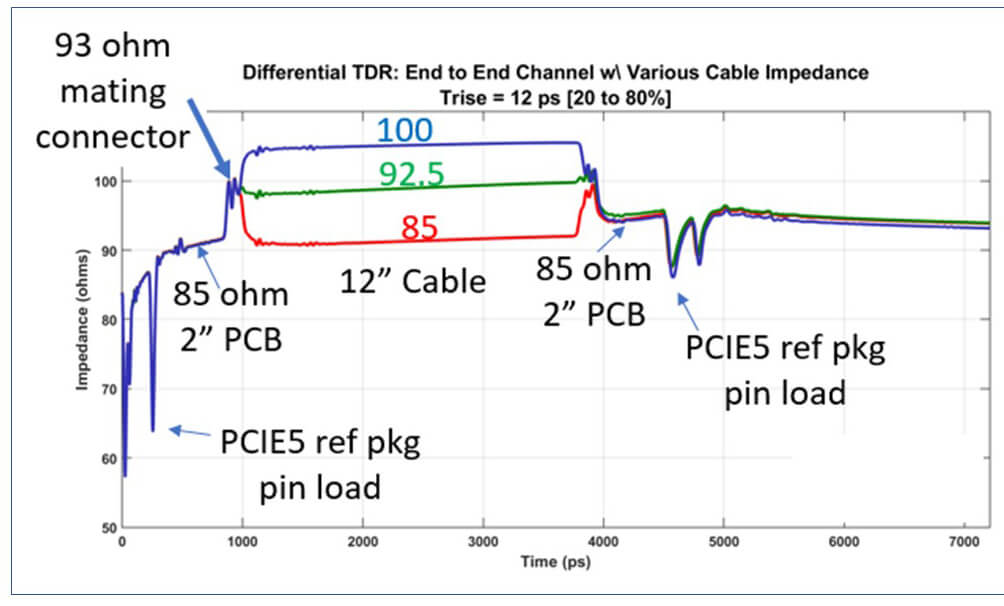

我們知道,較高的阻抗,插入損耗會(huì)比較好(衰減會(huì)比較小),之前我們做過數(shù)據(jù)分析,85歐姆和100歐姆阻抗之間的損耗差高達(dá)14%。而較高阻抗的PCB確又有具有更大的損耗;也就是說,阻抗和損耗之間的關(guān)系與PCB關(guān)系又成反比。舉例:目前PCIE平行對(duì)的線材阻抗有85歐姆和100歐姆兩種,看了一個(gè)關(guān)于PCI Express Layout gudie的文檔,其中關(guān)于阻抗的要求PCI Express link traces must maintain 100 ? differential / 60 ? single-ended impedancefor 4-layer or 6-layer boards; and 85 ? differential / 55 ? single-ended impedance for 8-layer or 10-layer boards. 這里就提到PCB板層不一樣會(huì)有不同的阻抗要求;按照行業(yè)數(shù)據(jù)分析,PCB板子的層數(shù)多了,層間距小了,要滿足原來的阻抗要求就可能導(dǎo)致走線太細(xì),不能滿足工藝要求,所以適當(dāng)?shù)亟档妥杩鼓繕?biāo)值來保證有足夠的走線寬度。這個(gè)主要是方便布線;4~6層主力布線層是top/botm,85Ω在表層線寬/間距會(huì)很大,100Ω的就會(huì)好很多。降低阻抗后,負(fù)載變重,抗干擾能力要強(qiáng)一點(diǎn)。4到6層板布線都在外層,需要考慮抗干擾能力;強(qiáng)制疊層和線寬間距的情況下,8層板厚度減少,阻抗就變低.

阻抗的概念和重要性

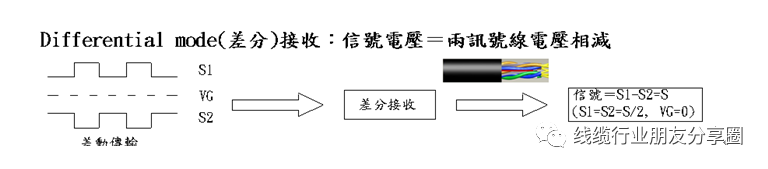

在測同一被測線材時(shí),其阻抗會(huì)因在該被測線材上傳輸?shù)男盘?hào)型式不同,而分為單端阻抗,同模(共模)阻抗及差分阻抗,其差異主要表現(xiàn)在測試的信號(hào)條件上。將傳輸線始端的輸入阻抗簡稱為阻抗;將信號(hào)隨時(shí)遇到的及時(shí)阻抗稱為瞬時(shí)阻抗如果傳輸線具有恒定不變的瞬時(shí)阻抗,就稱之為傳輸線的特性阻抗;和電阻,電容,電感一樣,傳輸線也是一種理想的電路元件,但是其特性卻大不相同,用于仿真效果較好,但電路概念卻比較復(fù)雜;依傳輸?shù)挠嵦?hào)型式不同.單端阻抗 Zse (Single Ended):差動(dòng)阻抗 Zdiff (Differential Mode);同模阻抗 Zcom (Common Mode).

早期的數(shù)字總線大部分使用單端信號(hào)做信號(hào)傳輸,如TTL/CMOS信號(hào)都是單端信號(hào)。所謂單端信號(hào),是指用一根信號(hào)線的高低電平的變化來進(jìn)行0、1信息的傳輸,這個(gè)電平的高低變化是相對(duì)于其公共的參考地平面的。單端信號(hào)由于結(jié)構(gòu)簡單,可以用簡單的晶體管電路實(shí)現(xiàn),而且集成度高、功耗低,因此在數(shù)字電路中得到最廣泛的應(yīng)用。

當(dāng)信號(hào)傳輸速率更高時(shí),為了減小信號(hào)的跳變時(shí)間和功耗,信號(hào)的幅度一般都會(huì)相應(yīng)減小。比如以前大量使用的5V的TTL信號(hào)現(xiàn)在使用越來越少,更多使用的是3.3V/2.5V/1.8V/1.5V/1.2V的LVTTL電平,但是信號(hào)幅度減小帶來的問題是對(duì)噪聲的容忍能力會(huì)變差一些。進(jìn)一步的,很多數(shù)字總線現(xiàn)在需要傳輸更長的距離,從原來芯片間的互連變成板卡間的互連甚至設(shè)備間的互連,信號(hào)穿過不同的設(shè)備時(shí)會(huì)受到更多噪聲的干擾。更極端的情況是收發(fā)端的參考地平面可能也不是等電位的。

因此,當(dāng)信號(hào)速率變高、傳輸距離變長后仍然使用單端的方式進(jìn)行信號(hào)傳輸會(huì)帶來很大的問題。為了提高信號(hào)在高速率、長距離情況下傳輸?shù)目煽啃裕蟛糠指咚俚臄?shù)字串行總線都會(huì)采用差分信號(hào)進(jìn)行信號(hào)傳輸。差分信號(hào)是用一對(duì)反相的差分線進(jìn)行信號(hào)傳輸,發(fā)送端采用差分的發(fā)送器,接收端相應(yīng)采用差分的接收器。采用差分傳輸方式后,由于差分線對(duì)里正負(fù)信號(hào)的走線是緊密耦合在一起的,所以外界噪聲對(duì)于兩根信號(hào)線的影響是一樣的。而在接收端,由于其接收器是把正負(fù)信號(hào)相減的結(jié)果做為邏輯判決的依據(jù),因此即使信號(hào)線上有嚴(yán)重的共模噪聲或者地電平的波動(dòng),對(duì)于最后的邏輯電平判決影響很小。

相對(duì)于單端傳輸方式,差分傳輸方式的抗干擾、抗共模噪聲能力大大提高。采用差分方式進(jìn)行信號(hào)傳輸會(huì)使得收發(fā)端的電路變得復(fù)雜,系統(tǒng)的功耗也隨之上升,但是由于其優(yōu)異的抗干擾能力以及可靠的傳輸特性,使得差分傳輸方式在需要進(jìn)行高速數(shù)字信號(hào)的傳輸或者惡劣工作環(huán)境的領(lǐng)域得到了廣泛的應(yīng)用,如LVDS、PCI-E、SATA、USB、1394、CAN、Flexray等總線都是采用差分的信號(hào)傳輸方式。

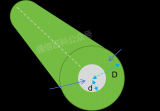

一般而言儀器的端口是以單端50Ω的阻抗最為常見。如欲以NA量測“差分訊號(hào)”時(shí),需經(jīng)由Bulan轉(zhuǎn)換將NA的“單端訊號(hào)”轉(zhuǎn)換成差分訊號(hào)。TDR的“單端訊號(hào)”轉(zhuǎn)成“差分訊號(hào)”或“同模訊號(hào)”時(shí),只需設(shè)定儀器端口即可。其實(shí),阻抗匹配的概念并不止于此,如果將兩段均勻的同軸電纜連接起來,在連接點(diǎn)處如果“加工”工藝視屏高,金屬銜接平順,沒有出現(xiàn)微觀結(jié)構(gòu)意義上的阻抗突變現(xiàn)象,則我們也把這兩段同軸線的連接也稱作匹配。

推而廣之,凡是阻抗連續(xù)的連接點(diǎn)我們都說它們是“匹配”的。按照這個(gè)思路,我們就知道通常在雙絞線和模塊的連接點(diǎn)處,阻抗是很可能有“失配”現(xiàn)象存在的,一條布線鏈路中的接插件和連接件所在的位置經(jīng)常也是阻抗不連續(xù)的位置(或者說是阻抗失配的位置)。不連續(xù)的原因主要是傳輸線的幾何結(jié)構(gòu)或材質(zhì)(包含絕緣介質(zhì)的材質(zhì))發(fā)生了突變。凡是阻抗不連續(xù)點(diǎn),也“一定是”一個(gè)信號(hào)能量的反射點(diǎn)(回波源)。對(duì)于產(chǎn)品設(shè)計(jì)和生產(chǎn)商來說,就是要制作出連接點(diǎn)阻抗盡量平順連續(xù)的產(chǎn)品 —模塊、跳線、各種工業(yè)連接器、各種異型非標(biāo)接插件等等。

-

CMOS

+關(guān)注

關(guān)注

58文章

5724瀏覽量

235686 -

PCB板

+關(guān)注

關(guān)注

27文章

1449瀏覽量

51742 -

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65397 -

TTL電平

+關(guān)注

關(guān)注

1文章

99瀏覽量

12028 -

差分阻抗

+關(guān)注

關(guān)注

1文章

26瀏覽量

10392

原文標(biāo)題:什么樣的信號(hào)線需要50歐姆阻抗,85歐姆阻抗,90歐姆阻抗,100歐姆阻抗,阻抗的重要性?

文章出處:【微信號(hào):線纜行業(yè)朋友分享圈,微信公眾號(hào):線纜行業(yè)朋友分享圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AppCAD計(jì)算天線信號(hào)線特性阻抗

你能想象嗎,傳輸線能控到多少阻抗還要看隔壁信號(hào)線的臉色?

射頻系統(tǒng)中的50歐姆特性阻抗

TE Connectivity的Z-PackTinMan100歐姆和85歐姆連接器,占位阻抗易匹配

射頻系統(tǒng)中的50歐姆特性阻抗詳細(xì)介紹

如何使用AppCAD實(shí)現(xiàn)計(jì)算天線信號(hào)線特性阻抗

PCB阻抗設(shè)計(jì)匹配的理想模型及方法

射頻為什么50歐姆 射頻阻抗為什么是50歐姆

RF射頻電路為什么選取50歐姆作為阻抗匹配的數(shù)值呢?

PCB如何進(jìn)行50歐姆匹配

差分阻抗為什么是100歐姆

為什么是50歐姆,50歐姆阻抗的來源和意義

什么樣的信號(hào)線需要50歐姆阻抗,85歐姆阻抗?

什么樣的信號(hào)線需要50歐姆阻抗,85歐姆阻抗?

評(píng)論