鍺(Ge)探測(cè)器是硅基光電子芯片中實(shí)現(xiàn)光電信號(hào)轉(zhuǎn)化的核心器件。在硅基光電子芯片工藝中實(shí)現(xiàn)異質(zhì)單片集成高性能Ge探測(cè)器工藝,是光模塊等硅基光電子產(chǎn)品實(shí)現(xiàn)小體積、低成本和易制造的優(yōu)先選擇。硅基光電子芯片集成Ge探測(cè)器主要挑戰(zhàn)在于熱預(yù)算兼容、金屬污染防控及工藝結(jié)構(gòu)的匹配三個(gè)方面。

據(jù)麥姆斯咨詢報(bào)道,聯(lián)合微電子中心有限責(zé)任公司研究團(tuán)隊(duì)探討了硅基光電子芯片集成Ge探測(cè)器在實(shí)際工藝中遇到的挑戰(zhàn)和解決思路。相關(guān)研究?jī)?nèi)容以“硅基光電子工藝中集成鍺探測(cè)器的工藝挑戰(zhàn)與解決方法”為題發(fā)表在《數(shù)字技術(shù)與應(yīng)用》期刊上。

硅光集成Ge探測(cè)器簡(jiǎn)介

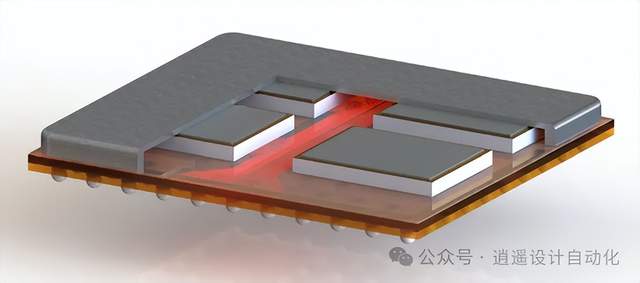

數(shù)據(jù)中心內(nèi)使用光纖通信以及由硅基光電子芯片封裝的光收發(fā)器是一個(gè)非常有吸引力的選擇,在短距離互連中可以顯著降低收發(fā)器模塊的功耗、成本和尺寸。硅基光電子芯片基于成熟的CMOS集成電路工藝技術(shù)、可在晶圓上大規(guī)模集成,成本低,產(chǎn)量大,且在重復(fù)性和良率上表現(xiàn)優(yōu)異。同時(shí)依靠先進(jìn)的封裝技術(shù)及相關(guān)產(chǎn)業(yè)的基礎(chǔ)條件,為大規(guī)模制造硅基光電子收發(fā)器模塊提供了成熟的生產(chǎn)解決方案。

PIN光電探測(cè)器是硅基光電子芯片中的核心器件之一,其較PN節(jié)探測(cè)器多了一層I型本征層作為產(chǎn)生光電流的吸收光輻射區(qū),從而實(shí)現(xiàn)小結(jié)電容,短渡越時(shí)間和高靈敏度。在高速光通信中,不僅依賴于芯片之間的通信,還需要實(shí)現(xiàn)芯片上組件之間的通信,然而,大多數(shù)信號(hào)處理,特別是數(shù)據(jù)存儲(chǔ)仍然是以電信號(hào)的模式存在,這意味著實(shí)現(xiàn)光信號(hào)到電信號(hào)快速轉(zhuǎn)換的PIN光電探測(cè)器在發(fā)射器和接收器上是必要的。

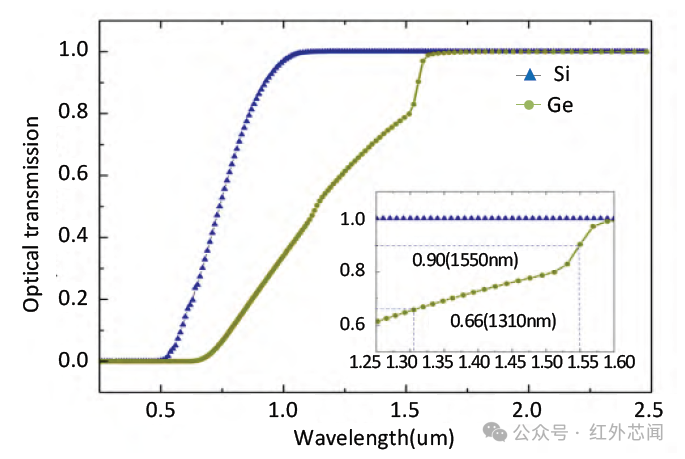

如圖1所示,硅對(duì)1100 nm以上波長透明,在通信波段可以實(shí)現(xiàn)較低損耗的光信號(hào)傳輸,但不適合用于光電探測(cè)器制造。Ge的帶隙為0.67 eV,同時(shí)是直接帶隙,在近紅外波段有著較高的吸收系數(shù),是工作波長為1310 nm(O波段)和1550 nm(C波段)的光電探測(cè)器首選的吸收材料。Ge的光電探測(cè)器可在高頻下工作,響應(yīng)度高,同時(shí)Ge與硅基CMOS集成電路制造工藝兼容,被廣泛用于光電探測(cè)器的制造。

圖1 根據(jù)光學(xué)常數(shù)計(jì)算的厚度為500nm的Si和Ge的透光率

長期以來,硅基光電子以SOI(絕緣層上硅)為主要集成平臺(tái),利用該平臺(tái)可實(shí)現(xiàn)高密度的多種硅光無源器件和有源器件集成。硅基光電子芯片集成Ge探測(cè)器同樣是基于SOI平臺(tái),由于Ge熔點(diǎn)較其他半導(dǎo)體材料低,集成時(shí)首先就要解決其熱預(yù)算兼容的問題。Ge選擇性外延工藝溫度較高,在金屬段集成易造成污染,同時(shí)其為半金屬,要避免與其他工藝的交叉污染,需要綜合考慮金屬污染防控問題。最后為了不影響其他器件設(shè)計(jì)及性能,工藝結(jié)構(gòu)也必須匹配。

集成Ge探測(cè)器的工藝挑戰(zhàn)與解決方法

熱預(yù)算兼容

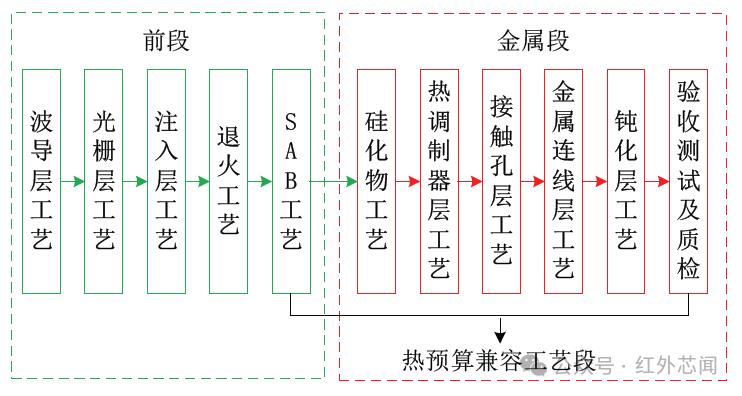

先進(jìn)半導(dǎo)體工藝會(huì)對(duì)其熱工藝制程進(jìn)行嚴(yán)格的控制,以避免過多的熱預(yù)算造成摻雜離子的過度擴(kuò)散,從而導(dǎo)致器件性能退化或失效。在硅基光電子工藝中集成Ge探測(cè)器時(shí),還需要考慮工藝對(duì)Ge材料的兼容問題。如圖2所示,為了實(shí)現(xiàn)有源器件的電學(xué)功能,常規(guī)的注入工藝之后,需要對(duì)其摻雜離子進(jìn)行退火激活,其典型的退火工藝溫度約1000 ℃,但Ge的熔點(diǎn)僅有938 ℃,如果在注入退火工藝之前集成必然會(huì)造成Ge探測(cè)器熔化失效,Ge工藝必須在注入和退火工藝后進(jìn)行。

但將Ge工藝整合在注入之后需要解決注入Si損傷問題。高能量劑量的注入會(huì)對(duì)Si造成損傷,導(dǎo)致Ge外延時(shí)產(chǎn)生大量缺陷甚至出現(xiàn)無法外延的情況。通過長時(shí)間的低溫退火,或者生長一層薄的熱氧然后通過稀氫氟酸清洗可以修復(fù)Si損傷,并獲得高質(zhì)量Ge器件。

圖2 硅光工藝流程示意圖

在另一方面,Ge外延同樣是一個(gè)熱過程,其會(huì)造成已注入離子的再次擴(kuò)散,特別是離子半徑小的元素,比如B,其擴(kuò)散過程會(huì)更加劇烈,有導(dǎo)致有源器件性能退化的風(fēng)險(xiǎn)。降低Ge工藝溫度可以避免摻雜離子的過度擴(kuò)散,但會(huì)導(dǎo)致Ge器件中螺位錯(cuò)無法有效消除,這些位錯(cuò)是由于Ge和Si之間約4%的晶格失配引起,其會(huì)生成少數(shù)載流子,導(dǎo)致暗電流增加。Ge外延工藝溫度需要綜合考慮Ge探測(cè)器和其他有源器件的性能,尋找一個(gè)最佳平衡點(diǎn)。

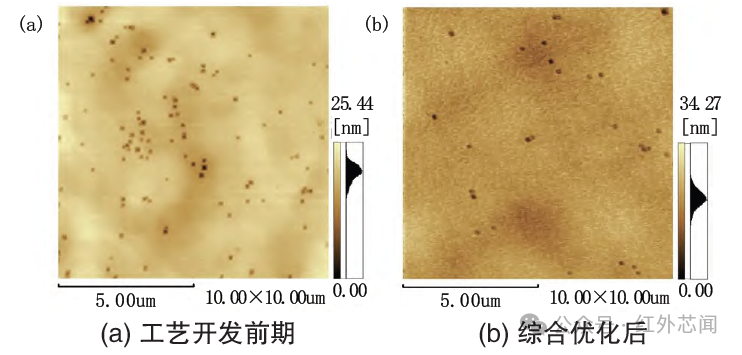

此外,綜合考慮Ge外延工藝的熱預(yù)算,提前對(duì)有源器件設(shè)計(jì),注入工藝和摻雜離子選擇做針對(duì)性的優(yōu)化同樣可以避免Ge探測(cè)器集成對(duì)其他有源器件的影響。如圖3所示,通過原子力顯微鏡(AFM)表征了工藝開發(fā)前期及綜合優(yōu)化后Ge外延薄膜的位錯(cuò)分布,其位錯(cuò)密度由10? /cm2 減少到10? /cm2數(shù)量級(jí),在保障其他器件性能的同時(shí),有效地降低了Ge探測(cè)器中暗電流的產(chǎn)生。

圖3 AFM下外延Ge中的位錯(cuò)分布

金屬污染防控

金屬污染對(duì)于半導(dǎo)體工藝是致命的,會(huì)造成可靠性和良率的降低,器件失效,甚至是給生產(chǎn)線帶來不可逆轉(zhuǎn)的損害。對(duì)于Ge探測(cè)器而言,金屬離子擴(kuò)散進(jìn)入Ge晶格后,會(huì)形成缺陷,產(chǎn)生中間能級(jí),導(dǎo)致探測(cè)器暗電流增大。將Ge探測(cè)器集成控制在金屬材料相關(guān)工藝之前可以最大限度地避免金屬段設(shè)備對(duì)Ge器件的污染。

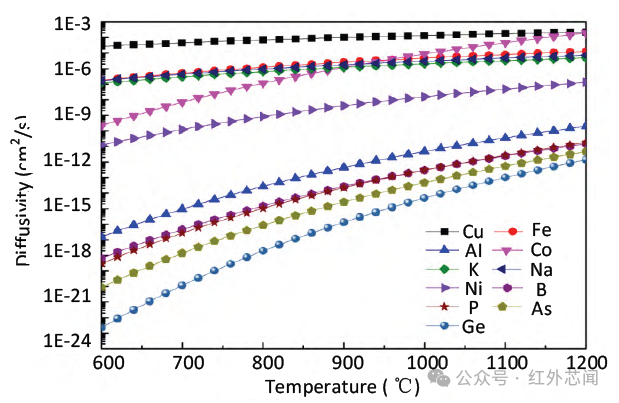

更重要的,Ge外延工藝是一個(gè)相對(duì)高溫過程,超過金屬Al的熔點(diǎn),如果在金屬Al工藝之后進(jìn)行Ge集成,會(huì)造成器件失效,同時(shí)帶來嚴(yán)重的設(shè)備交叉污染風(fēng)險(xiǎn)。此外,如圖4所示,金屬離子在晶圓中的擴(kuò)散系數(shù)會(huì)隨著溫度呈指數(shù)變化,在高溫過程中,作為降低接觸電阻的金屬硅化物元素,如:Co或Ni會(huì)擴(kuò)散到硅光器件的各個(gè)位置,形成光吸收中心或者P-N節(jié)漏電流,從而進(jìn)一步造成硅光器件光損耗異常甚至失效。

圖4 不同元素?cái)U(kuò)散系數(shù)隨溫度變化曲線

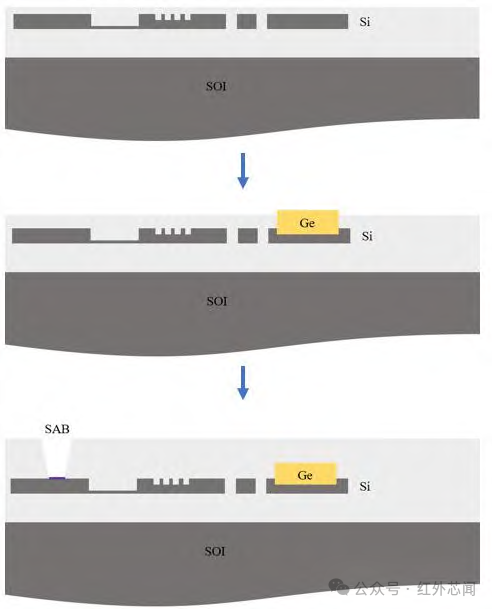

工藝結(jié)構(gòu)匹配

考慮到Ge探測(cè)器集成需要在完成離子注入退火后以及金屬段之前,同時(shí)由于Ge是一種半金屬,還要避免Ge的交叉污染,需要盡可能靠近金屬段,綜合考慮工藝架構(gòu)匹配,將探測(cè)器集成與SAB(Salicide Block,自對(duì)準(zhǔn)硅化物區(qū)域阻擋層)工藝段前為最優(yōu)。首先可以通過SAB阻擋層將Ge探測(cè)器保護(hù)起來;其次SAB為最靠近金屬段的光刻層,可以最大限度地避免Ge交叉污染。SAB主要用于降低接觸孔和器件之間的接觸電阻。如圖5所示,在完成硅光前段工藝之后,SAB工藝之前,沉積一層氧化硅作為Ge外延生長的硬掩模,通過光刻和刻蝕將Ge器件圖形轉(zhuǎn)移到硬掩模上,這個(gè)過程中,為了器件性能的穩(wěn)定性,對(duì)刻蝕深度的一致性有較高要求。

圖5 硅基光電子芯片集成Ge探測(cè)器示意圖

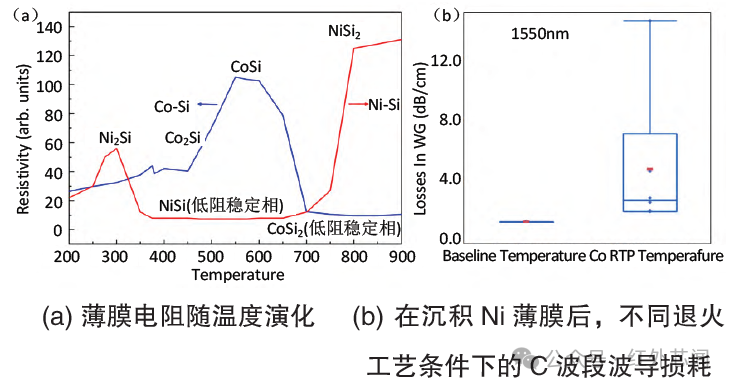

如圖6(a)所示,為了進(jìn)一步提升器件性能,通過采用工藝溫度較低的鎳的硅化物(NiSi,工藝溫度約400℃)替代工藝溫度較高的鈷的硅化物(CoSi?,工藝溫度約800℃),來降低后續(xù)工藝溫度對(duì)探測(cè)器的和其他硅光器件的影響。如圖6(b)所示,采用Ni作為生成硅化物的金屬,分別采用Ni和Co工藝的退火條件得到C波段的波導(dǎo)損耗,其中,Ni工藝退火條件的波導(dǎo)損耗在1.4 dB/cm左右,數(shù)據(jù)收斂;而Co工藝退火條件的波導(dǎo)損耗明顯偏高,嚴(yán)重影響硅基光電子芯片性能。

圖6 Ni-Si和Co-Si工藝對(duì)比

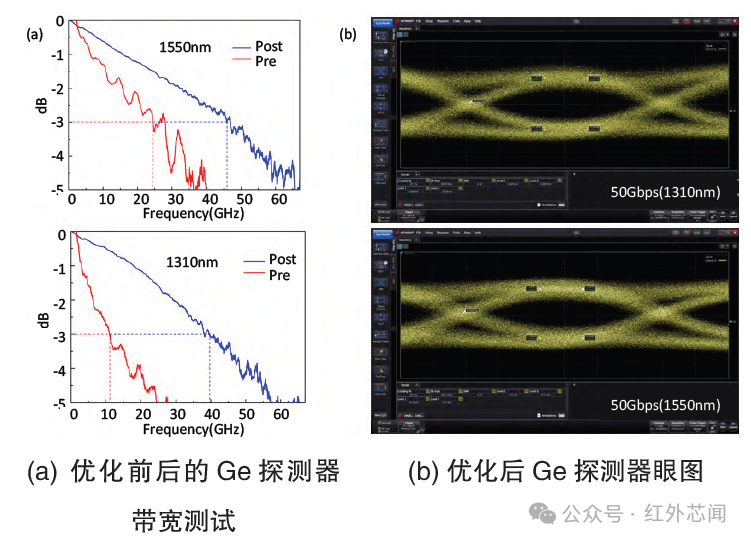

研究人員在CUMEC的中試線上開發(fā)了硅光SOI集成Ge探測(cè)器工藝,通過不斷對(duì)Ge集成工藝和設(shè)計(jì)的迭代優(yōu)化,實(shí)現(xiàn)了Ge探測(cè)器的工藝集成,其TEM(透射電子顯微鏡)截面圖如圖7所示,并對(duì)其器件性能進(jìn)行了表征,其性能表現(xiàn)優(yōu)異。圖8展示了優(yōu)化后Ge探測(cè)器性能提升。

圖7 Ge探測(cè)器TEM截面圖

圖8 優(yōu)化后Ge探測(cè)器性能

結(jié)語

全球各地的數(shù)據(jù)中心呈爆發(fā)式發(fā)展,硅基光電子芯片有望大幅降低其成本與功耗,其核心器件Ge探測(cè)器的集成主要面臨三個(gè)方面的工藝挑戰(zhàn):熱預(yù)算兼容、金屬污染防控及工藝結(jié)構(gòu)匹配,將探測(cè)器集成在SAB工藝段前是解決該挑戰(zhàn)的關(guān)鍵。通過綜合優(yōu)化器件和工藝設(shè)計(jì),尋找最佳Ge外延溫度,并對(duì)其金屬污染進(jìn)行嚴(yán)格管控以及采用對(duì)硅光器件更為友好的Ni金屬硅化物方案等,實(shí)現(xiàn)了高性能的Ge探測(cè)器的工藝集成。

論文信息:

DOI: 10.19695/j.cnki.cn12-1369.2023.08.46

審核編輯:劉清

-

集成電路

+關(guān)注

關(guān)注

5388文章

11554瀏覽量

361911 -

CMOS

+關(guān)注

關(guān)注

58文章

5721瀏覽量

235557 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3429瀏覽量

106015 -

探測(cè)器

+關(guān)注

關(guān)注

14文章

2642瀏覽量

73039 -

電子芯片

+關(guān)注

關(guān)注

3文章

57瀏覽量

15022

原文標(biāo)題:硅基光電子工藝中集成鍺探測(cè)器的工藝挑戰(zhàn)與解決方法

文章出處:【微信號(hào):MEMSensor,微信公眾號(hào):MEMS】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

硅鍺材料、硅退火片和絕緣體上硅(SOI)的介紹

推進(jìn)光電子集成芯片封裝技術(shù)

金屬探測(cè)器的常見故障及解決方法

光電探測(cè)器的工作原理、種類及特性

紅外探測(cè)器封裝秘籍:高可靠性鍵合工藝全解析

光電探測(cè)器和硅光電池一樣嗎?

國信光電子創(chuàng)新中心發(fā)布首款2Tb/s硅光互連芯粒

石墨烯/硅基異質(zhì)集成光電子器件綜述

微波光子集成芯片和硅基光子集成芯片的區(qū)別

光電子集成芯片是什么

基于一種納米金屬粒子梯度摻雜的復(fù)合材料設(shè)計(jì)

可片上探測(cè)和預(yù)處理的仿生視聽光電探測(cè)器

硅基異質(zhì)集成工藝的簡(jiǎn)介

硅基光電子工藝中集成鍺探測(cè)器的工藝挑戰(zhàn)與解決方法簡(jiǎn)介

硅基光電子工藝中集成鍺探測(cè)器的工藝挑戰(zhàn)與解決方法簡(jiǎn)介

評(píng)論