使用OVM6946和OV426設(shè)計內(nèi)窺鏡吧!

決戰(zhàn)1mm,OVM6946內(nèi)窺FPGA方案開源

這篇來寫硬件分析,這篇文章是個大的雜合體,如果有什么不對的地方請指教。

主要是我沒有大哥FPGA的功力,我只能用現(xiàn)成的轉(zhuǎn)換方案了。

但是所有的方案都是流式處理,對于圖像處理來說,永遠都是等著前一級的處理完才能干活。

所以都是:橋接處理器(同步輸出),數(shù)字信號將被圖像信號處理器(ISP)處理,最后輸出圖像數(shù)據(jù)。

其中中低端的內(nèi)窺鏡用圖像傳感器,主要是以O(shè)V的為主:

有OV6946+OV426、OV6948+OV426、OV9734、OH02A1S(帶近紅外增強)、OH0TA10+普通ADC(這顆料據(jù)說是業(yè)界最小,400×400相素,封裝尺寸只有550μm*550μm)、DH01A10。

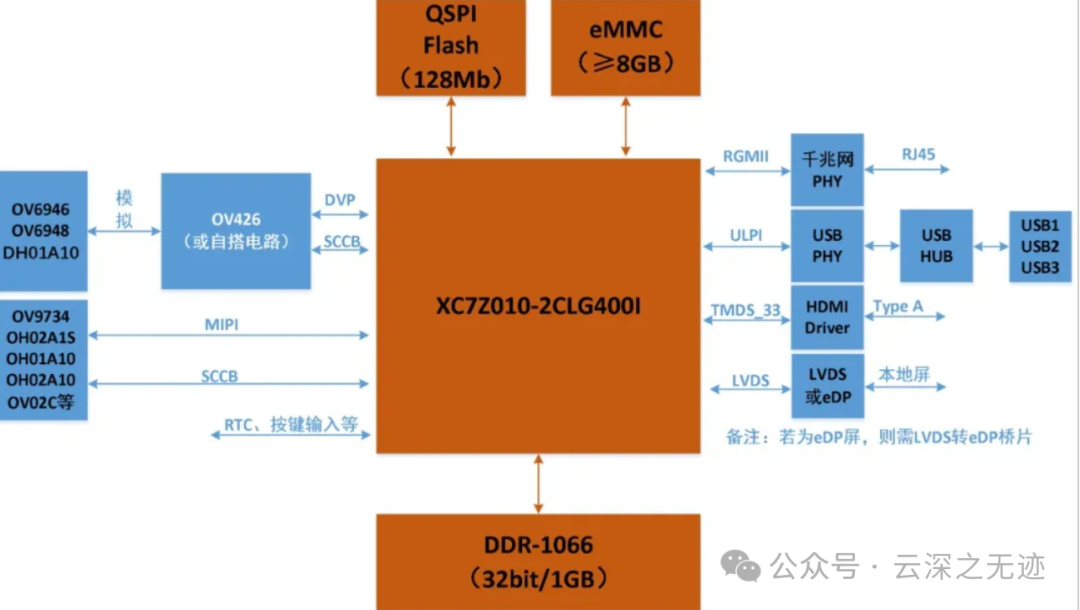

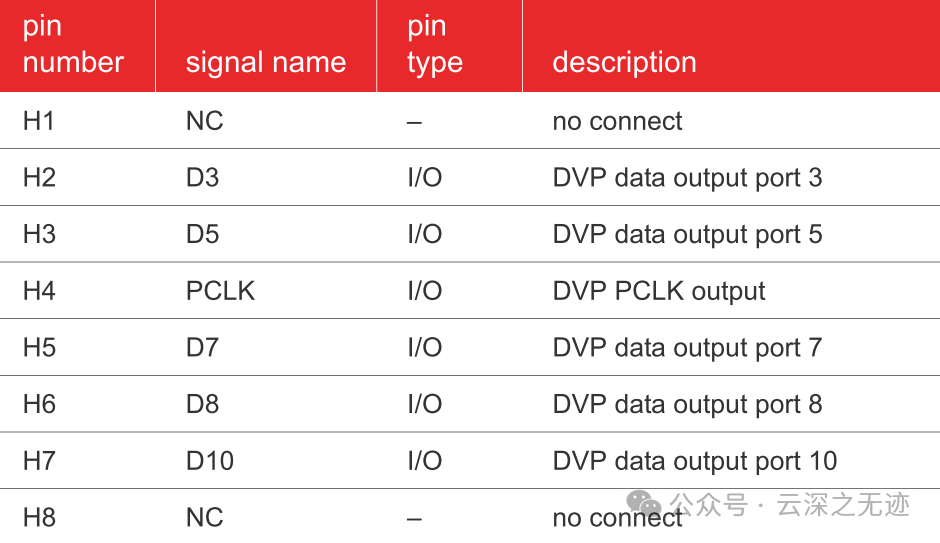

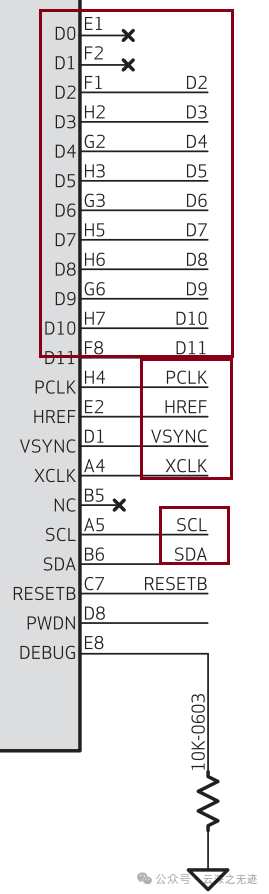

來自ZYNQ的一張圖,這里就看DVP和SCCB的接口

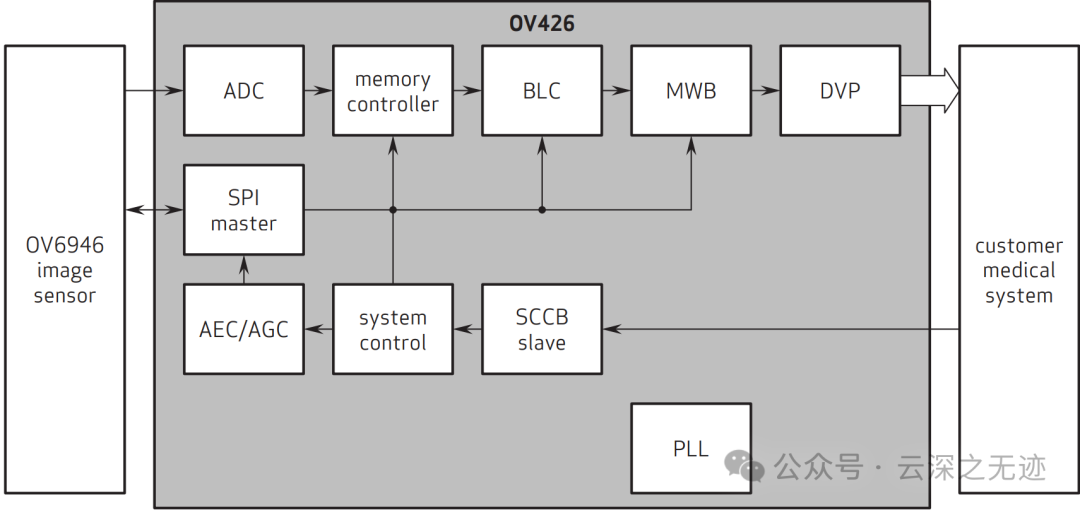

接口是4個,ADC+SPI是相機側(cè)的,IIC+DVP并口是輸出側(cè)的

穩(wěn)妥

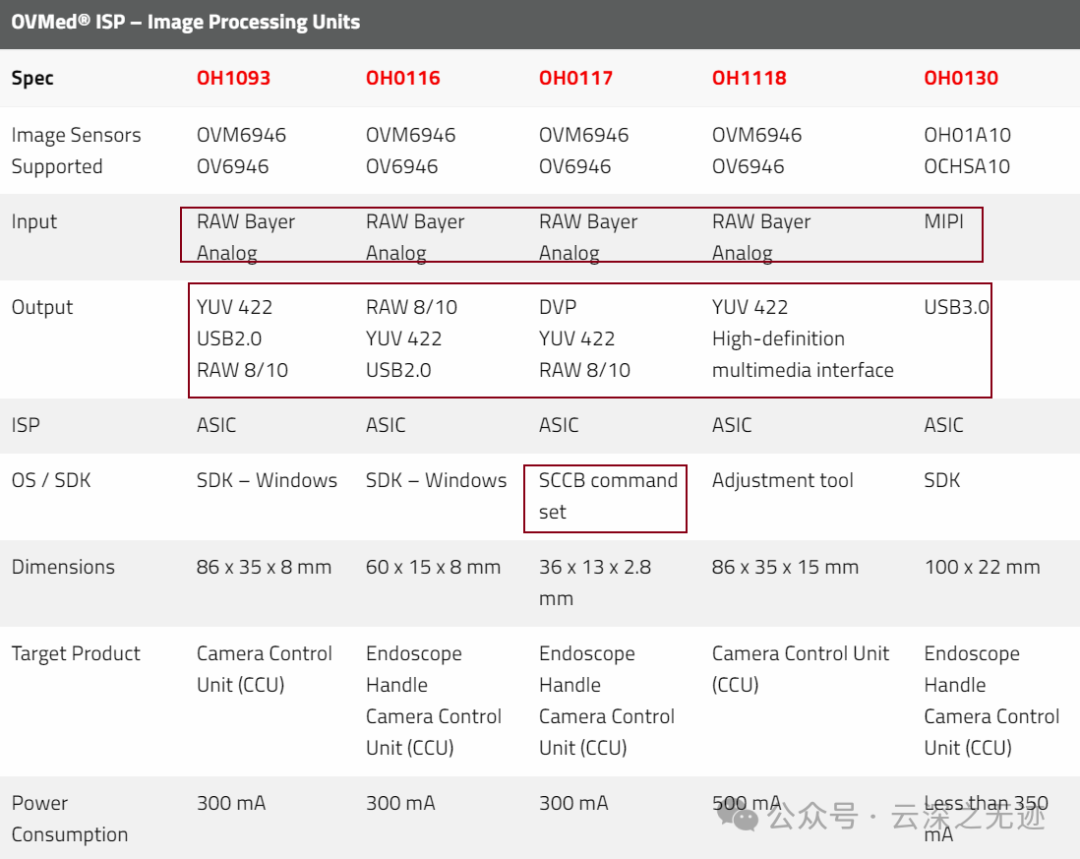

另外OV其實也是給了一系列的現(xiàn)成的解決方案:

五款

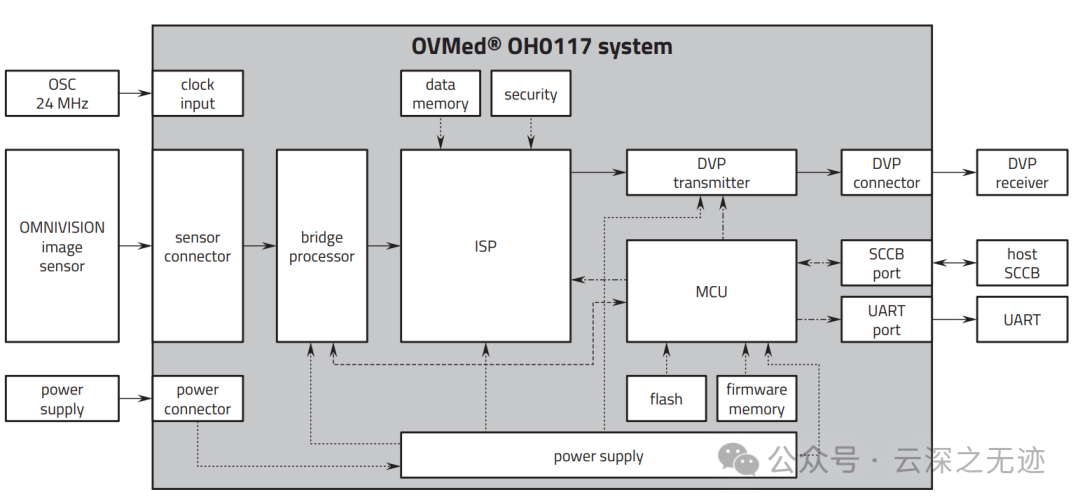

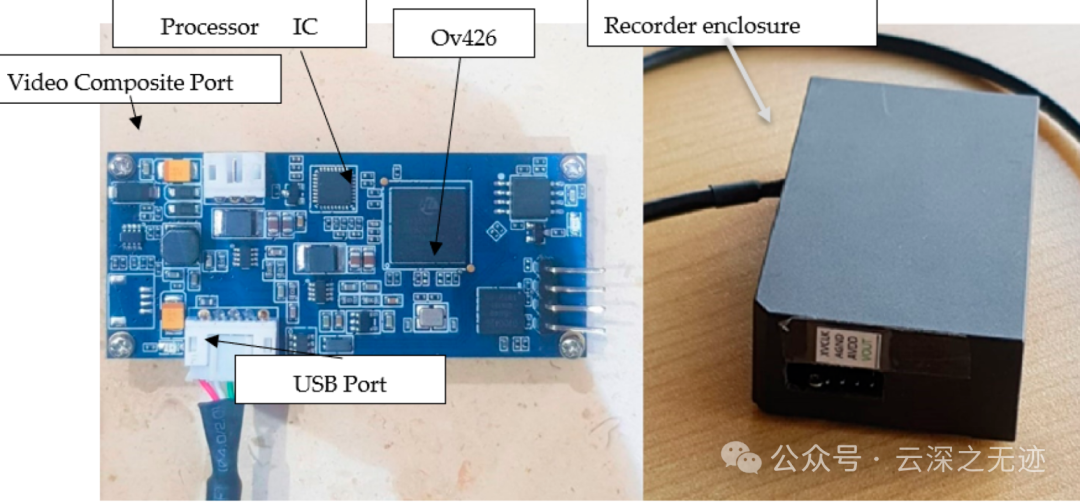

這個是處理完又是DVP輸出去了,命令可以使用串口來控制

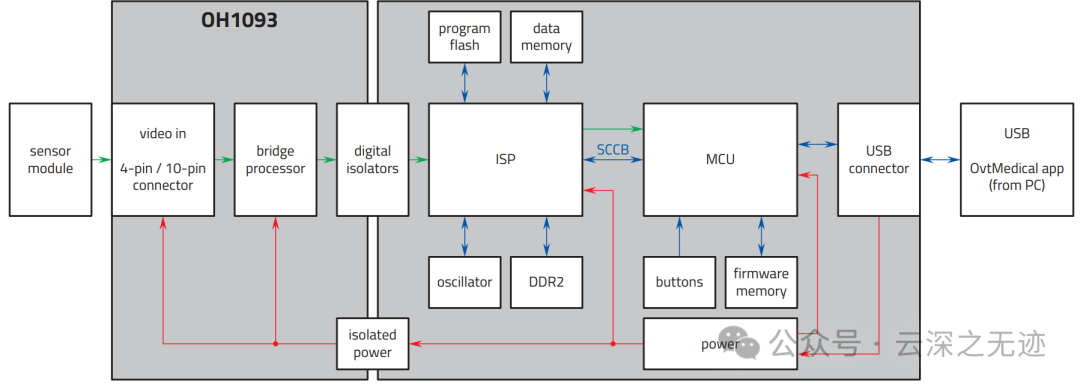

這個一看就很重型,直接USB輸出

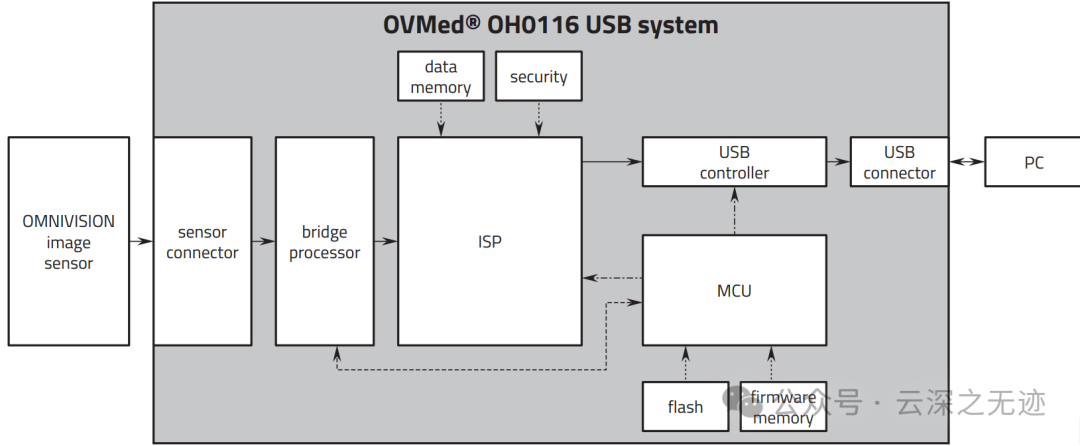

這個是追求實時性,沒有過多的緩存

這個是注重外設(shè)控制

有時候是好幾個攝像頭儀器拍攝,各個系統(tǒng)之間進行同步曝光:

同步曝光:關(guān)于 FSIN 引腳用于同步曝光的功能,可以通過外部信號來同步多個攝像頭的曝光時間,確保它們捕獲圖像的時刻是一致的。要實現(xiàn)這一點需要在設(shè)計中額外添加對 FSIN 信號的支持,以確保能夠正確地控制和同步曝光。 內(nèi)部時鐘:由于每個圖像傳感器的時鐘是自由運行的,同步曝光僅同步它們的曝光起點,而不會同步內(nèi)部時鐘或其他電路。這意味著即使曝光是同步的,傳感器間的像素數(shù)據(jù)輸出可能仍存在微小的時差,這通常可以通過后續(xù)的軟件處理來校正。

以上系統(tǒng)延遲范圍為100ms到160ms,我不知道真的假的。

說回OV426,DVP是需要很多的引腳,DVP接口使用的是LVDS(Low Voltage Differential Signaling)電氣接口標準,通常需要使用更多的電源和地線來支持高速數(shù)據(jù)傳輸。這使得dvp接口的設(shè)計更為復(fù)雜,并且需要更多的空間來布線。

DVP接口一個PCLK周期可以傳輸1byte數(shù)據(jù),1byte各位并行輸出,一行Pixel輸出完后,Sensor輸出一個HSYNC行同步信號,一幀所有行輸出完成后,輸出一個VSYNC幀同步型號。

PCLK、D0、D1都是高頻信號線(低位變化更加頻繁),Layout時注意屏蔽干擾、不可與其它高頻線并排或重疊走線,最好用GND線或者低頻線(如D7、D6)隔開。

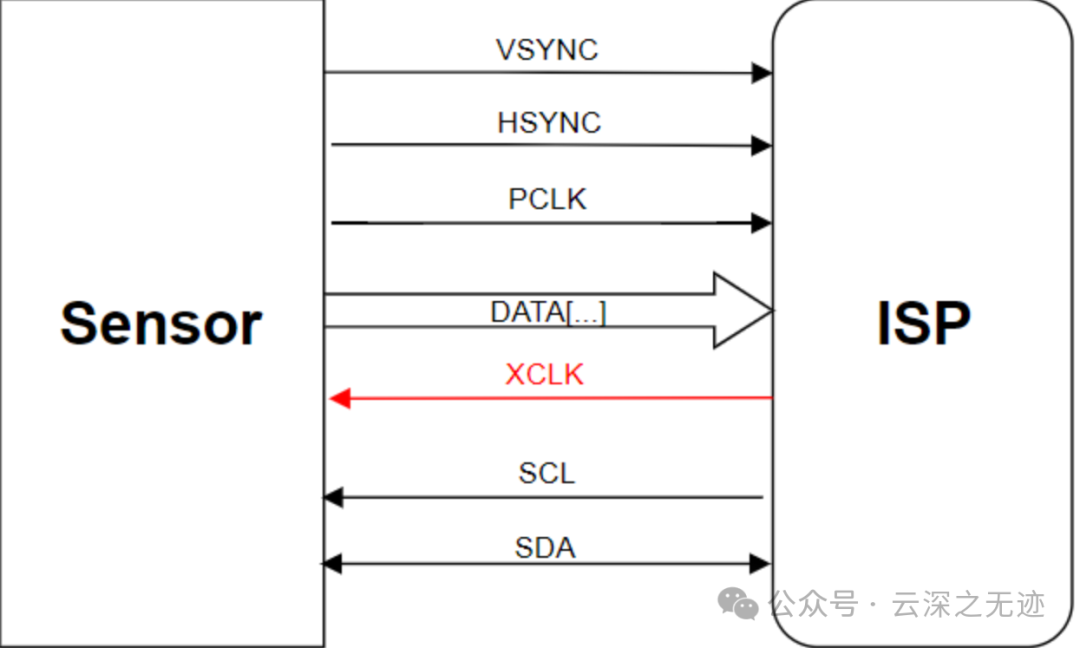

這圖最經(jīng)典了

VSYNC:vertical synchronization,幀同步信號, 一幀一個信號,頻率為幾十Hz

HSYNC:horizonal synchronization,行同步信號,一般為幾十KHz

PCLK:pixel clock ,像素時鐘,每個時鐘對應(yīng)一個像素數(shù)據(jù)

DATA: 像素數(shù)據(jù),視頻數(shù)據(jù),常見的有8位和10位

XCLK:也叫 MCLK,ISP芯片輸出給驅(qū)動 sensor 的時鐘,可由 ISP 主控或晶振提供,

一般是24MHz/27MHz

SCL: IIC 時鐘引腳,用來讀寫sensor的寄存器

SDA:IIC 數(shù)據(jù)引腳,用來讀寫 sensor 的寄存器

這里引腳放一部分

信號線雖然是說沒有mipi那么嚴格

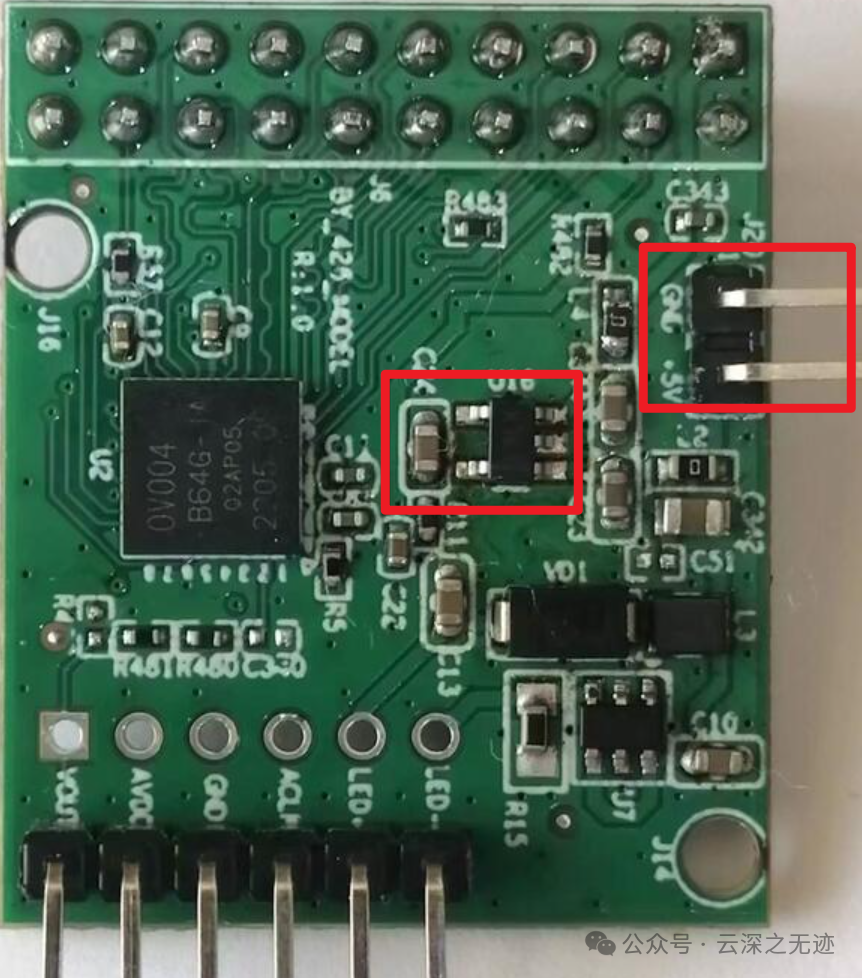

但是也是要保證等長,看電源

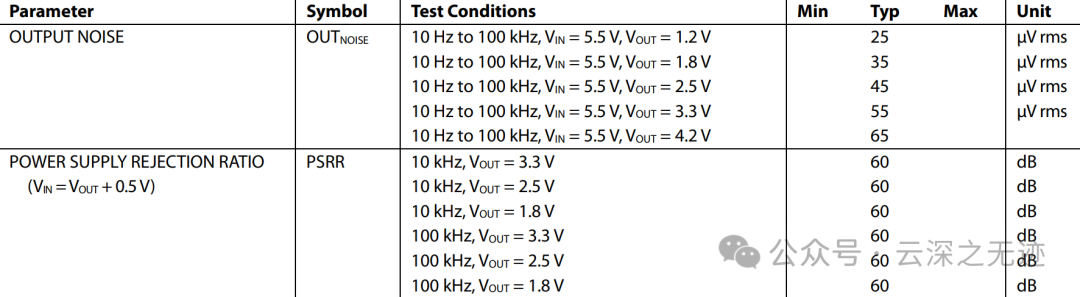

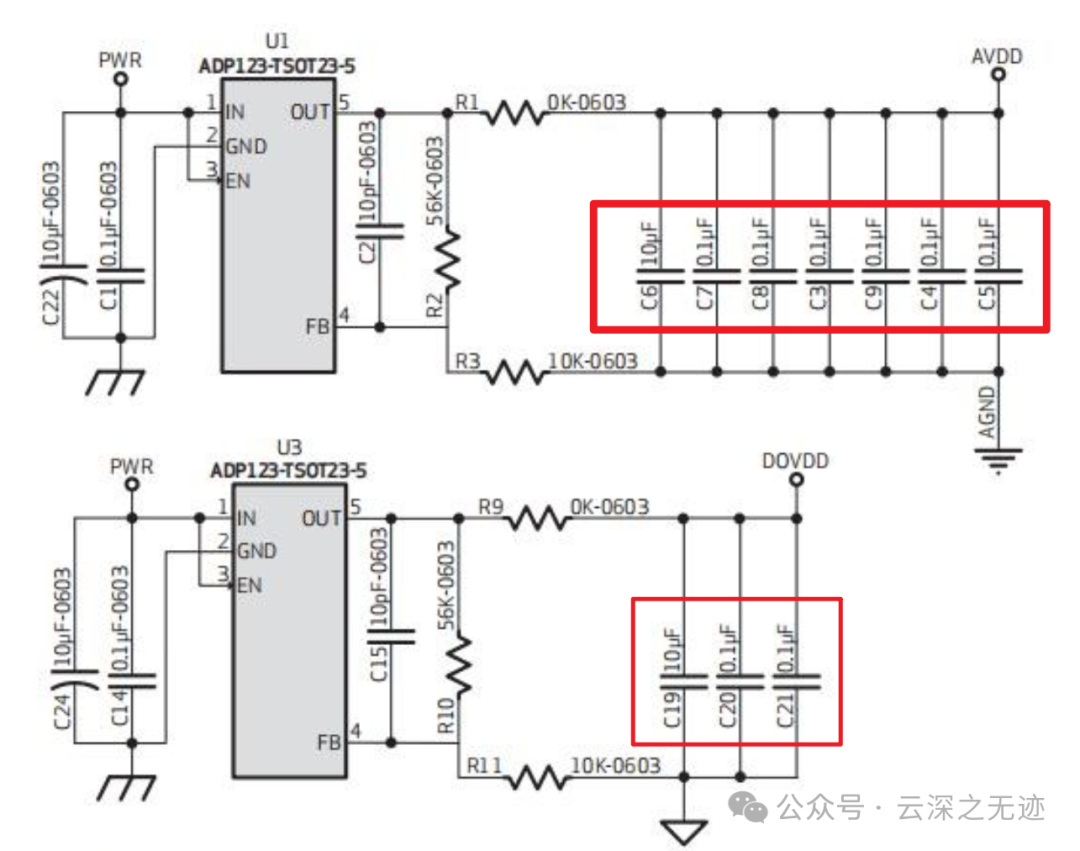

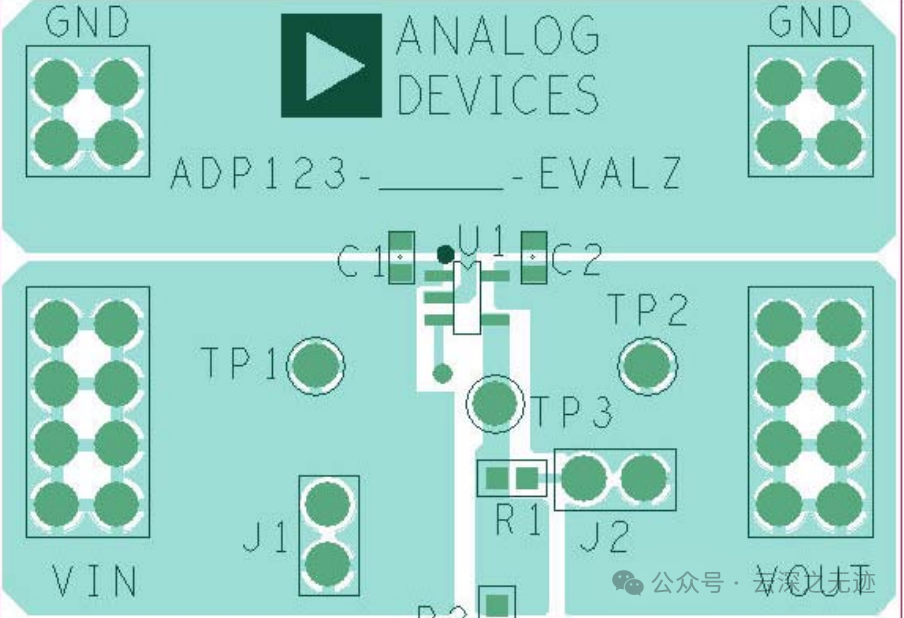

電源推薦ADP123,狠狠的加電容

模擬的比數(shù)字的電容更多

layout

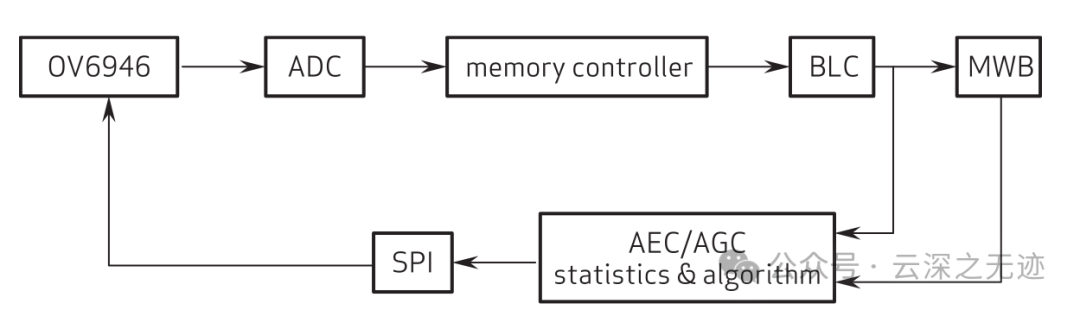

這個是內(nèi)部的工作

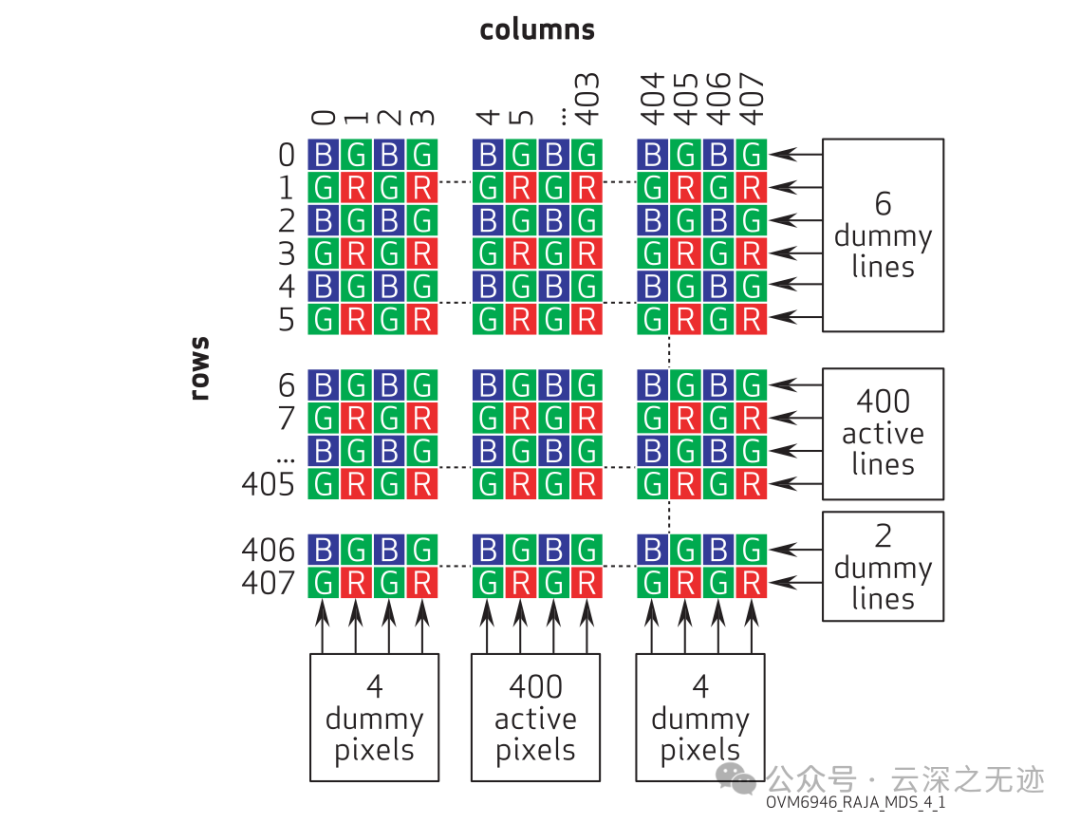

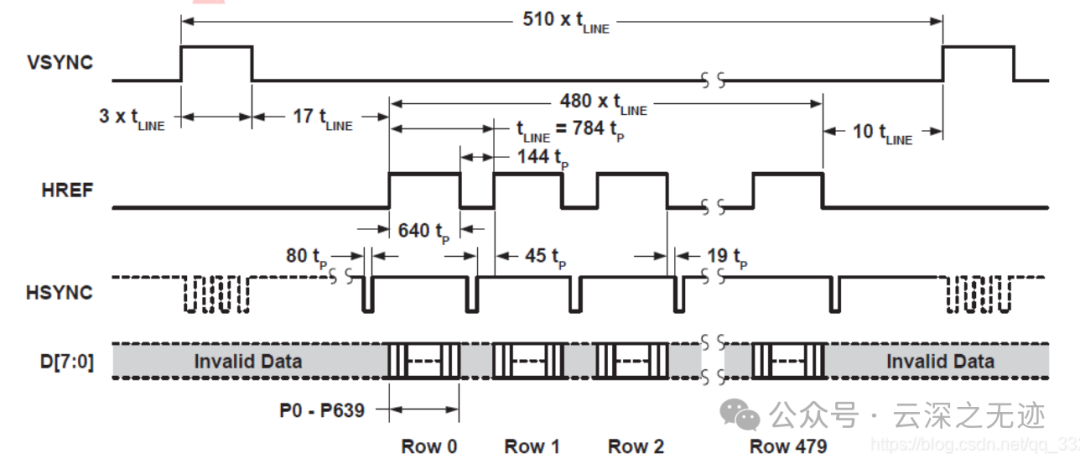

輸出圖像時,一幀幀地輸出,在幀內(nèi)的數(shù)據(jù)一般從左到右,從上到下, 一個像素一個像素地輸出。

數(shù)據(jù)線會在1個像素同步時鐘PCLK的驅(qū)動下發(fā)送1字節(jié)的數(shù)據(jù)信號,所以2個PCLK時鐘可發(fā)送1個RGB565格式(我沒有找到具體是什么)的像素數(shù)據(jù)。像素數(shù)據(jù)依次傳輸,每傳輸完一行數(shù)據(jù)時,行同步信號HREF會輸出一個電平跳變信號,每傳輸完一幀圖像時,VSYNC會輸出一個電平跳變信號。

可以看這個

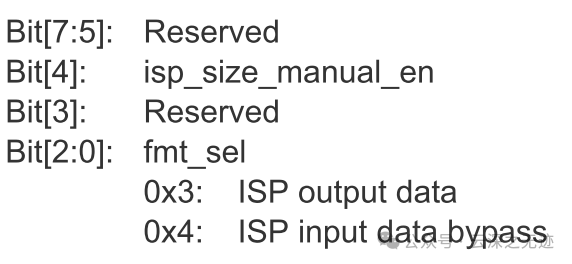

OV426的ISP很弱,所以需要外部ISP來補齊。

AEC 功能通過自動調(diào)整圖像傳感器的曝光時間來控制進入傳感器的光量,確保圖像既不過曝也不欠曝。

AGC 功能通過調(diào)整圖像傳感器的增益來控制圖像的亮度。增益可以被視為圖像信號的放大系數(shù)。

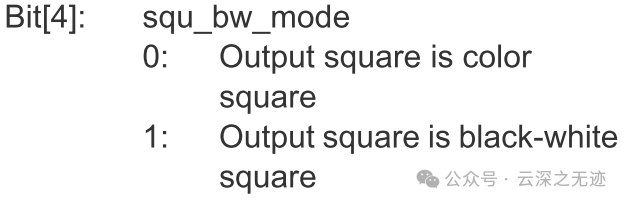

這個是一個有趣的寄存器,顏色

這個也是,可以輸出拜耳圖像,直接就不處理了

DVP的協(xié)議吧,一般都認為是和VGA的協(xié)議差不多:只是VSYNC信號高低電平相反了。DVP協(xié)議的HREF信號是在HERF為高電平是直接輸出像素數(shù)據(jù),而VGA接口的HSYNC信號在HSYNC為高時先后輸出顯示后沿、有效圖像數(shù)據(jù)、顯示前沿。

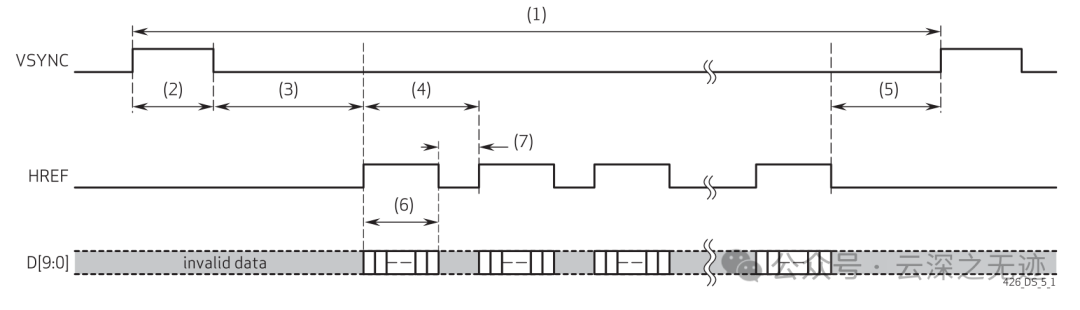

這里給出一個時序圖分析

這個是OV7670的

數(shù)字的區(qū)域是時間,t=1/8Mhz

VSYNC(垂直同步): 指示一幀圖像的開始和結(jié)束。在圖中,一個 VSYNC 脈沖代表一幀圖像的時間跨度。 HREF(水平參考): 用于標示一行像素的開始和結(jié)束。

在一幀圖像內(nèi)部,每當 HREF 信號為高電平時,對應(yīng)的行像素數(shù)據(jù)被視為有效。 D[9:0](數(shù)據(jù)線): 傳輸圖像數(shù)據(jù)的線。數(shù)據(jù)通常是在 HREF 高電平期間有效,并且在 VSYNC 低電平期間不斷傳輸以構(gòu)成一幀圖像。

時序圖中的各個部分代表:

(1): 整幀的周期,從一個 VSYNC 的下降沿到下一個下降沿。(看著是上升沿)

(2): VSYNC 信號內(nèi)部,代表幀開始前的時間間隔,通常稱為垂直前沿。

(3): 有效的幀傳輸時間,這時候 HREF 和 D[9:0] 會傳輸有效的圖像數(shù)據(jù)。

(4): 垂直后沿,幀結(jié)束后到下一個幀開始前的時間間隔。

(5): 垂直同步信號持續(xù)的時間。

(6): HREF 信號內(nèi)部,代表一行像素開始前的時間間隔,通常稱為水平前沿。

(7): 有效的行傳輸時間,在此期間,D[9:0] 上會傳輸有效的像素數(shù)據(jù)。 圖中的 "invalid data" 注釋指出在 VSYNC 信號為高時,HREF 可能仍為高電平,但此時的數(shù)據(jù)不應(yīng)被視為有效圖像內(nèi)容。

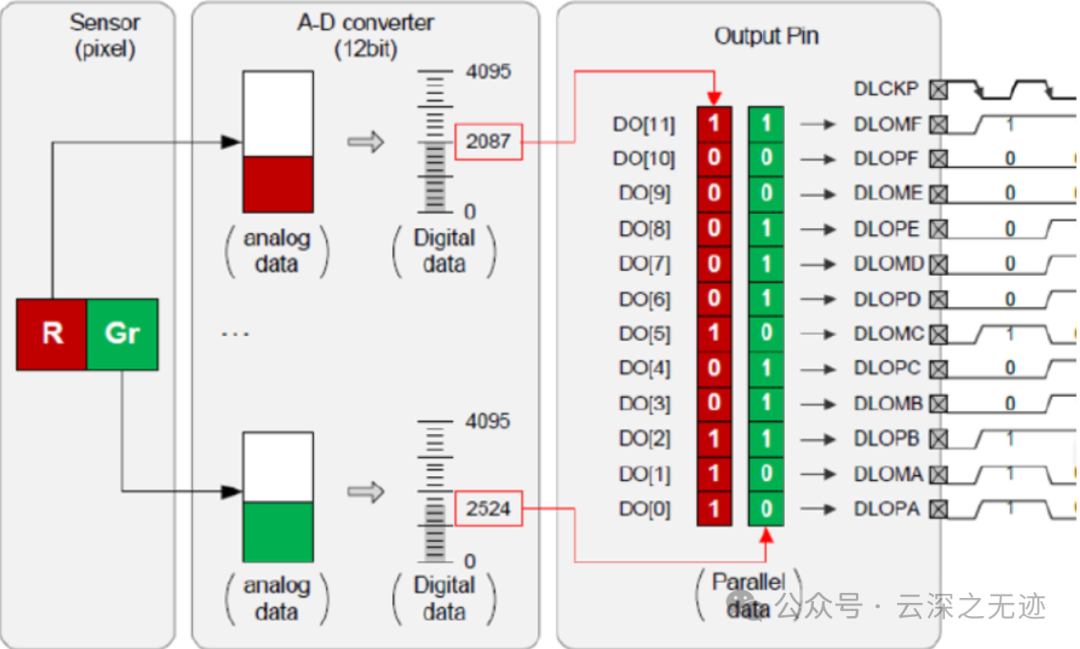

至于這個并口輸出,這個好像是最形象的一個

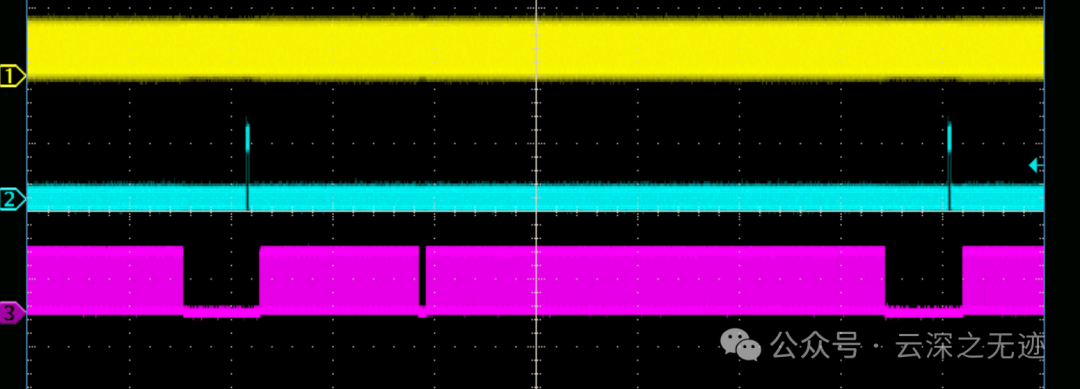

抓取的實測的 DVP 波形,黃色是輸入時鐘 ,藍色是幀同步信號 ,紅色是 PCLK(像素時鐘)

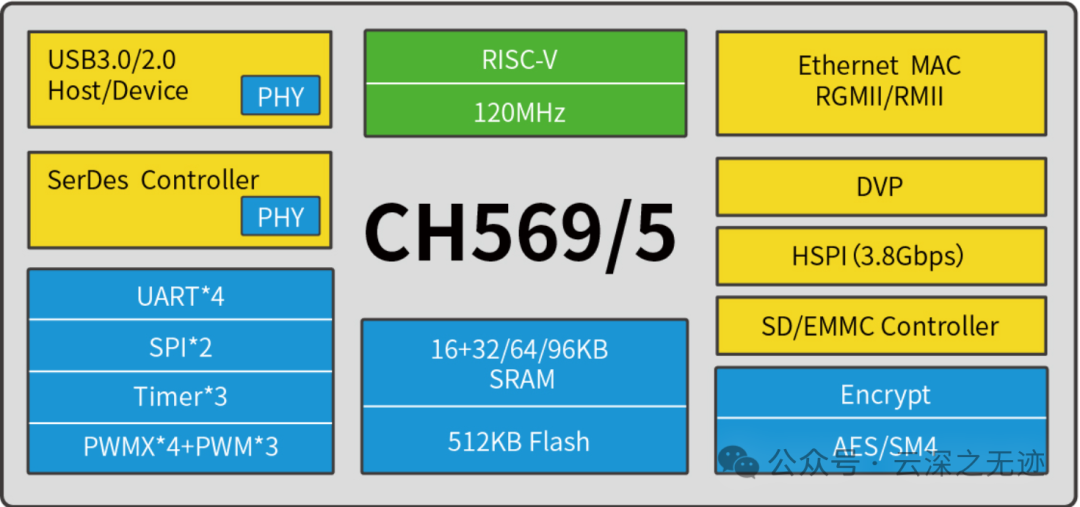

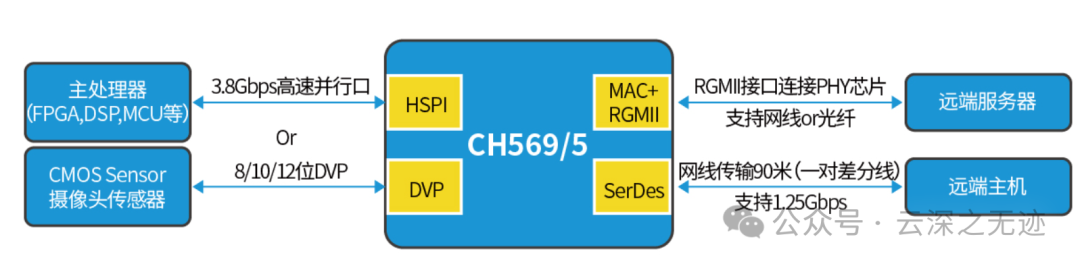

另外,我找到了一個芯片,這個可以直接當成USB輸出,可以探索一下

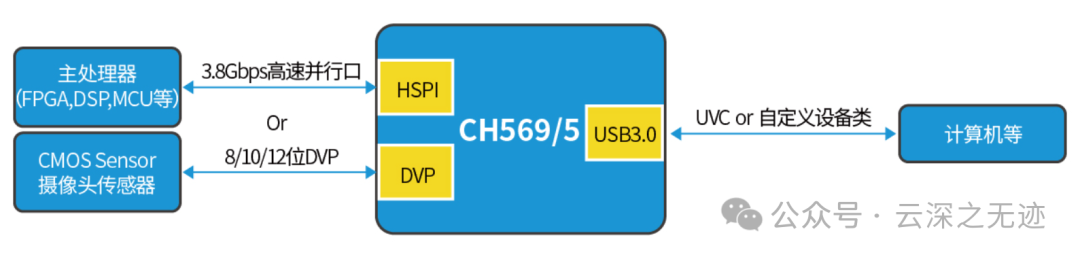

一個拓撲圖

也可以遠程傳輸

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19349瀏覽量

230327 -

圖像傳感器

+關(guān)注

關(guān)注

68文章

1907瀏覽量

129604 -

lvds

+關(guān)注

關(guān)注

2文章

1043瀏覽量

65870 -

信號處理器

+關(guān)注

關(guān)注

1文章

254瀏覽量

25304 -

串口控制

+關(guān)注

關(guān)注

0文章

27瀏覽量

9877

原文標題:OV426硬件設(shè)計-CCU(相機控制單元)

文章出處:【微信號:TT1827652464,微信公眾號:云深之無跡】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

汽車電子控制單元ECU的設(shè)計

基于IXP425和DM642的會議電視多點控制單元硬件設(shè)計原理和實現(xiàn)方法介紹

FPGA在賽車引擎控制單元有什么用處?

ABS ECU控制單元是什么意思

TCN線路冗余控制單元的研究

上位控制單元在運動控制系統(tǒng)中的應(yīng)用

HCU控制單元硬件手冊

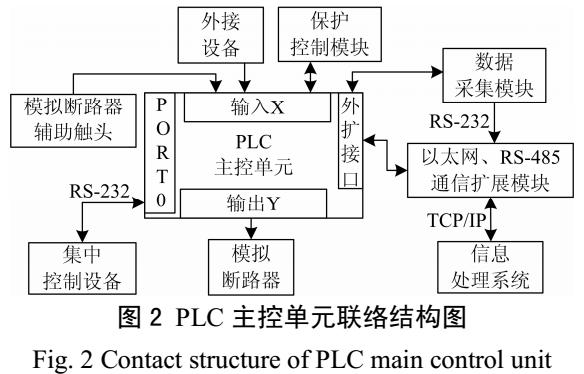

配網(wǎng)物理模擬系統(tǒng)控制單元設(shè)計

OV426硬件設(shè)計方案-CCU(相機控制單元)

OV426硬件設(shè)計方案-CCU(相機控制單元)

評論