根據(jù)圖像傳感器的應用和制造工藝,圖像傳感器可分為CCD圖像傳感器和CMOS圖像傳感器。 特別是CMOS圖像傳感器(CIS)不僅被搭載于數(shù)碼相機,還被廣泛應用于智能手機、平板電腦、CCTV、汽車黑匣子、無人駕駛車輛傳感器、虛擬現(xiàn)實(VR)、醫(yī)療設備、無人機等各種新興市場領域。

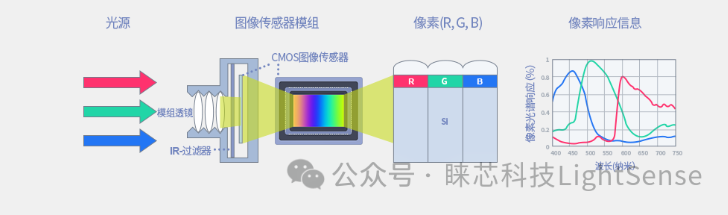

基于CMOS的圖像傳感器的工作過程如下: 當可見光波長范圍(400-700納米)的光能聚集在硅襯底的光電二極管(PD)時,硅表面接收光能形成電子-空穴對(electron-hole pair)。 在此過程中產(chǎn)生的電子通過浮動擴散(FD)轉換成電壓,然后再通過模擬到數(shù)字轉換器(ADC)轉換為數(shù)字數(shù)據(jù)。 為了制造出使這一系列流程成為可能的CIS產(chǎn)品,需要采用CIS特有的、有別于半導體存儲器的關鍵制造工藝技術。此類工藝技術可分為以下五大類:

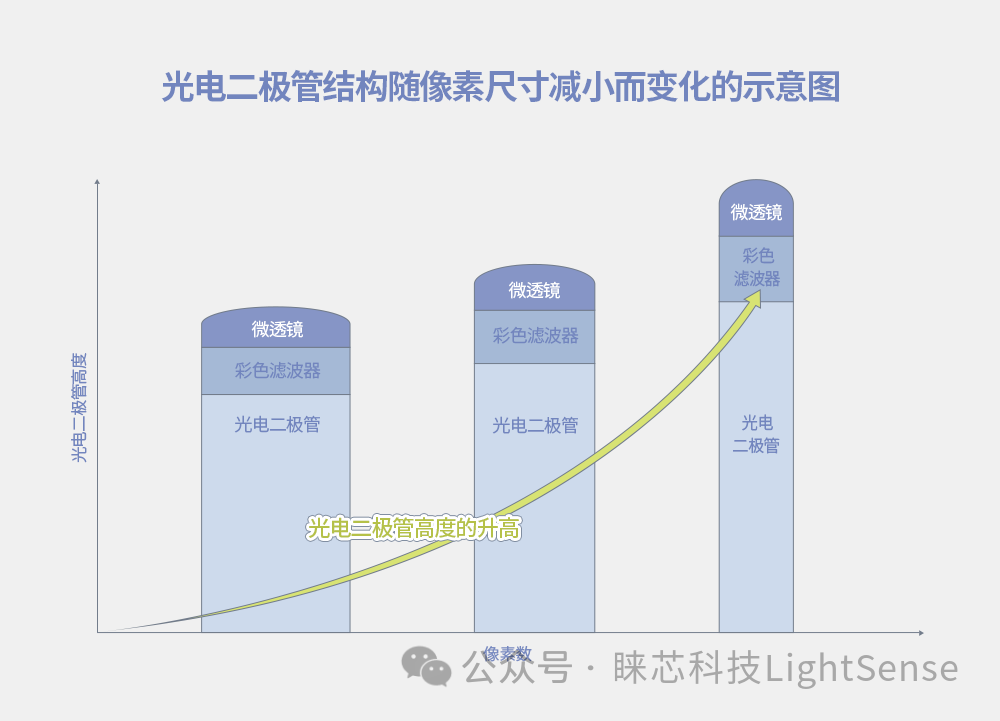

1.深層光電二極管成型工藝技術

在相同的芯片尺寸上要增加像素數(shù)量,就需要不可避免地縮小單一像素的尺寸。深層光電二極管的形成是防止圖像質量下降的關鍵技術。為了在更小的像素中確保足夠的滿阱容量(full well capacity, FWC),與半導體存儲器相比,CIS需要采用難度更高的圖像形成技術。尤其需要確保高縱橫比(>15:1)植入掩碼(implant MASK)工藝技術,以阻止高能量離子的植入;事實上,目前縱橫比在業(yè)內有逐步提高的趨勢。

2.像素間隔離處理技術

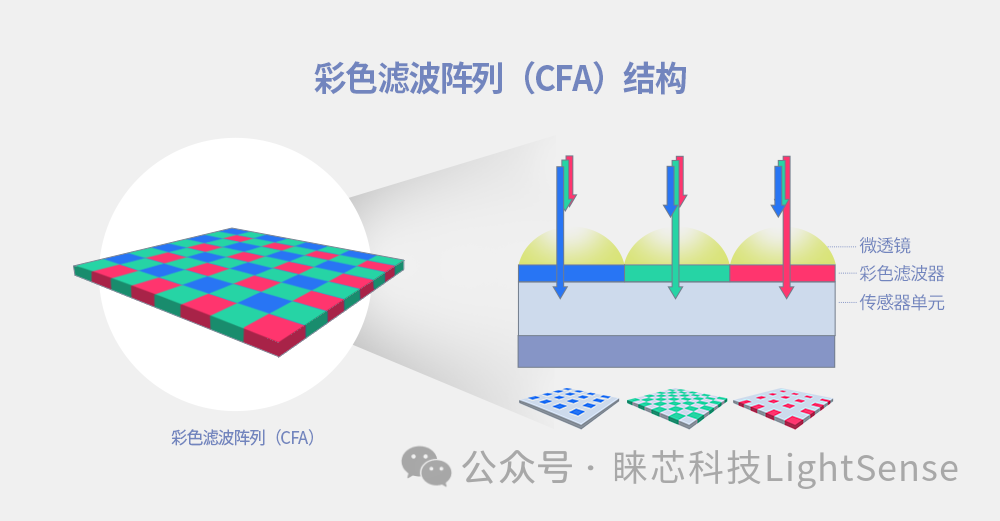

3.彩色濾波陣列(CFA)處理技術

彩色濾波陣列是有別于半導體存儲器制造工藝的CIS獨有的工藝 。CFA工藝一般由彩色濾波器(CF)和微透鏡(ML)組成,前者可將入射光過濾成紅、綠、藍各波長范圍,后者可提高光凝聚效率。為了獲得優(yōu)良的圖像品質,開發(fā)和評估R/G/B彩色素材并開發(fā)相關技術以優(yōu)化形狀、厚度等工藝條件非常重要。

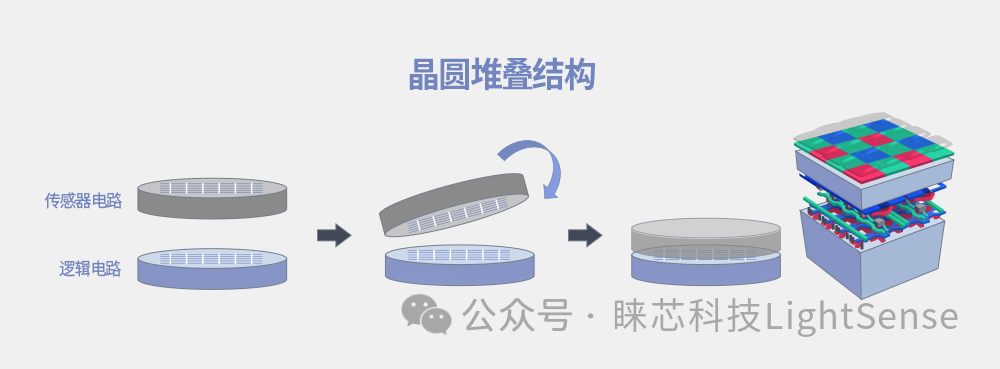

4.晶圓堆疊工藝

晶圓堆疊是指將兩個晶圓連接在一起。這是制作高像素、高清晰度的CIS產(chǎn)品的必備技術。對于高像素CIS產(chǎn)品,像素陣列和邏輯電路分別在個別晶圓上形成。這些晶圓在工藝期間被連接在一起,而這一過程被稱為“晶圓粘結(wafer bonding)”。像素陣列和邏輯電路的分離意味著制造成本的增加,但同時也意味著可以在同等晶圓面積上生產(chǎn)更多芯片;不僅如此,這還有助于提高產(chǎn)品的性能。因此,這是目前大多數(shù)CIS芯片廠商所采用的技術。晶圓堆疊技術正以各種形式不斷發(fā)展。近年來,晶圓堆疊技術也被應用于半導體存儲器領域,促進了產(chǎn)品性能的提升。

5.有助于提高CIS良品率和產(chǎn)品質量的控制技術

控制金屬污染是CIS產(chǎn)品開發(fā)和量產(chǎn)過程中最基本的前提條件之一。由于CIS產(chǎn)品對污染的敏感度是存儲器產(chǎn)品的數(shù)倍,且污染會直接影響CIS產(chǎn)品的良品率和質量,因此CIS的生產(chǎn)必須采用各種污染控制技術。另一個重要因素是等離子體損傷控制。由于圖像屬性的損壞(如熱像素)是在工藝過程中造成的損傷而發(fā)生的,因此有必要對關鍵工藝進行精確管理。

來源:睞芯科技LightSense

審核編輯:湯梓紅

-

CMOS

+關注

關注

58文章

5723瀏覽量

235639 -

半導體

+關注

關注

334文章

27442瀏覽量

219427 -

圖像傳感器

+關注

關注

68文章

1904瀏覽量

129581 -

CIS

+關注

關注

3文章

194瀏覽量

29633

原文標題:【光電集成】半導體領域的光學應用: CIS關鍵工藝技術概覽

文章出處:【微信號:今日光電,微信公眾號:今日光電】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

CMOS圖像傳感器電路設計

CMOS圖像傳感器的制造工藝

CMOS圖像傳感器的制造工藝

評論