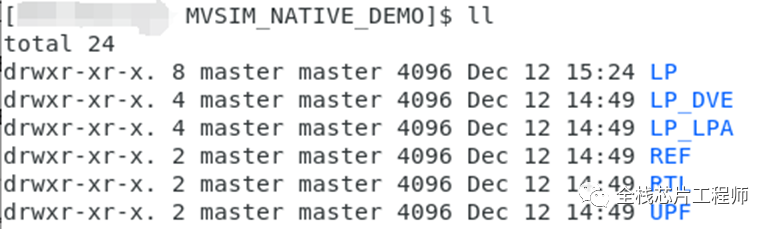

將MVSIM_NATIVE_DEMO文件夾拷貝出來,如下所示,LP、LP_DVE、LP_LPA文件夾分別存放的是仿真環境,REF文件夾是不帶UPF的參考對比仿真環境,RTL和UPF文件夾分別用來存放設計代碼和UPF文件。

直接上干貨,低功耗的關閉、打開仿真流程如下:

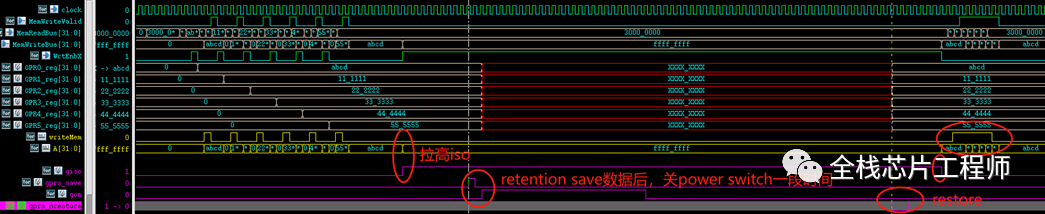

拉高isolation ->retention save ->關閉power switch ->打開power_switch->retention restore ->拉低isolation

仿真波形如下:

SoC訓練營學員問為何低功耗cell沒有插入網表?

雖然提問題是值得鼓勵的,但是我們在遇到問題時,還是先主動思考,主動解決問題,實在解決不了我們再求助,這樣成長更快。

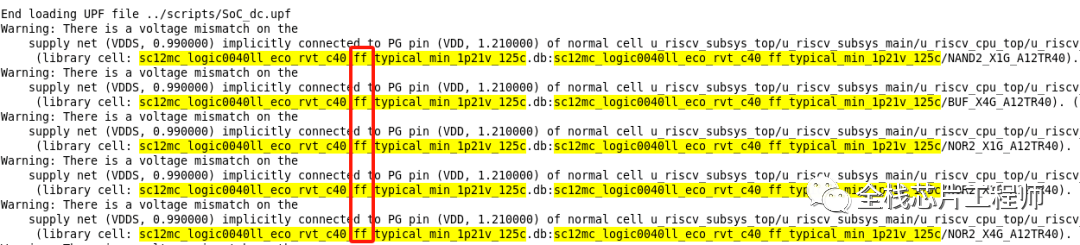

首先,小編拿到這問題,就打開log,查看log是一種IC設計美德!發現EDA工具吃進UPF文件后,報了warning如下,用到了很多ff庫。

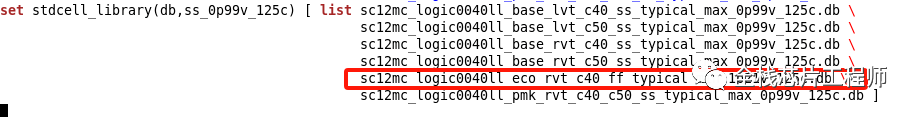

上圖報錯UPF指定電壓是0.99V,而CELL是1.20V,電壓不匹配,導致邏輯綜合出來的網表沒有插入MV CELL。注意,綜合時,我們用的ss庫,怎么會是ff庫呢?打開約束腳本發現如下bug:

于是,更改約束,將ff換成ss即可。再次run一下,結果就出來了:

低功耗設計部分,設計里面我會留一點小bug在里面 非常簡單,我不會公布答案,大家一定要多思考、多動手跑跑,這樣才學的深刻。

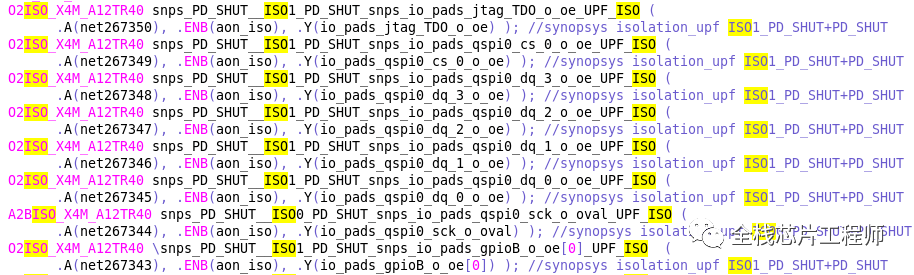

培訓學員請注意,景芯SoC用always on的power domain電壓域的pwrdown_mux信號作為power switch cell的switch控制信號,但是設計里面有個小問題,不太算bug的bug,但對upf低功耗flow而言,毫無疑問就是bug!

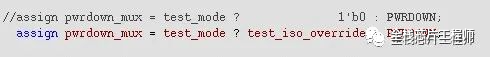

培訓學員請登陸服務器追蹤一下pwrdown信號,注意其負載情況,RTL代碼如下:

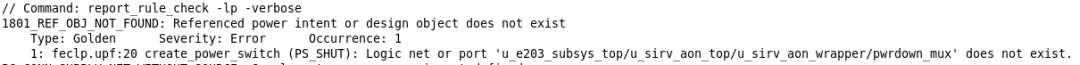

結合PR輸出的netlist, 我們做個clp低功耗檢查,腳本參見服務器。可以發現,clp報錯說power switch的switch控制信號找不到。

不得不說,clp檢查對低功耗而言多么重要,對芯片設計而言多重要!景芯SoC的價值就在把芯片設計全流程的這些細小的知識點,全部串接起來!猶豫啥?抓緊報名加入吧!

在芯片設計中端流程時,景芯SoC會插入UPF約束中的isolation等cell,但是無法插入power switch等cell,因此,作為power switch cell的控制信號pwrdown_mux在沒有負載的情況下,會被裁員掉(優化掉),因此需要設置上面MUX器件為dont_touch或者使pwrdown_mux成為module的port并禁止auto_ungroup(并設置no_boundary_optimization),這樣這個信號才能保留給后端,供后端實現power switch控制。

請學員完成代碼修改,基于全套flow環境完成如下任務:

lint檢查、前端仿真,

完成中端、后端flow,

完成clp檢查,完成后仿真

審核編輯:湯梓紅

-

soc

+關注

關注

38文章

4169瀏覽量

218330 -

仿真

+關注

關注

50文章

4087瀏覽量

133644 -

低功耗

+關注

關注

10文章

2406瀏覽量

103730 -

代碼

+關注

關注

30文章

4790瀏覽量

68649

原文標題:低功耗仿真實戰! 低功耗全流程培訓

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

低功耗仿真實戰

低功耗仿真實戰

評論