來源:造芯師

一、SOC芯片是什么?

SOC的定義多種多樣,由于其內(nèi)涵豐富、應(yīng)用范圍廣,很難給出準(zhǔn)確定義。一般說來,SOC系統(tǒng)級(jí)芯片,也有稱片上系統(tǒng),意指它是一個(gè)產(chǎn)品,是一個(gè)有專用目標(biāo)的集成電路,其中包含完整系統(tǒng)并有嵌入軟件的全部?jī)?nèi)容。同時(shí)它又是一種技術(shù),用以實(shí)現(xiàn)從確定系統(tǒng)功能開始,到軟/硬件劃分,并完成設(shè)計(jì)的整個(gè)過程。

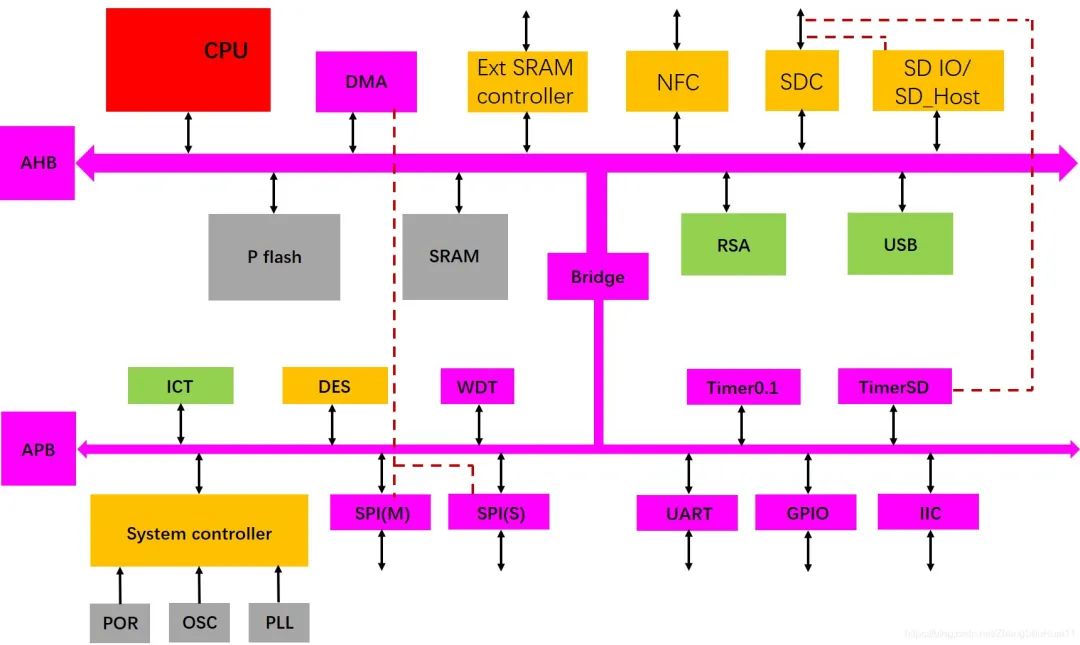

從狹義角度講,它是信息系統(tǒng)核心的芯片集成,是將系統(tǒng)關(guān)鍵部件集成在一塊芯片上;從廣義角度講,SOC是一個(gè)微小型系統(tǒng),如果說中央處理器(CPU)是大腦,那么SoC就是包括大腦、心臟、眼睛和手的系統(tǒng)。國(guó)內(nèi)外學(xué)術(shù)界一般傾向?qū)OC定義為將微處理器、模擬IP(Intellectual Property)核、數(shù)字IP核和存儲(chǔ)器(或片外存儲(chǔ)控制接口)集成在單一芯片上,它通常是客戶定制的,或是面向特定用途的標(biāo)準(zhǔn)產(chǎn)品。1、SOC的芯片的構(gòu)成是系統(tǒng)級(jí)芯片控制邏輯模塊、微處理器/微控制器CPU 內(nèi)核模塊、數(shù)字信號(hào)處理器DSP模塊、嵌入的存儲(chǔ)器模塊、和外部進(jìn)行通訊的接口模塊、含有ADC /DAC 的模擬前端模塊、電源提供和功耗管理模塊,對(duì)于一個(gè)無線SOC還有射頻前端模塊、用戶定義邏輯(它可以由FPGA 或ASIC實(shí)現(xiàn))以及微電子機(jī)械模塊,更重要的是一個(gè)SOC芯片內(nèi)嵌有基本軟件(RDOS或COS以及其他應(yīng)用軟件)模塊或可載入的用戶軟件等。

2、SOC的形成過程

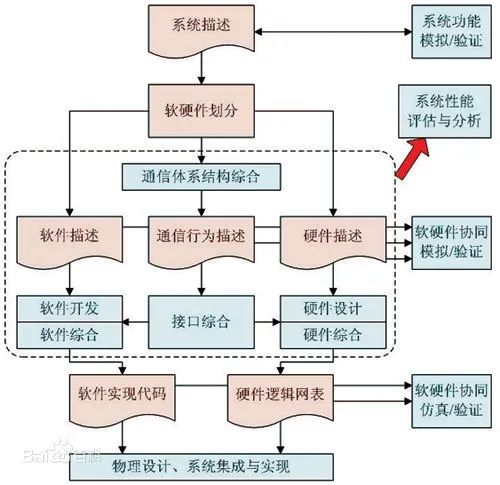

(1)基于單片集成系統(tǒng)的軟硬件協(xié)同設(shè)計(jì)和驗(yàn)證;

(2)再利用邏輯面積技術(shù)使用和產(chǎn)能占有比例有效提高即開發(fā)和研究IP核生成及復(fù)用技術(shù),特別是大容量的存儲(chǔ)模塊嵌入的重復(fù)應(yīng)用等;IP核復(fù)用技術(shù)在SOC芯片設(shè)計(jì)中被廣泛采用。先進(jìn)工藝條件下,SoC系統(tǒng)級(jí)芯片設(shè)計(jì)規(guī)模越來越大,芯片上所集成的IP種類和數(shù)量也隨之暴增。IP數(shù)據(jù)如何高效管理和追蹤變得尤為重要。

(3) 超深亞微米(VDSM) 、納米集成電路的設(shè)計(jì)理論和技術(shù)。

3、SOC設(shè)計(jì)的關(guān)鍵技術(shù)SOC關(guān)鍵技術(shù)主要包括總線架構(gòu)技術(shù)、IP核可復(fù)用技術(shù)、軟硬件協(xié)同設(shè)計(jì)技術(shù)、SOC驗(yàn)證技術(shù)、可測(cè)性設(shè)計(jì)技術(shù)、低功耗設(shè)計(jì)技術(shù)、超深亞微米電路實(shí)現(xiàn)技術(shù),并且包含做嵌入式軟件移植、開發(fā)研究,是一門跨學(xué)科的新興研究領(lǐng)域。

二、SOC芯片的優(yōu)缺點(diǎn)

優(yōu)點(diǎn)

- 芯片尺寸小。受益于MOS技術(shù),SOC片可實(shí)現(xiàn)功能增加的同時(shí),芯片尺寸大大減小。

- 低功耗。SOC的低功耗性能,可提高電子設(shè)備 (如手機(jī))的整體使用時(shí)間

- 可再編程。開發(fā)人員可對(duì)SOC芯片再編程,重復(fù)使用IP。

- 可靠性強(qiáng)。SOC芯片提高電路安全性并降低設(shè)計(jì)復(fù)雜性;

- 成本效益高。SOC相比其他電子器件,具有更少的物理組件和可再次設(shè)計(jì);

更快的運(yùn)行速度;

缺點(diǎn)

- 生產(chǎn)周期長(zhǎng)。SOC芯片從設(shè)計(jì)到制造出貨整個(gè)過程在6個(gè)月到1年左右;

- 設(shè)計(jì)驗(yàn)證時(shí)間長(zhǎng)。SOC芯片的設(shè)計(jì)驗(yàn)證環(huán)節(jié)約占總周期的70%;

- IP核的授權(quán)和兼容情況大大影響產(chǎn)品上市時(shí)間;

- 制造成本指數(shù)型增長(zhǎng);

對(duì)于小批量的產(chǎn)品,SOC不是最好的選擇;

三、SOC芯片設(shè)計(jì)流程

1.功能設(shè)計(jì)階段

設(shè)計(jì)人員產(chǎn)品的應(yīng)用場(chǎng)合,設(shè)定一些諸如功能、操作速度、接口規(guī)格、環(huán)境溫度及消耗功率等規(guī)格,以做為將來電路設(shè)計(jì)時(shí)的依據(jù)。更可進(jìn)一步規(guī)劃軟件模塊及硬件模塊該如何劃分,哪些功能該整合于SOC 內(nèi),哪些功能可以設(shè)計(jì)在電路板上。

2.設(shè)計(jì)描述和行為級(jí)驗(yàn)證功能設(shè)計(jì)完成后,可以依據(jù)功能將SOC 劃分為若干功能模塊,并決定實(shí)現(xiàn)這些功能將要使用的IP 核。此階段間接影響了SOC 內(nèi)部的架構(gòu)及各模塊間互動(dòng)的訊號(hào),及未來產(chǎn)品的可靠性。決定模塊之后,可以用VHDL 或Verilog 等硬件描述語言實(shí)現(xiàn)各模塊的設(shè)計(jì)。接著,利用VHDL 或Verilog 的電路仿真器,對(duì)設(shè)計(jì)進(jìn)行功能驗(yàn)證(functionsimulation,或行為驗(yàn)證 behavioral simulation)。注意,這種功能仿真沒有考慮電路實(shí)際的延遲,但無法獲得精確的結(jié)果。

3.邏輯綜合確定設(shè)計(jì)描述正確后,可以使用邏輯綜合工具(synthesizer)進(jìn)行綜合。綜合過程中,需要選擇適當(dāng)?shù)倪壿嬈骷?kù)(logic cell library),作為合成邏輯電路時(shí)的參考依據(jù)。硬件語言設(shè)計(jì)描述文件的編寫風(fēng)格是決定綜合工具執(zhí)行效率的一個(gè)重要因素。事實(shí)上,綜合工具支持的HDL 語法均是有限的,一些過于抽象的語法只適于做為系統(tǒng)評(píng)估時(shí)的仿真模型,而不能被綜合工具接受。邏輯綜合得到門級(jí)網(wǎng)表。

4.門級(jí)驗(yàn)證(Gate-Level Netlist Verification)門級(jí)功能驗(yàn)證是寄存器傳輸級(jí)驗(yàn)證。主要的工作是要確認(rèn)經(jīng)綜合后的電路是否符合功能需求,該工作一般利用門電路級(jí)驗(yàn)證工具完成。注意,此階段仿真需要考慮門電路的延遲。5.布局和布線布局指將設(shè)計(jì)好的功能模塊合理地安排在芯片上,規(guī)劃好它們的位置。布線則指完成各模塊之間互連的連線。注意,各模塊之間的連線通常比較長(zhǎng),因此,產(chǎn)生的延遲會(huì)嚴(yán)重影響SOC的性能,尤其在0.25 微米制程以上,這種現(xiàn)象更為顯著。

集成電路的發(fā)展已有40年的歷史,它一直遵循摩爾所指示的規(guī)律推進(jìn),現(xiàn)已進(jìn)入深亞微米階段。由于信息市場(chǎng)的需求和微電子自身的發(fā)展,引發(fā)了以微細(xì)加工(集成電路特征尺寸不斷縮小)為主要特征的多種工藝集成技術(shù)和面向應(yīng)用的系統(tǒng)級(jí)芯片的發(fā)展。隨著半導(dǎo)體產(chǎn)業(yè)進(jìn)入超深亞微米乃至納米加工時(shí)代,在單一集成電路芯片上就可以實(shí)現(xiàn)一個(gè)復(fù)雜的電子系統(tǒng),諸如手機(jī)芯片、數(shù)字電視芯片、DVD 芯片等。在未來幾年內(nèi),上億個(gè)晶體管、幾千萬個(gè)邏輯門都可望在單一芯片上實(shí)現(xiàn)。SOC(System - on - Chip)設(shè)計(jì)技術(shù)始于20世紀(jì)90年代中期,隨著半導(dǎo)體工藝技術(shù)的發(fā)展,IC設(shè)計(jì)者能夠?qū)⒂鷣碛鷱?fù)雜的功能集成到單硅片上,SOC正是在集成電路( IC)向集成系統(tǒng)( IS)轉(zhuǎn)變的大方向下產(chǎn)生的。1994年Motorola發(fā)布的FlexCore系統(tǒng)(用來制作基于68000和PowerPC的定制微處理器)和1995年LSILogic公司為Sony公司設(shè)計(jì)的SOC,可能是基于IP( IntellectualProperty)核完成SOC設(shè)計(jì)的最早報(bào)導(dǎo)。由于SOC可以充分利用已有的設(shè)計(jì)積累,顯著地提高了ASIC的設(shè)計(jì)能力,因此發(fā)展非常迅速,引起了工業(yè)界和學(xué)術(shù)界的關(guān)注。

SOC是集成電路發(fā)展的必然趨勢(shì),是技術(shù)發(fā)展的必然,也是IC 產(chǎn)業(yè)未來的發(fā)展。

-

處理器

+關(guān)注

關(guān)注

68文章

19343瀏覽量

230229 -

芯片

+關(guān)注

關(guān)注

456文章

50938瀏覽量

424687 -

soc

+關(guān)注

關(guān)注

38文章

4178瀏覽量

218480 -

軟件

+關(guān)注

關(guān)注

69文章

4968瀏覽量

87702

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文讀懂SOC芯片

一文讀懂SOC芯片

評(píng)論