1.電源處理

電源處理是射頻設計的第一道功課,電源處理不當,有源射頻電路將前功盡棄。同接收機一樣,浪涌、噪聲、DC-DC紋波、共模干擾都不可忽視,由于發射機是大信號,處理難度小于接收機。

2.輸出功率

功放管在整個頻率范圍內的額定輸出功率,考慮到最大輸出功率與功放管結溫緊密相關,應該有2dB以上的功率余量,如果是非恒包絡調制,會存在峰均比,功放的非線性還會惡化ACLR,所以實際的功放輸出功率應該在飽和輸出功率的基礎上再回退若干dB。

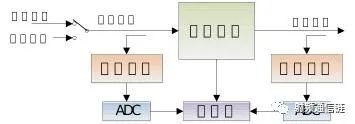

功放管的輸入、輸出阻抗隨頻率變化,使得輸出功率一樣隨頻率起伏,為了使輸出功率穩定,必須進行閉環控制,最佳閉環控制采用數字APC的方法,通過前向檢波,檢測輸出功率的偏差量,再通過數字衰減,調整激勵功率,是輸出功率穩定。

工作頻率越寬,功放的輸入、輸出匹配網絡越復雜,通過多級匹配展寬功放管的工作帶寬,只有功放管的輸入、輸出處于良好的匹配狀態,功放管的輸出功率才能達到最大,效率才會最低。三階互調也與匹配網絡密切相關,功放管有兩種匹配準則:按最佳互調和按最大輸出功率,這兩種匹配可能不會吻合,需要折中。

匹配網絡同時也是一種濾波器,濾波器的傳遞函數有個隨頻率變化的相位因子,可以改變不同頻率失真分量的相位,如果相位相反,則部分互調失真抵消,這就是最佳互調匹配。

3.輸出效率

效率關系到功耗,手持式采用電池供電,效率影響到電池的持續工作時間。從另一個層面,效率還影響到無用功耗,這部分功耗等于自身發熱,使器件溫度升高。

通常說的輸出效率將輸出功率與電源功耗相比:η=Pout/PDC×100%,另一個概念是附加效率PAE(Power-Add Efficiency),輸出功率扣除了輸入功率,是功放的凈輸出功率,是對效率更準確的描述,PAE=(Pout-Pin)/Pdc×100%。

4.穩定性

有兩種穩定狀態:條件穩定和無條件穩定,考慮到功放的工作頻率范圍寬,溫度適應范圍從-45~+85℃,條件穩定有潛在的自激危險,必須將功放設計成無條件穩定,即應通過反饋、偏置、匹配將功放牽引到穩定圓內。

5 關鍵指標

5.1 收發隔離度

收發隔離是對收發雙工器的要求,當發射的時候,會通過雙工器泄露到接收機前端,造成LNA飽和或損壞。設計多大的隔離度合適,一般原則是使射頻AGC不起控,避免發射轉接收后,因AGC時間常數(檢波器輸出)較大,射頻前端來不及響應,一般TDMA雙工器可以做到50dB以上。

5.2 寬帶噪聲

單純功放輸出的寬帶噪聲一般不大,當發射機激勵功放后,功放輸出的寬帶噪聲會顯著增大,為不影響附近工作的其它設備接收機,這個寬帶噪聲必須限制,通常要求地面設備近端低于-110dBc/Hz,偏離10%fo以遠寬帶噪聲低于-130dBc/H,特殊頻段甚至要求更低。

要達到這個指標,除了要限制接收機的輸出寬帶噪聲外,功放本身也需要優化設計。一般功放的總增益應該限制在30dB以下,功放的推動級輸出端應該采用調諧濾波器或濾波器組。這樣方有可能將輸出近端寬帶噪聲限制在-110dBc/Hz以下。

5.3 諧波抑制

功放具有非線性,輸出必然含有諧波,諧波屬于無用發射,會干擾附近其它設備接收機的工作,可以當作雜散看待。一般要求手持式諧波低于-50dBc,車載式、機載式諧波低于-70dBc。

為降低諧波水平,功放輸出端必須級聯濾波器,由于帶通濾波器的插損太大,一般采用低通濾波器,對于寬頻帶功放,fH/fL>1,諧波落在工作頻段內,所以需要低通濾波器組。

A類放大器在P1dB附近的2次諧波大約是-20~-25dBc,飽和輸出時諧波更大。AB類放大器由2個A類放大器組成,輸入、輸出端均有反相巴倫,功放輸出的偶數次諧波同相,經過后面的反相巴倫合成后,偶次諧波抵消。如果2個放大器的幅度平衡、相位平衡較好,2次諧波大約-30~-40dBc。相比之下采用AB類放大器,諧波抑制具有優勢。

經過推挽放大和不平衡-平衡轉化,諧波抑制可以提高,因此可以通過功率合成的辦法,提高諧波抑制。當fH/fL>>1,比如30~512MHz,頻率覆蓋達17倍,如果用濾波器來抑制諧波,至少需要含6個濾波器的濾波器組,結構十分復雜,插入損耗也不可小視,如果采用功率合成的方法(涉及到各支路幅度問題),難度會小很多。

5.4 三階互調(或ACLR)

功放是發射機的鏈路延伸,與發射機一樣,三階互調會影響ACLR,使EVM惡化,由于功放的輸出功率更大,功率回退較小,非線性更加嚴重。

三階互調指標主要用于衡量多信道、多載波時,互調分量對系統的干擾程度,任何2個信道都會產生2個三階互調產物,干擾上、下2個等間隔信道。

5.5 EVM

EVM是接收機解調的保證,EVM惡化太多,會損失解調信噪比,對于恒包絡調制,通常功放的EVM<5%,非恒包絡調制,為降低ACLR,功放輸出功率必須回退幾dB,EVM通常較好,<3%。

5.6 輸出駐波比

功放的輸出駐波比與激勵功率有關,當激勵為0與滿負荷激勵時,駐波比相差較大,不能用矢量網絡分析儀來測量,應該用通過式功率計進行測量,駐波比一般小于1.5。

5.7 輸出開短路保護

當功放輸出負載開路或短路,輸出功率全反射回功放管,與功放管輸出電壓疊加,使功放管漏極電壓加倍或等效短路,可能損壞功放管。為防止功放管損壞,通常降低激勵,使輸出下降3~10dB,保護功放管,當負載開短路恢復正常后,逐步恢復原激勵功率。

5.8 負載適應性

天線不是純阻負載,寬帶天線的阻抗變化很大,通信系統要求天線的駐波比不大于2.0。當駐波比等于1時,阻抗匹配,輸出功率最大;當駐波比為2.0時,阻抗失配,功放的輸出功率下降。通常,當采用駐波比為2.0的假負載時,功放輸出功率下降值應不大于1dB。

5.9 電源適應性

不管是電池供電還是外接直流電源供電,電源電壓并非一直保持恒定,當電源電壓升高、或下降時,功放輸出功率可能會發生變化,特別是恒包絡調制,功放工作在飽和狀態,電源電壓變高,飽和輸出功率變大,電源電壓變低,飽和輸出功率變小。

當電源電壓在極限電壓范圍內變化時,功放的輸出功率變化不應該超出2dB。除此之外,采用非恒包絡調制的波形,EVM還必須達標。

5.10 溫度穩定性

當工作溫度從最低到最高變化時,手持-25~+60℃,車載-45~+85℃,機載-55~+70℃,功放的輸出功率變化不大于±1dB,過溫可以進行熱保護,允許輸出功率降低3dB。

5.11輸出功率波動

在全溫范圍內、全頻率范圍內、標準輸出阻抗,功放的輸出功率應該保持穩定,輸出功率變化不大于±1dB。

5.2.1功耗(效率)

功耗與效率緊密相關,窄帶功放的輸出效率幾乎等于最大輸出效率,為了擴展帶寬,寬帶功放幾乎處于匹配狀態,效率大大下降,如何提高輸出效率與如何展寬功放的帶寬都是功放設計的最大難題。

5.12待機功耗

對于TDMA體制工作的設備,當處于接收狀態時,功放應該關閉,防止功放輸出噪聲干擾接收。由于功放斷電/上電時間達ms級,為適應設備收發轉換us級的需要,功放不能完全斷電,功放管只能處于待機狀態,加漏壓,只關閉柵壓。這樣流經功放管漏極的電流幾乎為零,起到降低功耗的目的,而且上電很快。

除了末級功放管外,推動級放大器也一樣需要待機,進一步降低功耗,降低噪聲。

5.13收發轉換時間

功放的收發轉換時間不是雙工器的T/R開關轉換時間,而是從功放的柵極打開開始,到輸出功率上升到90%的時間(保持激勵),同樣從功放的柵極關閉開始,到輸出功率下降到10%的時間(保持激勵)是發收轉換時間。

5.14雜散

功放本身應該不存在雜散問題,當功放的電源部分設計不良,出現內部浪涌或較大的紋波,電源可能會影響功放,產生電源雜散、開關雜散,

5.15穩定性

功放工作期間,或收發轉換期間,功放不應出現自激、瞬時指標異常、短時輸出功率變化太大,等不穩定現象。

5.16 溫度指示

功放管的管芯溫度最高,必須通過溫度傳感器實時采集功放管的殼溫,由處理器判斷是否過溫,是否要進行過溫保護。5.17正向、反相功率指示 正向、反相功率檢測用于功率閉環控制,穩定輸出功率。反相功率除以正向功率就是駐波比,處理器可以由此判斷功放負載是否異常。5.18 峰值電流

電源的最大負載能力是有限的,最大工作電流不能超過電源最大電流值,開機沖擊電流會產生開機浪涌,也不能太大。

5.20 電源

功放的電源必須經過相應處理,退耦、濾波、抑制浪涌,提高電磁兼容能力。濾波電容越大,電源越平滑,但開機沖擊電流也越大,單個濾波電容的ESR較大,頻繁的充放電使電容發熱,多個電容并聯,使ESR成倍降低,發熱大大減小,延長了電容的使用壽命。

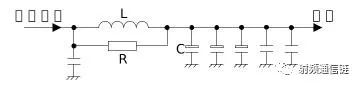

功放是設備功耗最大的部件,電源的充放電、浪涌容易引起電源欠阻尼振蕩,需要大功率電阻增大阻尼,抑制振蕩。通常將大功率電阻與磁芯電感并聯,對于直流,電阻被電感短路,不產生壓降,對于交流,電阻被接入,吸收振蕩。

電源處理

設備采用突發通信,發、收工作比不高,電源電流也是脈沖,如果采用電容存儲的方法,平滑電流,將大大降低輸入峰值電流,類似于脈沖功放。這種脈沖電源儲能電容不能直接并聯在電源線上,需要單獨設計電流源充電,限制充電電流。

6 布局

功放的電源電流很大,電壓較高,極易干擾小信號射頻和低頻電路,原則上功放按照信號流向布局,推動級與末級輸出采用空間隔離,防止自激。電源輸入口應該在末級功放管一側,所有小信號、控制電流電路應該遠離總電源濾波、退耦,遠離末級放大器。

采用金屬殼屏蔽的功放結構,應該實現仿真、計算腔體的諧振頻率,諧振頻率必須大于最高工作頻率的2倍以上,以留出足夠的安全余量。

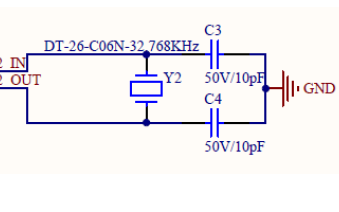

6.1時鐘

軍用通信設備通常工作于很寬的射頻頻段,射頻低端頻率較低,時鐘的諧波極易落入工作頻段內,成為無法避開的干擾。

如何處理時鐘問題,有一些基本的處理方法和原則。

6.1.1時鐘輸出波形

通常,晶體振蕩器直接輸出的都是切頂正弦,諧波十分豐富,可以通過低通濾波器將切頂正弦(準方波)過濾成正弦。為降低諧波干擾,寬帶設備使用的頻率參考源采用正弦波形,并通過BPF或LPF抑制時鐘諧波,使諧波低于-40dBc(切頂正弦的諧波更高),即便在這種情況下,時鐘的高次諧波泄漏到射頻通道仍然可以達到-80~-100dBm,遠高于接收靈敏度,使諧波頻率點不能正常使用。

由于晶振電路本身也會泄漏高次諧波,當后級濾波器對諧波的抑制達到一定程度,再增大抑制就幾乎沒什么改善。

另外,由于阻抗失配、電路寄生參數的影響,方波容易產生過沖和振鈴,使時鐘的過零點產生偏移,惡化相位噪聲。相反,正弦波不存在過沖和振鈴問題,所以正弦波的相位噪聲好于方波。這個結論在電路噪聲較小的情況下成立,當電路噪聲較大,疊加在正弦電壓上,同樣會引起過零點的偏移,而方波的偏移量就明顯小于正弦波。由于數字單元的脈沖噪聲很大,而射頻單元的噪聲相對較小,故將時鐘放在射頻部分是一種更合理的做法。

窄帶通信為降低電路復雜度、降低成本,時鐘通常采用方波。

6.1.2多時鐘同步

如果使用多時鐘,原則上各時鐘應該同源,即保持同步。不同于雷達,通信設備各時鐘之間不一定有很嚴格的相位關系,故有的設備多時鐘之間是異步的。需要注意的是,時鐘越多,諧波頻點也越多,干擾也就越嚴重。

6.1.3時鐘分配

設備需要很多路時鐘,ADC、DAC、FPGA、ARM、DSP、PLL等,原則上時鐘由射頻部分產生,射頻部分有幾路本振就應有幾路時鐘,對數字基帶部分可給出1~2路時鐘,ADC和DAC最重要,應優先使用。如果晶振的輸出電平較低,應先放大后分配。

有另一種做法,由數字基帶部分產生時鐘,在FPGA里將時鐘分作多路,共各部分使用,由于FPGA是數字器件,干擾嚴重,相位抖動也很大,用這種簡單方法得到的時鐘,基本指標會較。

6.2功耗

功耗在整個設備設計過程中都不可輕視,是需求嚴格限制的技術要求,功耗大還會產生過多熱量,使設備溫度升高,方案階段必須優先選擇電路簡單、功耗低的方案,器件選型也必須優先選擇功耗的器件。

功放是設備的發熱大戶,功放的結構、末級功放管的安裝位置影響到散熱效果,需要通過有限元熱仿真來確定最佳方案。設備對熱最敏感的單元、模塊應遠離功放的安裝位置。

6.3機內自檢BIT

機內自檢BIT(Built-in Test)是GJB要求的功能,完成六性規定的可測性,同時也輔助維修性對故障部位的判斷。機內自檢分為開機自檢、周期自檢、按需自檢。

自檢應完成對鏈路所有單元的檢測,故障隔離到模塊。為此,每塊PCB、每個功能單元的輸入輸出均需要檢測,PLL的鎖定指示需要檢測,電源是否正常需要檢測。自檢需要激勵源,發射機自身可以產生調制射頻信號,接收機需要增加輔助信號源,可以用晶振的諧波或者FPGA輸出方波的諧波,通過檢測輸入、輸出功率可以大致判斷模塊鏈路是否正常,若將發射機與接收機變環,接收機分析解調數據,計算EVM,可得出鏈路是否正常,發射、接收信號質量是否正常,間接知道本振是否鎖定。

自檢常用方法

1)開機自檢:開機上電后,程序加載完成,進入自檢模式,處理器采集所有功能模塊的狀態,異常者以故障標示,并上報。

2)周期自檢:處理器定時切換電路功能,進入自檢模式,采集所有功能模塊的狀態,異常者以故障標示,并上報。

3)按需自檢:當用戶或上位機下達單元自檢命令后,處理器完成當前工作,切換電路功能,進入自檢模式,處理器采集所有功能模塊的狀態,異常者以故障標示,并上報。

6.4電磁兼容

電磁兼容包含兩個方面:EMI和EMS。

EMI包含傳導CE(Conducted Emission)和輻射RE(Radiated Emission)。

CE的頻譜范圍25Hz~40GHz,RE的頻譜范圍25Hz~40GHz。

EMS包含CS傳導敏感度和RS輻射敏感度,CS:ESD,快速脈沖群,浪涌,注入電流,電源跌落;RS:強輻射電磁場。

審核編輯:湯梓紅

-

射頻

+關注

關注

104文章

5588瀏覽量

167779 -

發射機

+關注

關注

7文章

505瀏覽量

48039 -

DC-DC

+關注

關注

30文章

1949瀏覽量

81699 -

功放管

+關注

關注

1文章

27瀏覽量

17779

原文標題:射頻產品設計需要考慮哪些問題?

文章出處:【微信號:射頻學堂,微信公眾號:射頻學堂】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

射頻產品設計注意事項

射頻產品設計注意事項

評論