上回書說到SA0和SA1的測試方法。

這種測試方法是建立在一個前提上的,就是我們可以任意改變輸入信號的邏輯值。如果這個輸入正好就是整個芯片的輸入還好辦,直接在芯片外部改變即可。但很多時候我們需要測試芯片內部的各個邏輯單元,它們的輸入就會是在芯片內部,不那么好調整了,這可咋辦呢?

這個時候人們就想到了芯片中的重要元件——寄存器。如果我們給寄存器存儲相應的測試的邏輯值,讓這些reg的存儲的數據作為我們DFT測試的輸入,不就可以達到控制輸入信號的目的了嗎?但這種方法有一定局限性,這樣我們的DFT測試輸入位置必須保證是時序邏輯中寄存器的輸出pin才行,接收輸出信號就還是用探針就可以,沒有太多限制。

這樣的輸入限制有可能會導致我們無法完全測試出所有combinational cell的問題,但DFT工程師還是可以控制輸入信號測很多次,來盡可能多的覆蓋到能測的cell。DFT測試中有一個測試覆蓋率的概念,一般都會要求到90%以上。

然而使用reg來作為測試輸入又帶來了新的問題,那就是我如何給這些reg灌進我想要的值呢?要知道芯片在正常工作時reg之間是會互相影響的,我們很難控制在某一個時刻,很多個reg都正好輸出我們想要的某個邏輯值組(一般DFT工程師稱這種輸入邏輯組叫pattern,比如上篇提到的例子里,11、10就是不同的兩個pattern),怎么辦呢?

為了DFT測試,我們要對芯片進行大刀闊斧的改革!我們要把芯片中所有的正常reg全部升級!升級后的reg在可以正常工作的同時,還要支持一種模式,這種模式可以讓我們直接控制每個reg寄存的值。

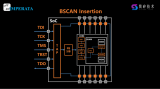

但是我們不可能把每個reg都接一根net到整個芯片的port,那port數量就太多了,根本不現實。如何只用控制一個port就能控制所有reg的值呢?別忘了,我們要控制的是寄存器,是被時鐘控制的,時鐘每跳變一次,信號往后傳輸一次,那么人們就想到把所有reg都串起來,后一個reg的輸入是前一個reg的輸出,我們只需要往第一個reg的輸入一個個灌值就行了。

比如三個reg串起來,我們想要一個101的pattern,就在第一個時鐘周期給第一個reg灌進去1,三個reg狀態是1xx;下個時鐘周期灌0,狀態變為01x,第三個周期灌1,狀態變為101.這就是我們想要的pattern,在這個時刻進行測試即可。

這里的reg的輸入輸出就是不同于電路的輸入輸出了,就是別的pin,稱為SI和SO,控制信號SE,我們把這個串稱為掃描鏈(scan chain)。

并且芯片工作的時鐘很快,DFT測試的時候相對就很慢,我們就需要一個專門的慢速時鐘用來測試,相應的這個慢速時鐘和正常的時鐘要經過一個選擇器接到reg上。

而后DFT工程師就要生成各個pattern了,最終把這一串值一個一個送到ATE機臺完成測試。呼~寫了這么多只講完了DC mode,但還有AC mode沒講...就是說我們上文提到的測試不涉及電路transition的問題,如果某個cell transition比預期的要慢,也會發生錯誤,這也得測才行,因此就不能用慢速時鐘了,得用常速時鐘才行,相應的測試方法更加復雜了。

-

寄存器

+關注

關注

31文章

5362瀏覽量

120900 -

DFT

+關注

關注

2文章

231瀏覽量

22781 -

時鐘芯片

+關注

關注

2文章

252瀏覽量

39926

發布評論請先 登錄

相關推薦

光學中簡單但重要的光學路徑與成像系統介紹

DFT的常見誤區與解決方案

DFT在生物信號分析中的應用

DFT的優缺點比較 DFT在機器學習中的應用

DFT與離散時間傅里葉變換的關系 DFT在無線通信中的應用

DFT在圖像處理中的作用 DFT在音頻信號處理中的應用

如何使用DFT進行頻譜分析

DFT在信號處理中的應用 DFT與FFT的區別

PCB星形接地的簡單介紹

簡單介紹下PWM原理與設計

DFT的簡單介紹(下)

DFT的簡單介紹(下)

評論