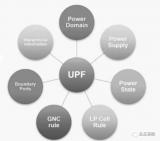

為實現低功耗設計,會采用多電源域、多電壓域、動態電壓調節等策略,需要使用到電壓控制單元,包括:isolation、level shifter、power switch、always-on、retention等,下面介紹學習的一些低功耗單元概念、lib格式和pg_type的三種類型。

低功耗單元匯總

isolation cells

隔離單元,用于在電源關斷之后,保持輸出為定值。用在shut-off電壓域的輸出。可以防止不定態信號值傳播引起下級邏輯錯誤,和當電壓在0.5 VDD附近時造成的短路功耗。

按照放置的位置可以分為sink-side和source-side。其中sink-side指的是放在always-on電壓域的單元,里面只有一個供電電源,即always-on的電源。source-side指的是放在可關斷電壓域的單元,里面有兩個供電電源,shutoff電源和always-on電源。

按照結構可以分為AND-type、OR-type和Latch-type類型的單元。

因此組合可以分文sink-side AND-type isolation cell、sink-side OR-type isolation cell、sink-side latch-type isolation cell、source-side AND-type isolation cell with global power、source-side OR-type isolation cell with global power、source-side latch-type isolation cellwith global power等。

level shifter cells

電壓轉換單元,用于將信號從一個電壓域轉移到另一個電壓域。一般用于低電壓域到高電壓域的轉換:因為假如低電壓域輸出0,那么能夠正常控制高電壓域的NMOS關閉和PMOS開啟,如果低電壓域輸出1,因為電壓較低,一般來說能夠控制高電壓域NMOS開啟,但是不能控制PMOS關閉,造成短路。

power switch cells

電源開關,能夠打開/關閉電壓域的供電電源,分為header(通過PMOS控制VDD開關)和footer(利用NMOS控制VSS開關,該庫沒有這一類型)。

學習了4種類型的HEADER結構的power switch cells。包括:

HEADER: switch connects the local power with global power,最基礎版,只有一個輸入使能。

HEADERBUF:switch with always-on buffer that connects the local power with global power,高級點的,有輸入使能和輸出。

HEADERBUFTIE::switch with always-on buffer that connects the local power with global power, the n-well and p-well are tied to VDDG and VSS respectively,在HEADERBUF基礎上給nwell和pwell加了偏置。

HEADERTIE:,switch that connects the local power with global power, the n-well and p-well are tied to VDDG and VSS respectively,在HEADER基礎上加了nwell和pwell偏置。

always-on cells

該電源供電來源于不會被關斷的電源域,但是可以被擺放到shut-off電源域,用于驅動always-on net。其結構是shutoff的VDD和VSS在基本單元版圖中為feedthrough形式,僅用于連接power rail保證不斷路,真正的供電電源為VDDG(backup power)。

類型:

TIEHI、TIELO、二輸入與或門、反相器、延時單元、BUF等。

Retention cells

能夠在電源關斷的情況下保持狀態。是時序邏輯,有兩種類型:flip-flop和latch。

沒找到retention cell的詳細結構。

特殊單元

FILLDCAP:為了防止大量標準單元翻轉造成的voltagedrop問題。其原理是電容公式為C=εS/4πkd,通過下面的版圖,增大了S,降低了d,因此提升了VDD和VSS之間的電容,能夠維持電源穩定。

此外還有為nwell和pwell提供偏置電壓的特殊單元。

LIB舉例:

sink-side isolation:

cell(A2BISO) {

cell_footprint : A2BISO ;

dont_touch : true ;

dont_use : true ;

is_isolation_cell : true ;

sec_class : combinational ;

sec_cell_type : clamp ;

valid_location : to ;

leakage_power

...

pg_pin(VDD) {

voltage_name : VDD ;

pg_type :primary_power;

related_bias_pin : "TW" ;

}

...

pin(Y) {

direction : output ;

function : "(A&!ENB)" ;

related_ground_pin : VSS ;

related_power_pin : VDD ;

power_down_function : "!VDD+VSS" ;

sec_pin_type : data ;

internal_power

timing

...

}

...

sec_pdt_pin(VDD) {

sec_pdt_pin_type : power ;

}

...

}

source-side isolation:

cell(GPA2BISO) {

cell_footprint : GPA2BISO ;

dont_touch : true ;

dont_use : true ;

is_isolation_cell : true ;

sec_class : combinational ;

sec_cell_type : clamp ;

valid_location : from ;

leakage_power()

...

pg_pin(VDD) {

voltage_name : VDD ;

pg_type :primary_power;

related_bias_pin : "TW" ;

}

pg_pin(VDDG) {

voltage_name : VDDG ;

pg_type :backup_power;

}

...

pin(A) {

direction : input ;

related_ground_pin : VSS ;

related_power_pin : VDD ;

isolation_cell_data_pin : true ;

internal_power

...

}

}

pin(ENB) {

direction : input ;

input_voltage :alwaysonpower;

related_ground_pin : VSS ;

related_power_pin : VDDG ;

isolation_cell_enable_pin : true ;

sec_pin_type : enable_low ;

always_on : true ;

internal_power

...

}

}

pin(Y) {

direction : output ;

function : "(A&!ENB)" ;

output_voltage :alwaysonpower;

related_ground_pin : VSS ;

related_power_pin : VDDG ;

power_down_function : "!VDD+!VDDG+!TW+VSS+VPW+SX" ;

always_on : true ;

internal_power

...

timing

...

}

sec_pdt_pin(VDD) {

sec_pdt_pin_type : power ;

}

...

}

Power Switch:

cell(HEAD) {

cell_footprint : HEADL ;

dont_touch : true ;

dont_use : true ;

switch_cell_type :coarse_grain;

sec_cell_type : complex ;

user_function_class : HEAD ;

leakage_power

...

dc_current(ivt125x25) {

related_switch_pin : SLEEP ;

related_pg_pin : VDDG ;

related_internal_pg_pin : VDD ;

}

pg_pin(VDD) {

voltage_name : VDD ;

pg_type :internal_power;(power switch的內部輸出電源)

direction : output ;

switch_function : "SLEEP" ;

pg_function : "VDDG" ;

}

pg_pin(VDDG) {

voltage_name : VDDG ;

pg_type :primary_power;(power switch使用的電源)

}

...

pin(SLEEP) {

direction : input ;

input_voltage : header ;

related_ground_pin : VSS ;

related_power_pin : VDDG ;

switch_pin : true ;

always_on : true ;

...

}

sec_pdt_pin(VDD)

...

}

pg_type的3種類型

primary_power/ground:

主電源/地,一般功能信號使用的電源/地,可關斷

backup_power/ground:

備用電源/地,always-on的電源/地

internal_power/ground:

內部電源/地,主要用于power switch的電源/地

審核編輯:黃飛

-

電容

+關注

關注

100文章

6066瀏覽量

150555 -

低功耗

+關注

關注

10文章

2408瀏覽量

103779 -

電壓控制

+關注

關注

0文章

111瀏覽量

22903 -

VDD

+關注

關注

1文章

312瀏覽量

33309 -

VSS

+關注

關注

1文章

35瀏覽量

21458

發布評論請先 登錄

相關推薦

電子書: 低功耗mcu的選型技巧與設計思路

STM32的3種低功耗模式

基于門控時鐘的低功耗電路設計方案

什么是低功耗,對FPGA低功耗設計的介紹

關于MCU的低功耗問題

什么是低功耗設計呢(UPF編碼篇)

低功耗設計單元匯總

低功耗設計單元匯總

![RA2快速設計指南 [7] 模塊停止功能,中斷控制<b class='flag-5'>單元</b>與<b class='flag-5'>低功耗</b>](https://file1.elecfans.com/web2/M00/A4/8C/wKgaomUDyOyAOoMAAAI-ZvuSIMY086.jpg)

評論