1 簡介

PSoC?4是一種可擴展和可重構的平臺架構,適用于一系列可編程嵌入式系統控制器,具有Arm?Cortex?-M0+ CPU,同時符合AEC-Q100標準。它結合了可編程和可重構的模擬和數字塊與靈活的自動路由,Cypress現在已被Infineon收購。Cypress 1982年在美國加州成立,主要提供汽車、工業、網絡平臺到互動消費以及移動設備的解決方案。該公司主要有四個部門:可編程系統部門、存儲產品部門、數據通信部門、新興技術部門。

2 PSoC?4介紹

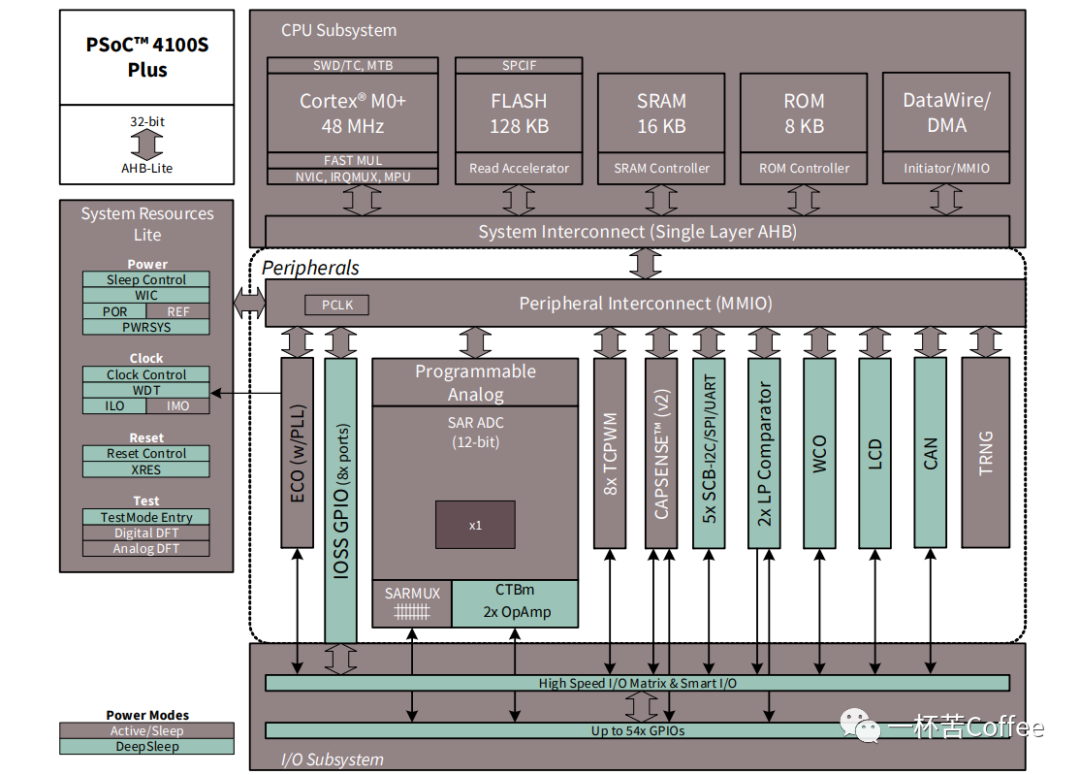

PSoC?4100S Plus是PSoC?4平臺架構的成員。它結合了帶有標準通信和定時外設的微控制器、具有一流性能的電容式觸摸傳感系統(CAPSENSE?)、可編程通用連續時間和開關電容模擬模塊以及可編程連接。PSoC?4100S Plus產品將與PSoC?4平臺的產品能實現向上兼容,以滿足新的應用和設計需求。

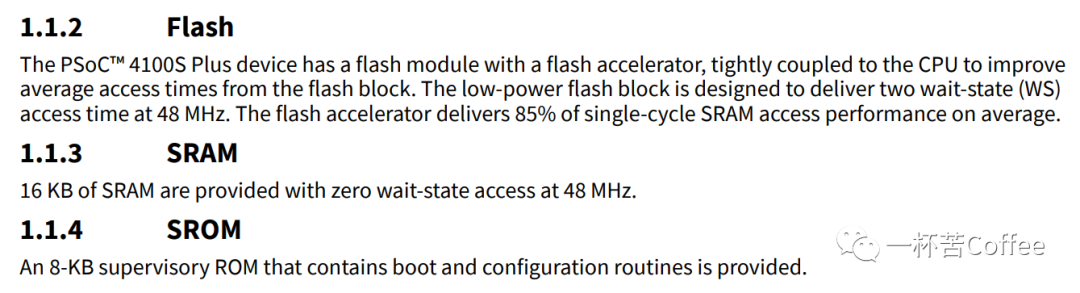

- 存儲器

提供128K Flash、16KB SRAM、5KB ROM。

- 電源介紹

PSoC?4100S Plus使用單個外部電源,工作范圍為1.8 V±5%(外部調節)或1.8 V至5.5 V(內部調節),并有三種不同的電源模式,其中轉換都是由電力系統管理的。PSoC?4100S Plus提供活動、睡眠和深度睡眠低功耗模式。所有子系統都在主動模式下運行。CPU子系統(CPU、閃存和SRAM)在睡眠模式下被時鐘門控關閉,而所有外設和中斷都是活動的,在喚醒事件上具有瞬時喚醒。在深度睡眠模式下,高速時鐘和相關電路被關閉;從該模式喚醒需要35μs。opamp可以在深度睡眠模式下保持運行。

- 時鐘系統

PSoC?4100S Plus時鐘系統負責為所有需要時鐘的子系統提供時鐘用于在不同時鐘源之間切換而不會出現故障。此外,時鐘系統確保不存在亞穩條件。PSoC?4100S Plus的時鐘系統由IMO, ILO, 32 khz手表晶體振蕩器(WCO), MHz ECO和PLL組成,并提供外部時鐘。WCO允許將IMO鎖定到32khz振蕩器。

硬件I2C塊實現了一個完整的多主和從接口(它能夠進行多主仲裁)。該塊能夠以高達1mbps (Fast Mode Plus)的速度運行,并具有靈活的緩沖選項,以減少CPU的中斷開銷和延遲。它還支持EZI2C,在PSoC?4100S Plus的內存中創建郵箱地址范圍,并有效地減少I2C通信,從內存中的數組讀取和寫入。此外,該塊支持8bit位深FIFO接收和發送,通過增加CPU讀取數據的時間,大大減少了由于CPU沒有及時讀取數據的而導致的時鐘擴展的需要。I2C外設兼容NXP I2C總線規范和用戶手冊(UM10204)中定義的I2C標準模式和快速模式Plus設備。I2C總線I/O是用Open Drai Mode的GPIO實現的。

- UART mode

這是一個全功能的UART,運行速度高達1mbps。支持汽車單線接口(LIN),紅外接口(IrDA)和智能卡(ISO7816)協議,所有這些都是基本UART協議的次要變體。此外,它支持9位多處理器模式,允許通過普通RX和TX線路連接的外設尋址。支持常見的UART功能,如奇偶校驗、中斷檢測和幀錯誤。8深FIFO允許更大的CPU服務延遲被容忍。

- SPI mode

SPI模式支持全摩托羅拉SPI, TI SSP(增加一個啟動脈沖用于同步SPI編解碼器)和National Microwire(半雙工形式的SPI)。SPI塊可以使用FIFO。

有一個CAN模塊,它實現了Bosch規范中定義的CAN 2.0B,并符合ISO-11898-1標準。

- GPIO

PSoC?4100S Plus具有多達54個gpio。每個GPIO有8種驅動模式:

- Analog input mode (input and output buffers disabled)

- Input only

- Weak pull-up with strong pull-down

- Strong pull-up with weak pull-down

- Open drain with strong pull-down

- Open drain with strong pull-up

- Strong pull-up with strong pull-down

- Weak pull-up with weak pull-down

- 特殊功能外設

- CAPSENSE?(手勢識別)

PSoC?4100S Plus通過CAPSENSE?sigma-delta (CSD)模塊支持CAPSENSE?,該模塊可通過模擬多路復用總線通過模擬開關連接到任何引腳。因此,CAPSENSE?功能可以在軟件控制系統中的任何可用引腳或引腳組上提供。為CAPSENSE?塊提供了PSoC?Creator組件,使其易于用戶使用。

屏蔽電壓可以在另一個模擬多路總線上驅動,以提供耐水能力。通過與傳感電極同步驅動屏蔽電極來提供水容忍度,以防止屏蔽電容衰減被感測輸入。也可以實現近距離感應。CAPSENSE?塊有兩個IDAC,如果不使用CAPSENSE?(在這種情況下兩個IDAC都可用),或者如果CAPSENSE?不耐水使用(一個IDAC可用),則可用于一般用途。CAPSENSE?模塊還提供10位斜率ADC功能,可與CAPSENSE?功能結合使用。CAPSENSE?模塊是一種先進的低噪聲可編程模塊,具有可編程電壓參考和電流源范圍,可提高靈敏度和靈活性。它也可以使用外部參考電壓。它具有全波CSD模式,交替感應到VDDA和接地以消除電源相關噪聲。

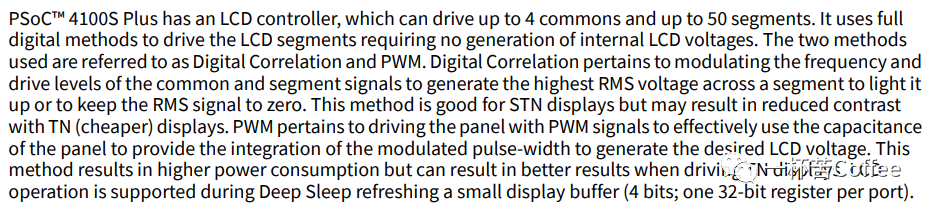

- LCD顯示驅動

3 方案介紹

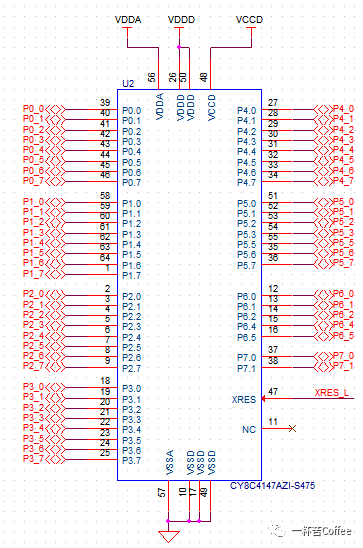

今天主要介紹的芯片是CY8C4147AZI-S475,共有8組端口。

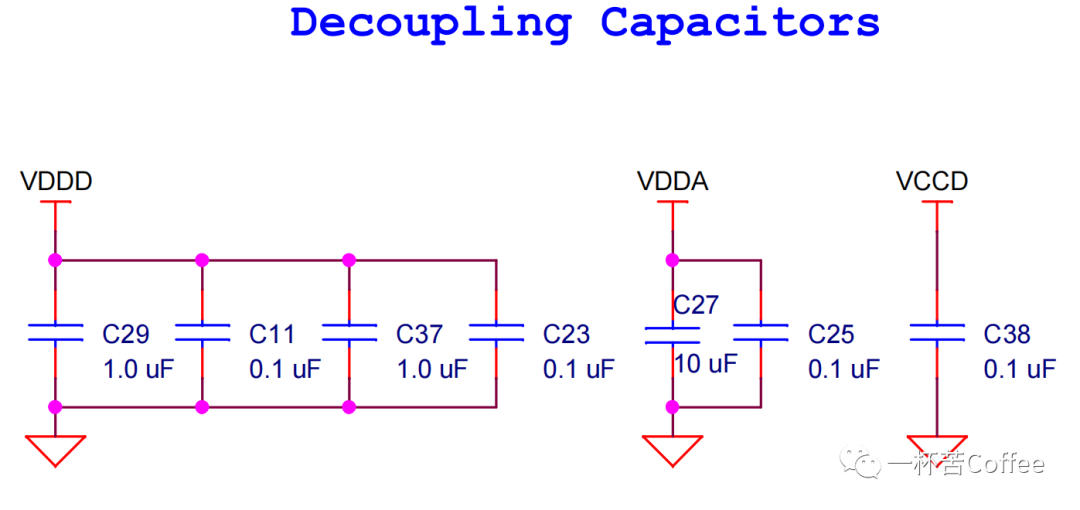

- 電源電路設計

電源部分,主要包含VDDD、VDDA和VCCD,各部的功能分別見下:

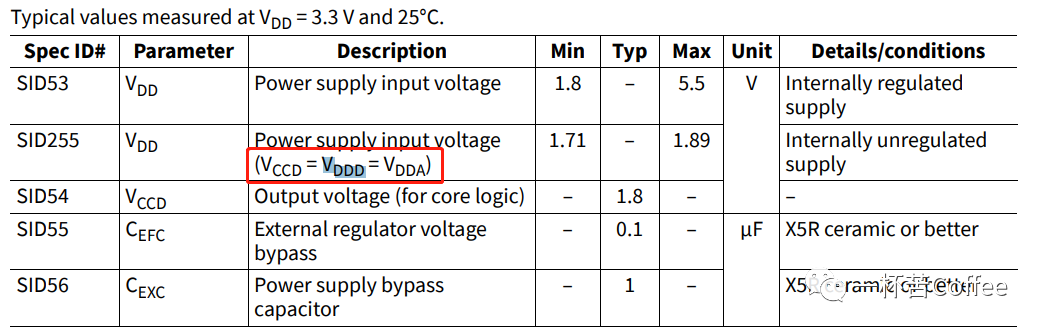

供電范圍設計指導:

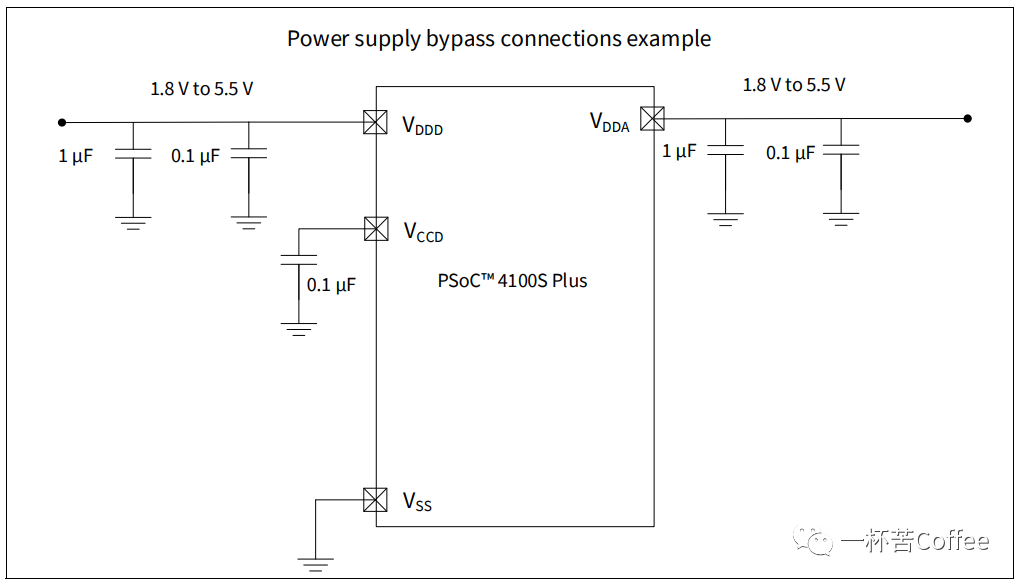

手冊設計參考設計:

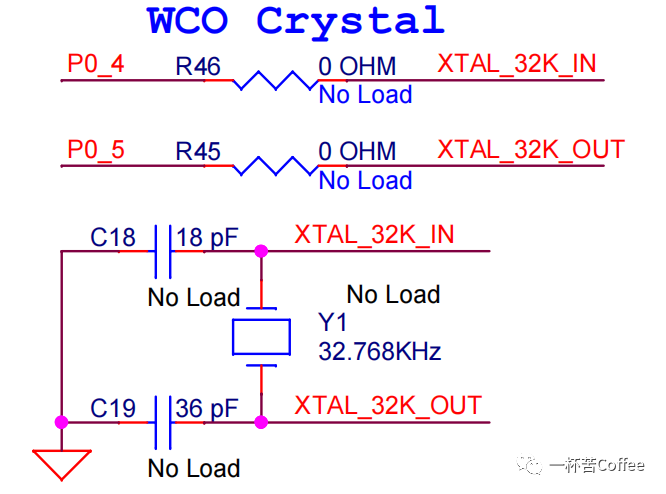

- 時鐘電路設計

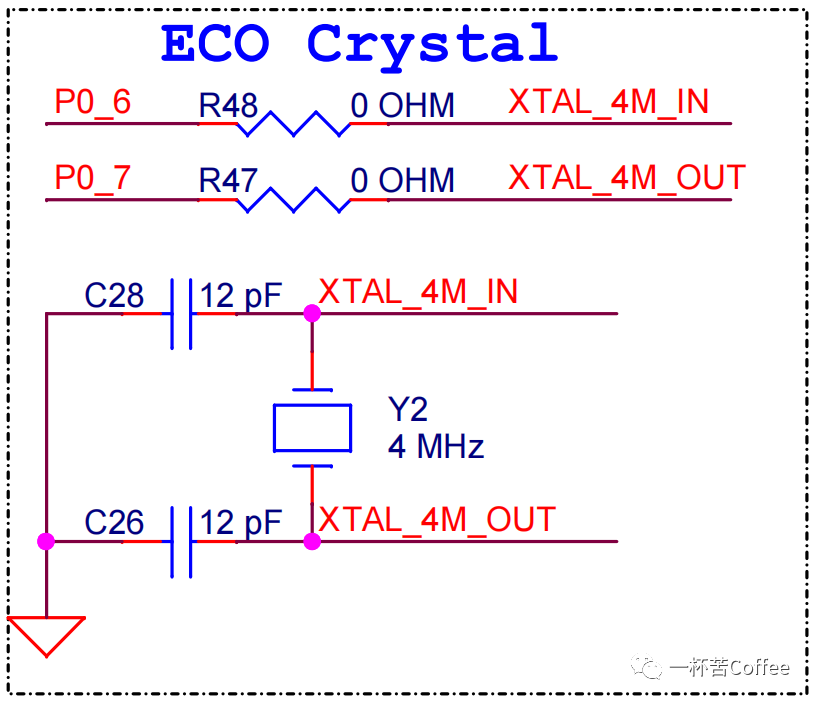

時鐘主要包含兩個部分,分別是主時鐘和RTC時鐘,電路設計分別見下:

- 主時鐘電路設計

時鐘的引腳為P0_6和P0_7,采用4M的晶振,時鐘輸入范圍4to33 MHz。

- 實時時鐘電路設計

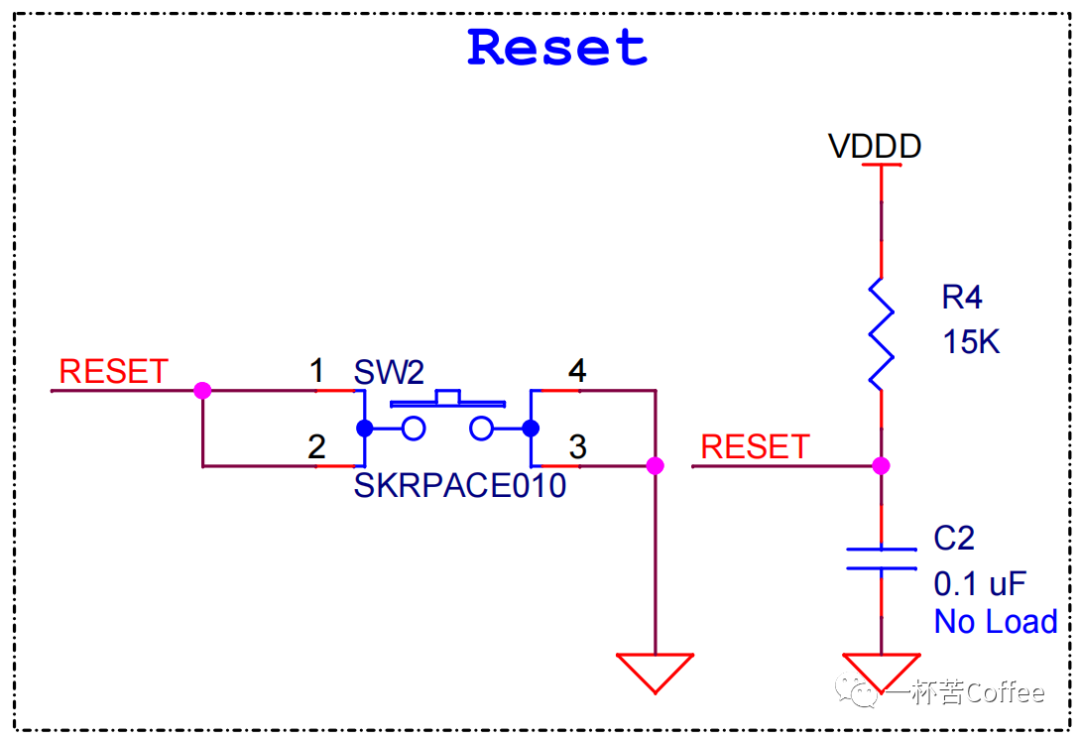

- 復位電路

復位采用的是低電平復位的方式,其中焊接C2可實現硬件消抖。

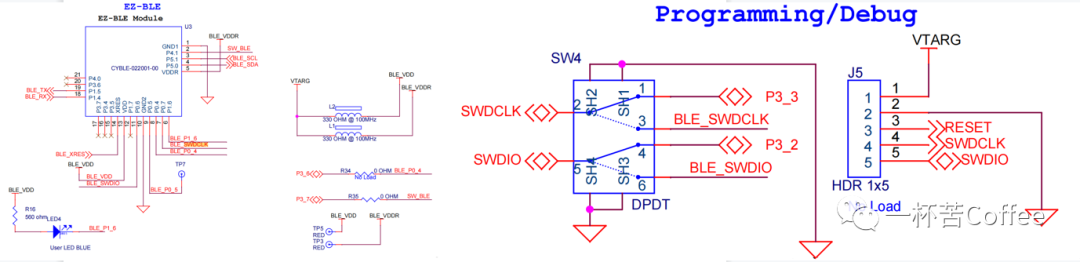

- 下載電路

軟件下載這個位置還沒有研究過,感興趣的朋友可以研究一下。

-

嵌入式

+關注

關注

5086文章

19141瀏覽量

305975 -

PSoC

+關注

關注

12文章

170瀏覽量

91976 -

嵌入式系統

+關注

關注

41文章

3595瀏覽量

129550 -

cpu

+關注

關注

68文章

10873瀏覽量

212095 -

電路設計

+關注

關注

6677文章

2455瀏覽量

204605

發布評論請先 登錄

相關推薦

怎么成為硬件電路設計高手?

硬件電路設計之PSoC?4100S Plus電路設計

硬件電路設計之PSoC?4100S Plus電路設計

評論