Xcelium工具中的SimVision是一個圖形化的工具,支持對SystemVerilog代碼的調試,同時內置svdebug布局幫助用戶來調試基于System Verilog的驗證環境。

使用SystemVerilog調試布局

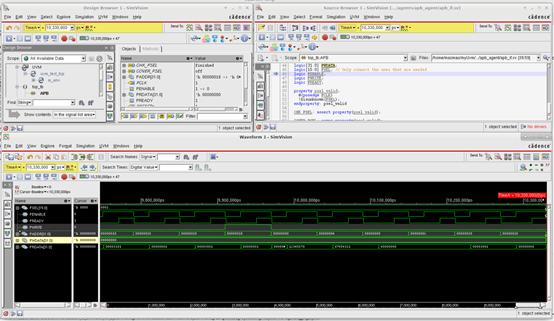

System Verilog調試布局由三部分組成。左上角Design Browser,可以訪問仿真對象,右上角為Source Browser,用來展示源碼,下側窗口為Waveform window,用來顯示波形。

啟動SystemVerilog調試布局的方式

命令行使用–layout svdebug來指定,如:

xrun –s –gui –layout svdebug –linedebug top_tb.sv

使用菜單欄切換布局

Window – Layout – SystemVerilog Debugging

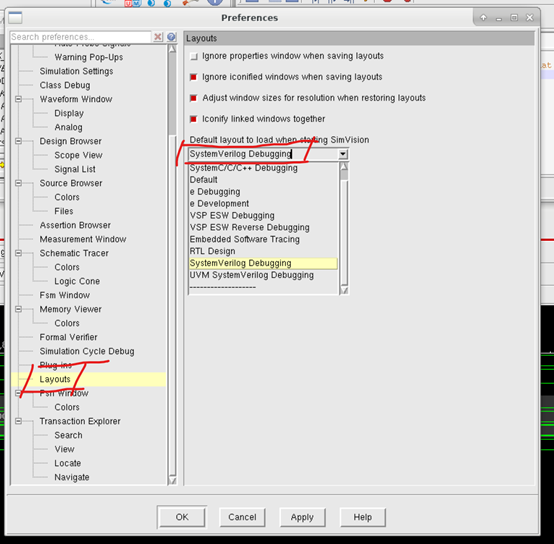

設置SystemVerilog為默認窗口布局的方式

啟動SimVison圖形界面

選擇Edit – Preferences

打開Layouts 標簽

選擇System Verilog Debugging為默認窗口布局

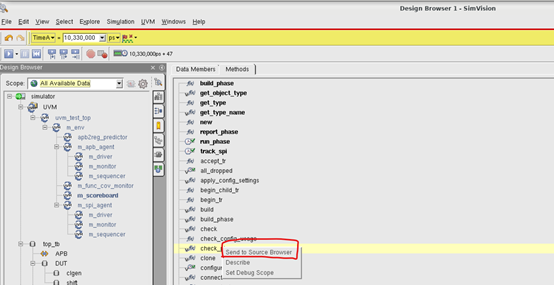

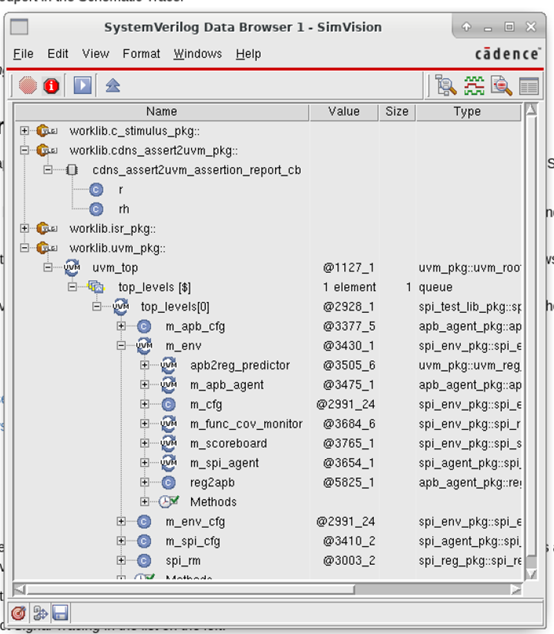

通過Design Browser查看SystemVerilog對象

這里可以看到對象的實例,包括它們之間的層級關系以及各個對象的數據成員和包含的task和function。還可以看到module實例及其層級關系。需要查看源碼,可以右擊目標選擇Send to Source Browser。

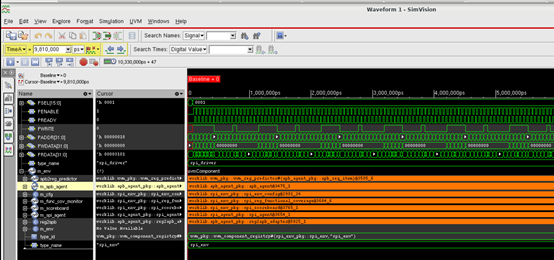

使用Waveform Window查看SystemVerilog對象

該窗口支持對 Static variables / Class variables /Queues / Packed structures / Packed arrays / Associative arrays / Dynamicarrays對象的查看

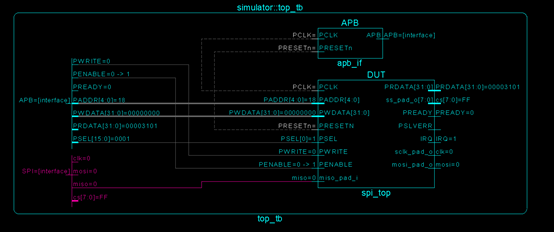

使用Schematic Tracer查看SystemVerilog對象

Schematic Tracer用來顯示interface、modports與rtl之間的連接關系。

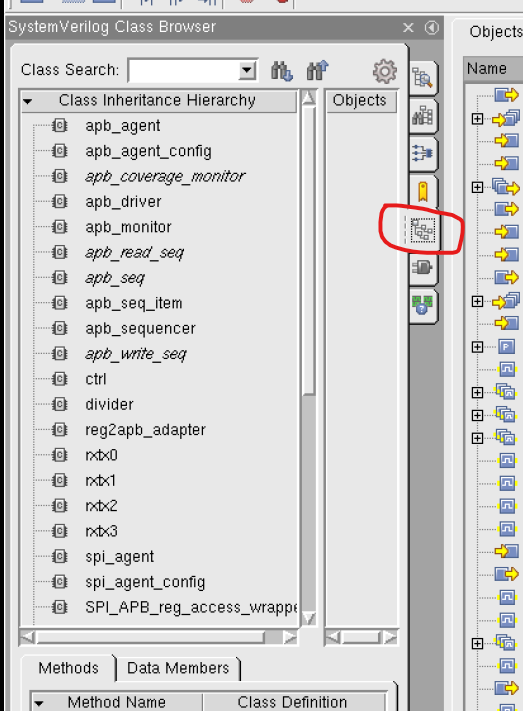

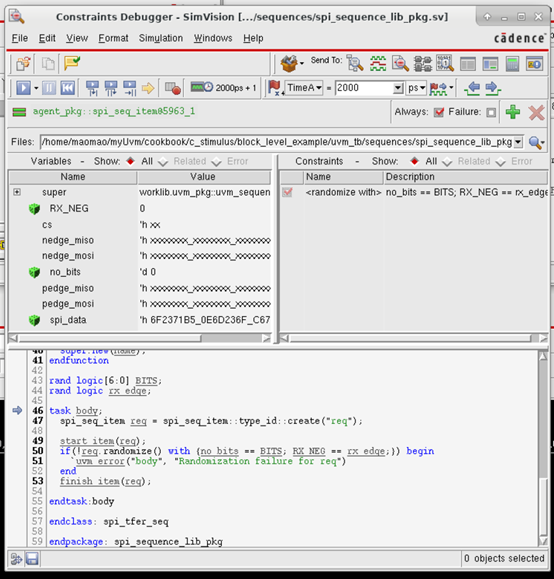

其他SystemVerilog調試窗口

SystemVerilog Class Browser

Data Browser

Constraints Debugger

審核編輯:黃飛

-

Verilog

+關注

關注

28文章

1351瀏覽量

110162 -

Layout

+關注

關注

14文章

405瀏覽量

61852 -

Xcelium

+關注

關注

1文章

5瀏覽量

5882

原文標題:xcelium筆記 | SimVision調試SystemVerilog簡介

文章出處:【微信號:ExASIC,微信公眾號:ExASIC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SystemVerilog 的VMM驗證方法學教程教材

[啟芯公開課] SystemVerilog for Verification

做FPGA工程師需要掌握SystemVerilog嗎?

SystemVerilog Assertion Handbo

SystemVerilog的斷言手冊

基于事件結構的SystemVerilog指稱語義

基于SystemVerilog語言的驗證方法學介紹

使用SystemVerilog調試布局方法

使用SystemVerilog調試布局方法

評論