1 簡介

本文主要講述一下DDR從0到1設(shè)計(jì)的整個(gè)設(shè)計(jì)的全過程,內(nèi)容涵蓋以下部分:

- SDRAM電路設(shè)計(jì)

- DDR4電路設(shè)計(jì)

下一篇文章內(nèi)容:

- DDR4級(jí)聯(lián)

- DDR4 Layout注意事項(xiàng)

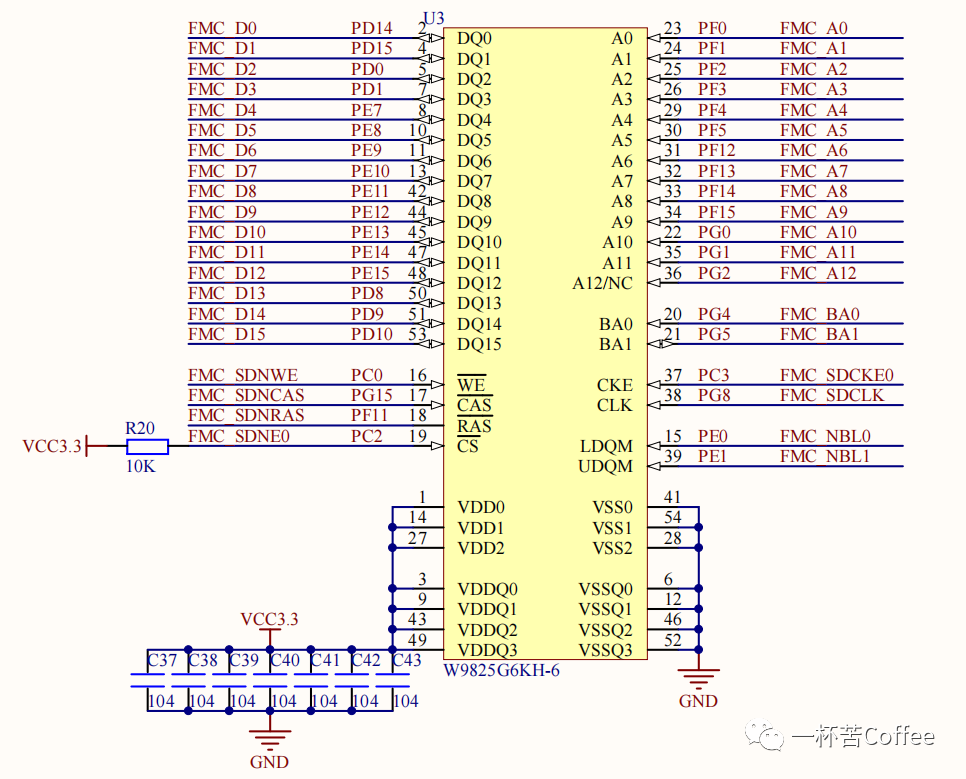

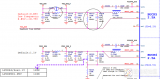

2 SDRAM電路設(shè)計(jì)

W9825G6KH-6是一種 動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器 ,存儲(chǔ)的容量為 256 Mbit ,支持最大時(shí)鐘頻率為 166MHz ,供電范圍 3V~3.6V 。

電路分析:

- 地址線A0-A12 :行地址線為A0-A12;列地址線為A0-A8,無需上拉電阻;

- 數(shù)據(jù)線DQ0-DQ15 :數(shù)據(jù)的輸入輸出線為DQ0-DQ15,無需上拉電阻;

- 片選信號(hào)CS :當(dāng)CS為低電平時(shí),表示選中該芯片。多個(gè)芯片復(fù)用或者與NAND FlashNor Flash復(fù)用時(shí),需要注意該信號(hào)。

- 行選通信號(hào)RAS列選通信號(hào)CAS :行選通信號(hào)為RAS(Row Addredd Strobe),低電平有效,列選通信號(hào)為CAS(Column Addredd Strobe),低電平有效;

- 寫使能信號(hào)WE :寫使能信號(hào)為WE(Rrite Enable),低電平有效;

- 數(shù)據(jù)輸入輸出屏蔽信號(hào)LDQMUDQM :用于在讀模式下控制輸出緩沖,在寫模式下屏蔽輸入數(shù)據(jù)。LDQM,UDQM這些信號(hào)線是為了實(shí)現(xiàn)字節(jié)訪問和半字訪問,LDQM控制低八位,UDQM控制高八位,這樣當(dāng)要按字節(jié)寫的時(shí)候,就把高八位屏蔽掉。

- 時(shí)鐘信號(hào)CLK :輸入時(shí)鐘信號(hào);

- 時(shí)鐘使能CKE :輸入時(shí)鐘使能引腳CKE,高電平有效。

- 電源引腳VDD和VDDQ :均采用3.3V供電。

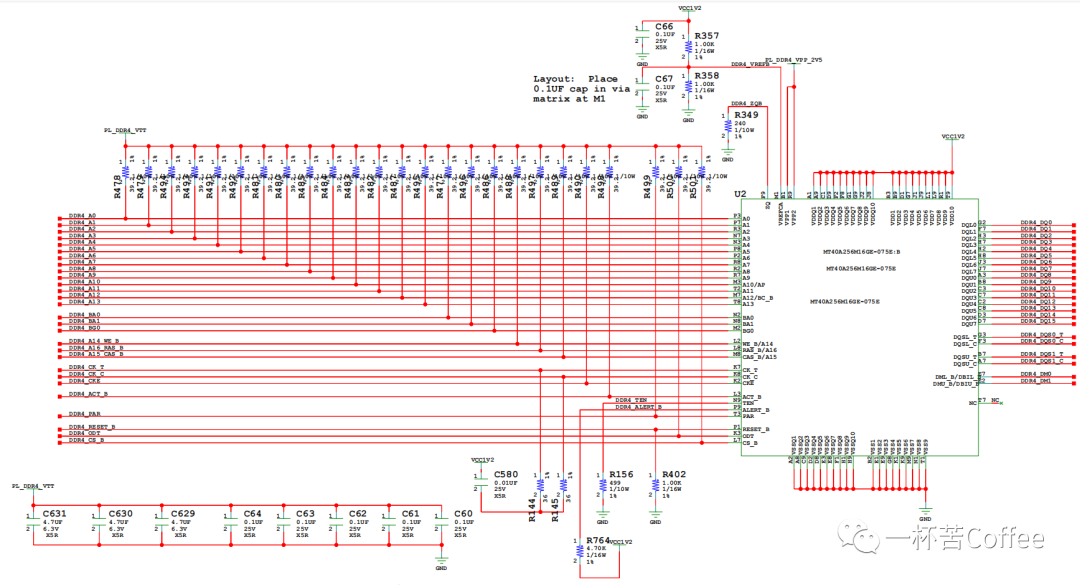

3 DDR4電路設(shè)計(jì)

今天使用的DDR顆粒為鎂光的MT40A256M16GE-075E(DDR 的廠家有三星、鎂光、海力士、東芝,國產(chǎn)廠家有長鑫、紫光),數(shù)據(jù)位寬為16bit,存儲(chǔ)的容量為4Gbit(容量計(jì)算請(qǐng)參考:硬件電路設(shè)計(jì)之DDR電路設(shè)計(jì)(1)),支持最高的時(shí)鐘頻率為1.333 GHz,供電范圍1.14V-1.26V,封裝形式為96-Ball FBGA。

電路分析:

- 電源設(shè)計(jì)

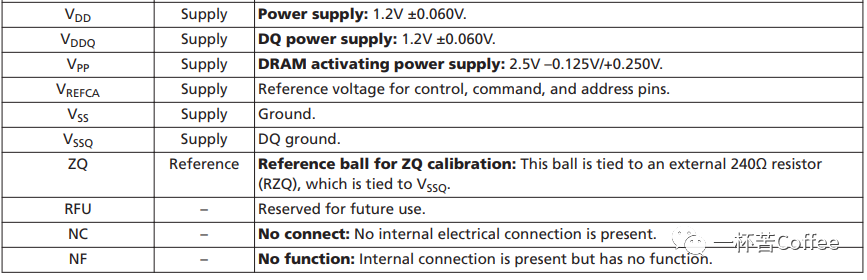

DDR4的電源主要有以下幾個(gè)部分: VDD(核電壓)、VDDQ 、 參考電壓VREF、VTT、激活電壓VPP 。

1、電源VDD

Power supply通常也會(huì)被稱為主電源(核電壓),其供電范圍: 1.2V ±0.060V。隨著不斷發(fā)展,主電源(核電壓)的電壓在不斷降低,具體見下:

| 序號(hào) | 版本 | VDD電壓 |

|---|---|---|

| 1 | SDRAM | 2.5V/3.3V |

| 2 | DDR2 | 1.8V |

| 3 | DDR3 | 1.5V |

| 4 | DDR4 | 1.2V |

| 5 | DDR5 | 1.1V |

2、電源VDDQ

DQ power supply是給IO buffer供電的電源,其供電范圍:1.2V ±0.060V。一般情況下,VDD和VDDQ合成一個(gè)電源使用,即VDDQ=VDD。

3、參考電壓VREFCA

控制、命令和地址的參考電壓。該電壓要求跟隨VDDQ,且VREF=VDDQ/2。參考電壓VREF可以通過兩種方式獲取:

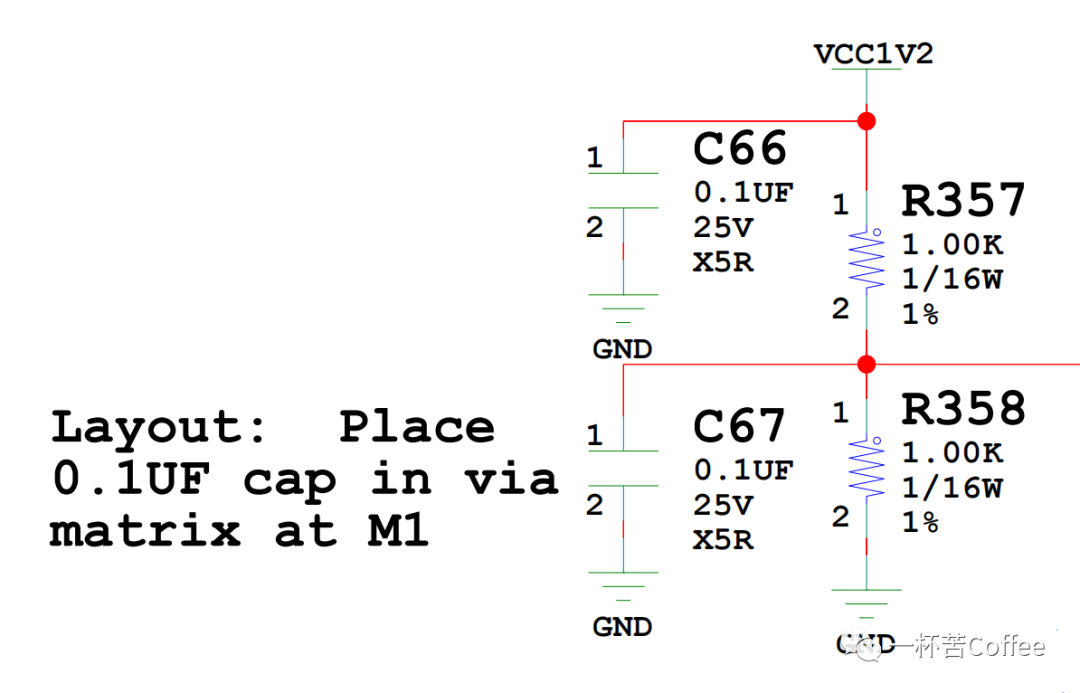

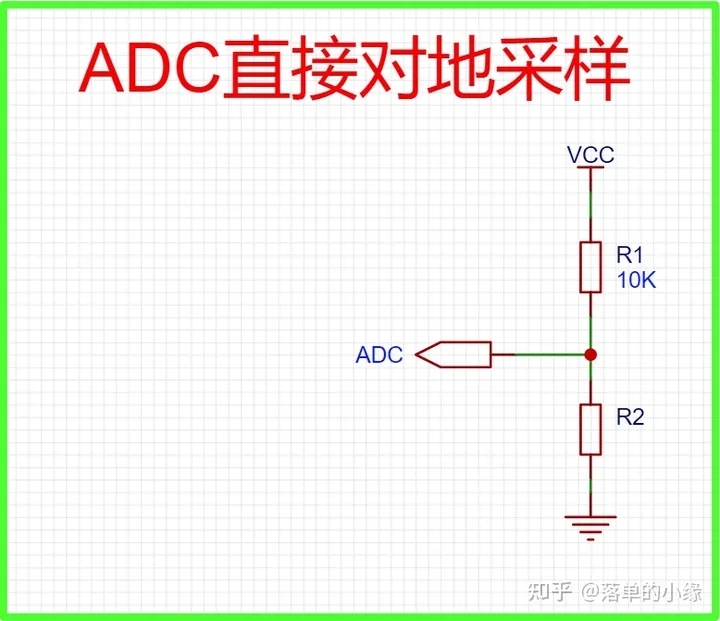

- 電阻分壓

VREF需要的電流比較小,一般為mA和幾十mA的數(shù)量級(jí),這種方式在布局上比較靈活,且成本較低。分壓電阻的取值范圍:100Ω-10kΩ,電阻精度為1%。參考電壓VREF每個(gè)分壓電阻上需要添加一個(gè)0.1uF的濾波電容。

- 電源芯片提供

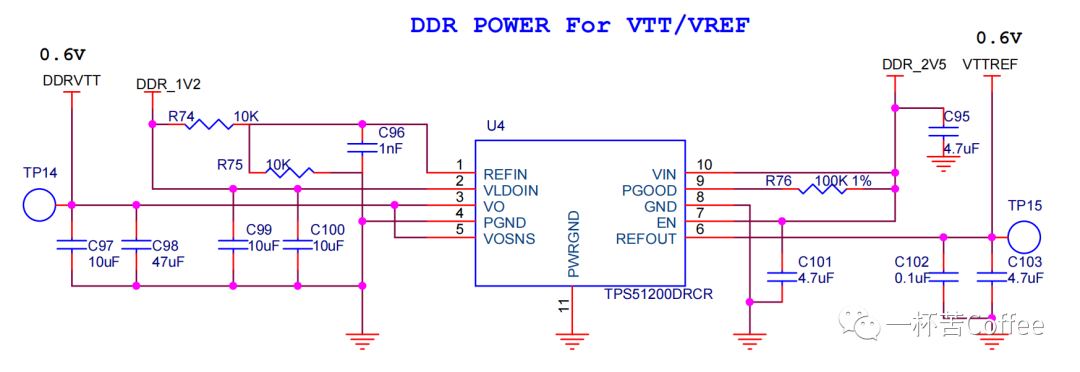

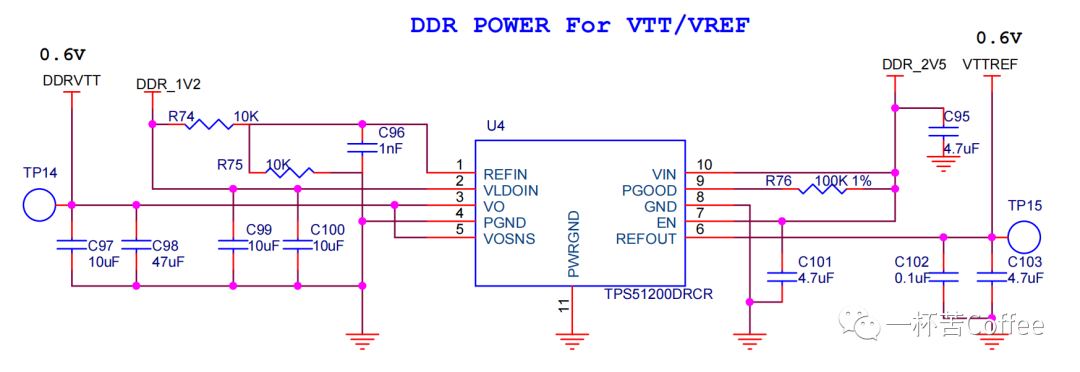

此處推薦的芯片是TID的電源管理芯片(TPS51200DRCR),TPS51200 器件是一款灌電流和拉電流雙倍數(shù)據(jù)速率 (DDR) 終端穩(wěn)壓器,專門針對(duì)低輸入電壓、低成本、低噪聲的空間受限型系統(tǒng)而設(shè)計(jì)。

TPS51200 可保持快速的瞬態(tài)響應(yīng),僅需 20μF 超低輸出電容。TPS51200 支持遙感功能,并滿足 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

此外,TPS51200 還提供一個(gè)開漏 PGOOD信號(hào)來監(jiān)測輸出穩(wěn)壓,并提供一個(gè) EN 信號(hào)在 S3(掛起至 RAM)期間針對(duì)DDR應(yīng)用對(duì)VTT進(jìn)行放電。

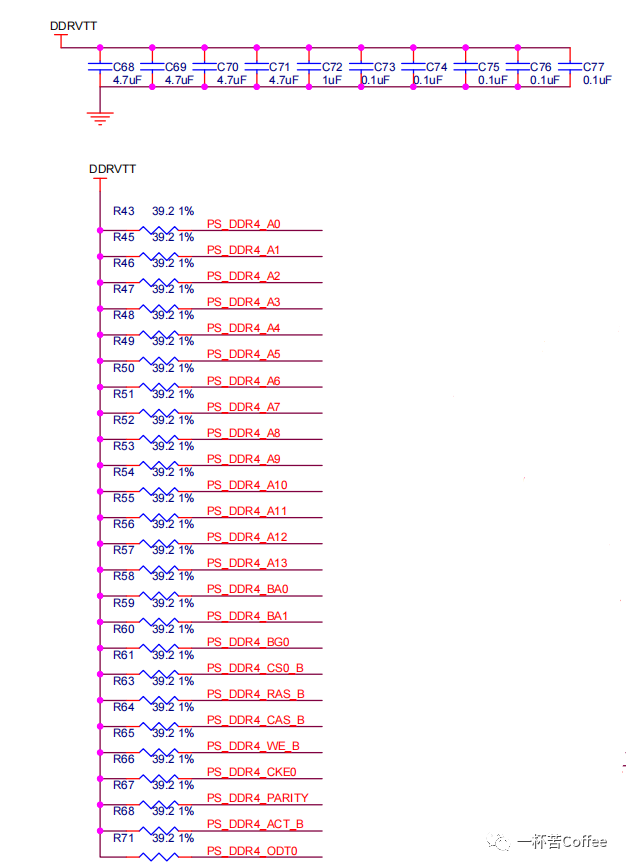

4、用于匹配的電壓VTT

VTT為匹配電阻上拉到的電源,VTT=VDDQ/2 。DDR的設(shè)計(jì)中,根據(jù)拓?fù)浣Y(jié)構(gòu)的不同,有的設(shè)計(jì)使用不到VTT,如控制器帶的DDR器件比較少的情況下。 如果使用VTT,則VTT的電流要求是比較大的,所以需要走線使用銅皮鋪過去。 并且VTT要求電源,即可以提供電流,又可以灌電流(吸電流)。

一般情況下可以使用專門為DDR 設(shè)計(jì)的產(chǎn)生VTT的電源芯片來滿足要求(曾經(jīng)使用過程中用了簡單的線性穩(wěn)壓器也沒發(fā)現(xiàn)出現(xiàn)什么問題,這種方式還是不建議的)。每個(gè)拉到VTT的電阻旁一般放一個(gè)10nF~100nF的電容,整個(gè)VTT電路上需要有uF級(jí)大電容進(jìn)行儲(chǔ)能。

一般情況下,DDR的數(shù)據(jù)線都是一驅(qū)一的拓?fù)浣Y(jié)構(gòu),且DDR2和DDR3內(nèi)部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到較好的信號(hào)質(zhì)量。而地址和控制信號(hào)線如果是多負(fù)載的情況下,會(huì)有一驅(qū)多,并且內(nèi)部沒有ODT,其拓?fù)浣Y(jié)構(gòu)為走T點(diǎn)結(jié)構(gòu)或Flayby結(jié)構(gòu),所以常常需要使用VTT進(jìn)行信號(hào)質(zhì)量的匹配控制。

5、激活電壓VPP

VPP為激活電壓,一般為2.5V電壓,上電的時(shí)間必須早于VDD,且在整個(gè)工作期間必須保持高于VDD的電壓。

6、ZQ電阻

輸出驅(qū)動(dòng)校準(zhǔn)的外部參考。這個(gè)腳應(yīng)該連接240ohm 電阻到 VSSQ。

- 時(shí)鐘設(shè)計(jì)

1、CK_T、CK_C

**CK_T、CK_C是差分時(shí)鐘輸入 。所有的地址、命令和控制信號(hào)都是在CK_T上升沿和CK_C下降沿的 交叉位置采樣 。

2、CKE

CKE是時(shí)鐘使能信號(hào),高電平有效。

- 數(shù)據(jù)信號(hào)

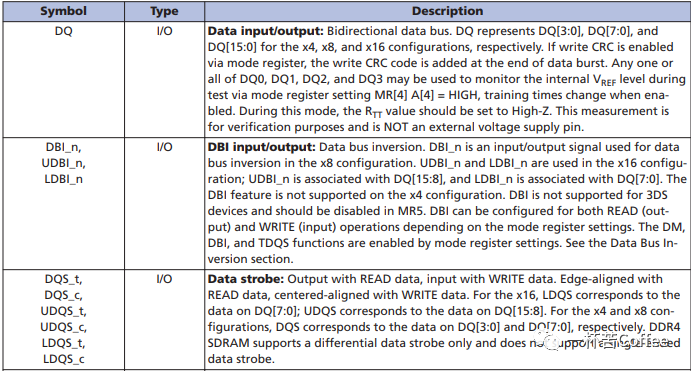

1、DQ數(shù)據(jù)線

數(shù)據(jù)輸入/輸出,雙向數(shù)據(jù)總線。

2、DBI_n、LDBI_N、UDBI_n

數(shù)據(jù)掩碼以及數(shù)據(jù)總線倒置:DM 信號(hào)是作為寫數(shù)據(jù)的掩碼信號(hào),當(dāng) DM 信號(hào)為低電平時(shí),寫命令的輸入數(shù)據(jù)對(duì)應(yīng)的位將被丟棄。DM 在 DQS 的兩個(gè)條邊沿都采樣。同時(shí),在 MR5 中的 A10,A11,A12 可選擇此信號(hào)是 DM 還是 DBl。在 X8 設(shè)備中, MR1 的 A11 可控制此信號(hào)是 DM 或者 TDQS, DBI 為低電平時(shí),DDR4 SDRAM 會(huì)將數(shù)據(jù)進(jìn)行翻轉(zhuǎn)存儲(chǔ)以及輸出,反之,DBI 為高電平時(shí),則不會(huì)翻轉(zhuǎn)數(shù)據(jù),TDQS 僅支持 X8 設(shè)備。

3、LDQS_T、LDQS_C

數(shù)據(jù)選通信號(hào):輸入時(shí)與寫數(shù)據(jù)同時(shí)有效,輸出時(shí)與讀數(shù)據(jù)同時(shí)有效,與讀數(shù)據(jù)時(shí)邊沿對(duì)齊的,但是跳變沿位于寫數(shù)據(jù)的中心。在 x16 系統(tǒng)中,DQSL 對(duì)應(yīng)到 DQL0_7;DQSU 對(duì)應(yīng)到DQU0_7;DQS_t,DQSL_t 與 DQSU_t 分別與 DQS_c, DQSL_c與 DQSU_c,對(duì)應(yīng)為差分信號(hào)對(duì)。DDR4 SDRAM 僅支持選通信號(hào)為差分信號(hào),不支持單根信號(hào)的數(shù)據(jù)選通信號(hào)。

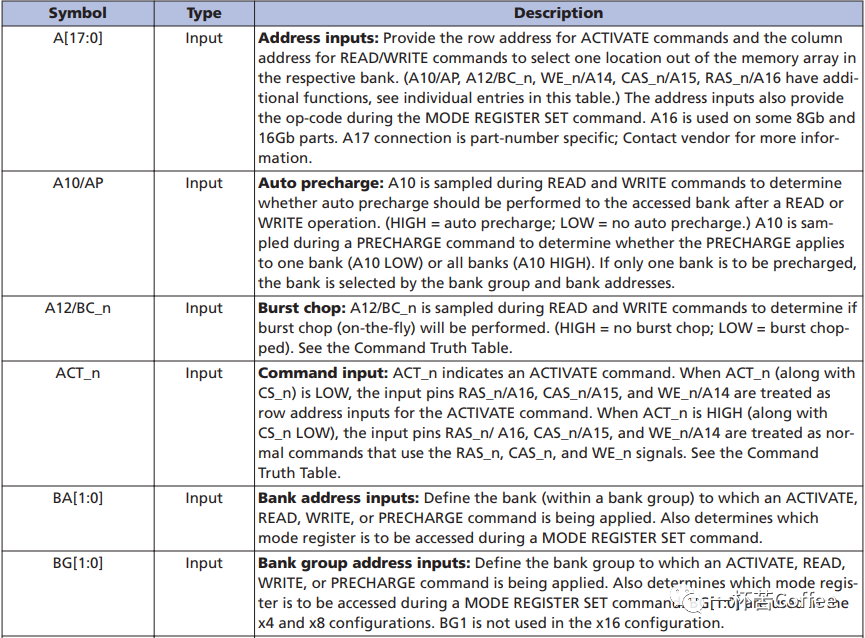

- 地址和控制信號(hào)

1、BA[1:0]

BANK地址輸入,用于指定當(dāng)前操作的BANK。

2、BG[1:0]

Bank Group 地址輸入;BG0-BG1可以選擇當(dāng)前的 ACT、READ、WRITE或是PRE 命令是對(duì)哪一個(gè) BANK 組進(jìn)行操作。在MODE REGISTER SET 命令中,BG0 也參與模式寄存器的選擇。在 X4、X8 系統(tǒng)中,有 BG0和BG1,而 X16 系統(tǒng)中,僅有 BG0。

3、A[17:0]

地址輸入引腳,其中有些引腳具有一些其它的復(fù)用功能,詳見下:

- A10有AP功能(自動(dòng)預(yù)充電)

- A12有BC_N功能(突發(fā)中止)

- A14有WE_N功能(寫使能)

- A15有CAS_N功能(行地址選通)

- A16有RAS_N功能(列地址選通)

4、ODT

片上終端電阻使能,高電平有效。

5、RESET

復(fù)位信號(hào),低電平有效。

6、ALERT_N

警告信號(hào),低電平有效。當(dāng)出現(xiàn)數(shù)據(jù)錯(cuò)誤(CRC校驗(yàn)錯(cuò)誤等)時(shí),該引腳會(huì)被拉低。

7、TEN

連接測試信號(hào),高電平有效。正常使用使用過程中,該信號(hào)必須為低電平。

8、PAR

奇偶檢驗(yàn)使能信號(hào)。這個(gè)功能必須通過寄存器來使能或失能。

9、ACT_N

激活信號(hào),低電平有效。ACT_N為低電平時(shí),A[16:14]為復(fù)用功能,ACT_N為低電平時(shí)為高電平時(shí),A[16:14]為地址線。

-

SDRAM

+關(guān)注

關(guān)注

7文章

430瀏覽量

55346 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164303 -

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6677文章

2463瀏覽量

205267 -

DDR

+關(guān)注

關(guān)注

11文章

715瀏覽量

65496 -

DDR4

+關(guān)注

關(guān)注

12文章

322瀏覽量

40937

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

模擬電路設(shè)計(jì)的注意事項(xiàng)

電子工程師的電路設(shè)計(jì)經(jīng)驗(yàn)分享

硬件電路設(shè)計(jì)的思路介紹

硬件電路設(shè)計(jì)的一般思路

基于PWM控制的buck電路設(shè)計(jì)

電路設(shè)計(jì)指導(dǎo)手冊(cè):數(shù)據(jù)轉(zhuǎn)換器

電路設(shè)計(jì)常見問題解答

Hot Swap外置軟啟電路設(shè)計(jì)

PCB及電路設(shè)計(jì)的接地資料基礎(chǔ)

STM32F103在電路板上怎樣做配套的電路設(shè)計(jì)呢?

硬件篇---電路設(shè)計(jì)之ADC采樣

硬件工程師電路設(shè)計(jì)的九大模塊電路

硬件電路設(shè)計(jì)之DDR電路設(shè)計(jì)(2)

硬件電路設(shè)計(jì)之DDR電路設(shè)計(jì)(2)

評(píng)論