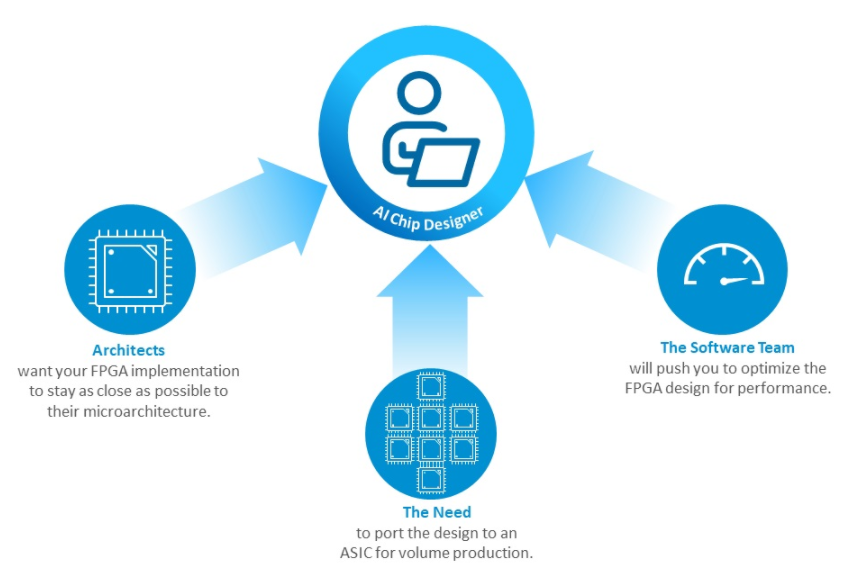

如果您選擇——大多數團隊都會選擇——用FPGAs進行概念驗證或驗證平臺,那么從一開始,您就會被同時拉向三個方向,如圖1所示。架構師希望您的FPGA實現盡可能接近他們的微架構。對他們來說,關鍵是看設計如何有效地實現他們的算法。但是,軟件團隊會督促您針對性能優化FPGA設計。這意味著改變架構以適應所選FPGA芯片的優勢和限制。你可以依靠營銷來增加這種壓力——主要是如果他們的計劃包括早期進入FPGAs市場。存在這樣一種風險,即概念的證明會像科學怪人一樣,有自己的生命。

圖1:如果你選擇在FPGAs中做一個概念驗證或驗證平臺,你會被拉向三個方向:來自架構師、軟件團隊和生產需求。

第三,需要將設計移植到ASIC上進行批量生產。這將為您帶來競爭力所需的性能、動力和面積。理想情況下,ASIC設計將準確反映最初的理論架構,并針對您選擇的ASIC工藝和IP庫進行優化。通過轉換成熟的FPGA設計,您可以在多大程度上獲得ASIC設計,這是一個至關重要的問題。答案將取決于架構師、FPGA和ASIC團隊合作的緊密程度。

也許支持這種說法的最好方式是看看一些區分人工智能加速器的架構特征,并在設計過程中遵循它們。

并行處理是人工智能加速器的基礎。它可以通過大量小型專用處理核心來實現,如特定算法的GPU。或者它可以以數據流的方式完成:專用處理器的流水線。這兩種架構都給FPGA實現帶來了挑戰。

設計者可以在RTL對處理元件及其互連進行編碼,并將RTL交給FPGA設計工具。但是,要獲得具有足夠設備利用率和性能的設計——獲得接近100%的布線——通常至少需要在平面規劃和布局方面進行人工干預。

這種規劃必須關注FPGA中資源的可用性和位置,而不是加速器的原始架構。例如,該體系結構可能希望計算元素群集在本地組中。然而,FPGA可能要求您將計算元素分散在整個芯片中,甚至將它們分成更小的模塊,以確保足夠的路由和RAM資源。這可能需要改變互連架構,例如改變總線結構。

還會出現其他選擇。例如,深度學習推理加速器的設計師經常使用精度降低的算法——比如8位而不是32位——來提高速度和節省能源。但出于性能和資源的原因,FPGA團隊可能希望使用FPGA的32位乘累加硬宏,而不是由邏輯單元構造的8位乘法器。這種選擇會使FPGA設計逐漸偏離原始架構,并影響轉換過程。

ASIC轉換

然后,是時候將實現轉移到ASIC上了。在小型、簡單的SOC中,FPGA到ASIC的轉換意味著一個近乎機械的逐步過程。拿出任何特殊的FPGA功能,如乘法累加模塊、高速串行接口、PCIe接口和DRAM控制器。用功能等同的ASIC IP替換它們,并對內部總線或接口進行任何必要的更改以連接它們。為了重新合成邏輯,插入新的時鐘網和自測結構,分配功率,并進行驗證。

這對于人工智能加速器來說仍然是可行的。在FPGA中工作的任何東西都可以通過這種方式轉移到ASIC中。但是,您為優化FPGA設計所做的設計更改呢?由于ASIC中有基本上無限的邏輯和路由資源以及大量的第三方IP庫,這些針對FPGA的更改將是不必要的,甚至可能適得其反。

進行轉換的團隊必須理解最初的設計意圖,這樣他們才能根據具體情況決定是使用FPGA設計還是恢復最初的架構。這對于確定合成哪個代碼和選擇如何最好地使用IP是正確的。

再舉兩個例子可能會有幫助。首先是記憶。由于它們的并行架構,AI加速器通常在處理元件內部或之間采用許多不同形狀、大小、類型和速度的小型RAM實例。這種做法完全符合ASIC設計的優勢,但它可能會對FPGA造成嚴重破壞。雖然可以將各組FPGA邏輯單元轉換成邏輯結構中的小RAM,但設計人員通常會在FPGA中使用大型硬連線可配置RAM模塊。這給FPGA團隊留下了兩個選擇:要么修改原始架構,使用大的共享RAM塊,而不是許多較小的塊,要么設計一個包裝FPGA的大塊RAM的包裝器,以仿真一組較小的實例,希望不會耗盡塊RAM附近的路由資源。

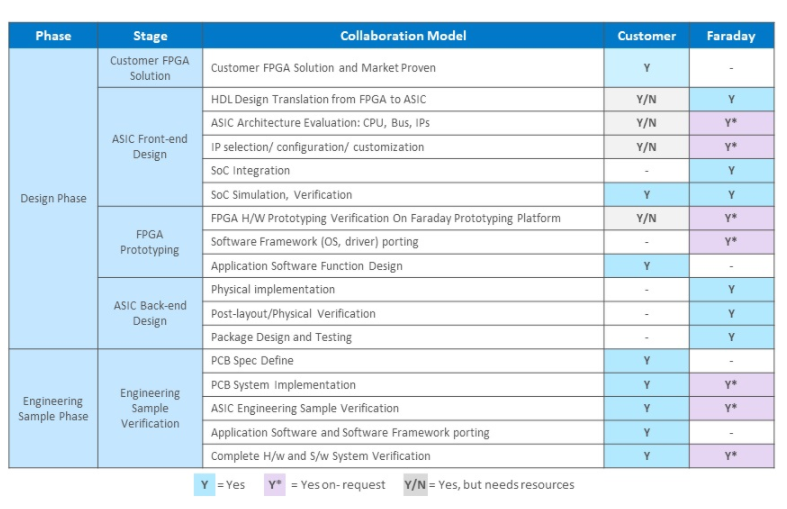

圖2:從FPGA遷移到ASIC提供了更多選擇。決策取決于對設計意圖的清晰理解。

當從FPGA轉移到ASIC時,有更多的選擇,如圖2所示。轉換團隊應該直接轉換FPGA設計嗎?經驗豐富的轉換供應商在ASIC設計中實現FPGA模塊RAM的功能不會有任何問題。或者團隊應該恢復到具有許多分散的RAM實例的原始架構?更小的ram將更快、更節能,并可能恢復原始架構的數據流,消除可能的內存瓶頸。然而,決策取決于對設計意圖的清晰理解。

多合一

還有多個FPGAs的問題。許多加速器設計對于單個FPGA來說太大,必須分布在多個芯片上。這些芯片如何相互通信將影響轉換過程。

例如,如果FPGA通過諸如存儲器總線的高速并行總線鏈接,設計者可以將所有FPGA的內容放入ASIC中,通過相同的并行總線排列鏈接。假設FPGAs通過類似PCIe的東西連接。在這種情況下,設計人員將不得不移除PCI接口,并根據模塊間數據流的性質,用直接并行連接或可能的片上網絡來取代它們。重要的是要回顧原始架構,看看它是否被修改以適應芯片到芯片接口的插入——例如,通過插入大緩沖存儲器或創建消息傳遞協議——并消除這些修改。

密切的合作

一旦功能設計完成,工作就可以進入時鐘架構了。這里,ASIC也不受FPGAs的限制。轉換團隊可以研究原始架構的工作原理,并利用它為本地時鐘區域、門控和頻移提供的所有機會,所有這些在ASIC領域都是現成的。

圖3:該表列出了FPGA到ASIC轉換過程中的每個步驟,并指明了負責執行該步驟的人員。

同樣,經驗豐富的轉換團隊可以利用他們對設計意圖的理解和對測試供應商能力的了解,利用加速器的并行架構來實施并行內置自測。這種優化超越了ASIC設計,深入到供應鏈中。做得好的話,它將大幅降低測試成本,顯著節約整體單位成本,如圖3所示。

我們已經看到,將AI加速器設計從中間FPGAs轉換為ASIC幾乎是一個機械的過程。但由于人工智能高度并行加速器的性質,理解原始設計意圖和架構微妙之處、能夠識別FPGA特定優化、擁有人工智能芯片經驗、能夠在客戶和供應商專家之間自由分配任務的轉換團隊可以實現更好的結果。從一開始,具有出色功率、性能和面積的ASIC就是設計的全部內容。

精彩推薦 至芯科技FPGA就業培訓班——助你步入成功之路、11月30號北京中心開課、歡迎咨詢! 基于LVDS的高速串行數據傳輸系統設計 FPGA學習-異步FIFO原型設計與驗證掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:為你的AI芯片從FPGA走向ASIC?

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1630文章

21762瀏覽量

604453

原文標題:為你的AI芯片從FPGA走向ASIC?

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ASIC芯片會成為AI的下一件大事嗎

大多數FPGA的程序存儲器(FLASH)為什么都放在外面呢?FPGA的主要應用

FPGA與ASIC的區別 FPGA性能優化技巧

ASIC集成電路與FPGA的區別

FPGA與ASIC的優缺點比較

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰的任務!

FPGA芯片你了解多少?

到底什么是ASIC和FPGA?

為你的AI芯片從FPGA走向ASIC?

為你的AI芯片從FPGA走向ASIC?

評論