本文轉(zhuǎn)載自:Cadence楷登PCB及封裝資源中心

導讀:移動數(shù)據(jù)的迅速攀升、蓬勃發(fā)展的人工智能及機器學習(AI / ML)應用,以及 5G 通信對帶寬前所未有的需求,導致對現(xiàn)有云數(shù)據(jù)中心的服務器、存儲和網(wǎng)絡架構(gòu)形成了巨大壓力。這些頗具挑戰(zhàn)性的應用需要高 I / O 帶寬和低延遲通信的支持。112G SerDes 技術具有卓越的長距性能、優(yōu)秀的設計裕度、優(yōu)化的功耗和面積,是下一代云網(wǎng)絡、AI / ML 和 5G 無線應用的理想選擇。由于更小的 UI 和更低的 SNR,在采用 112G 數(shù)據(jù)速率的過程中會遇到更大的挑戰(zhàn)。解決這一問題需要綜合考慮 RX / TX 規(guī)范、串擾、抖動、碼間干擾(ISI)和噪聲等多種因素,IEEE 標準也推出了通道運行裕度(COM)和有效回波損耗(ERL)作為測量標準,用于檢查高速串行系統(tǒng)的互操作裕度。

體現(xiàn)到信號完整性工程師的實際工作中,一項重要內(nèi)容就是要分析和優(yōu)化無源鏈路中的阻抗連續(xù)性和不同信號之間的串擾。封裝基板上的Core層過孔和BGA焊盤區(qū)域,是封裝上影響最大的阻抗不連續(xù)段,同時,這個區(qū)域因為有比較長的過孔縱向耦合,也是最容易引入串擾的地方,是我們需要重點優(yōu)化的。本文我們將聚焦封裝Core層過孔的阻抗連續(xù)性優(yōu)化。

一、封裝過孔區(qū)域的阻抗特性分析

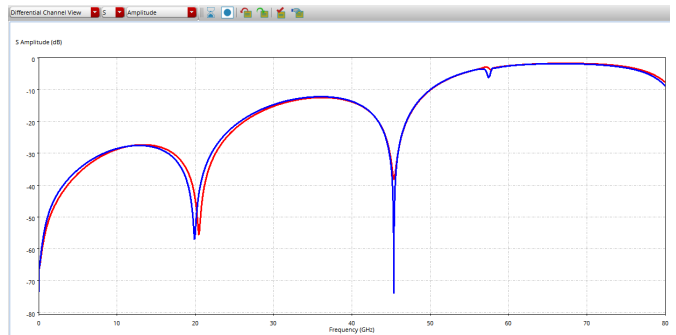

下圖是一個典型的封裝Core過孔和BGA焊盤區(qū)域的差分回波損耗結(jié)果。在奈奎斯特頻率以下的差模-差模回損都已基本控制到-20dB以下。

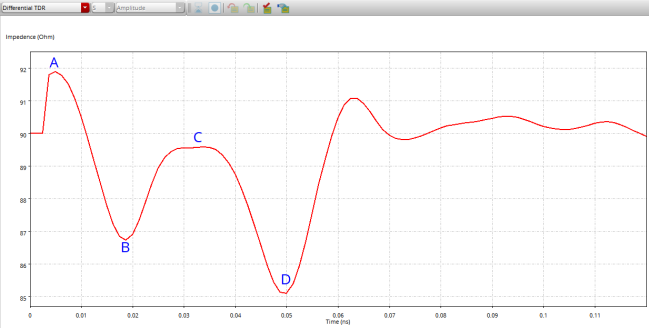

我們再看下其對應的TDR結(jié)果。可以看到實際阻抗并不是很靠近目標值90歐姆的一條直線,而是存在多個阻抗不連續(xù)點。

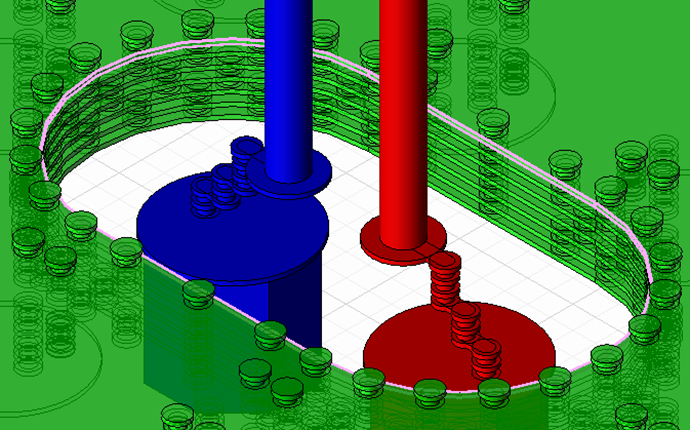

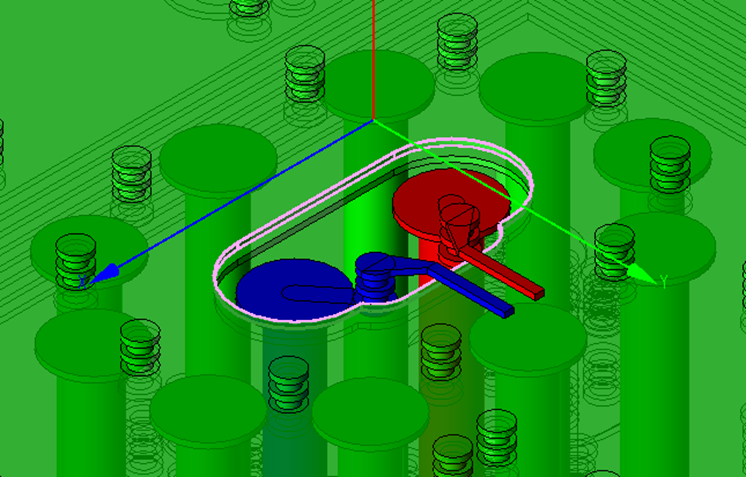

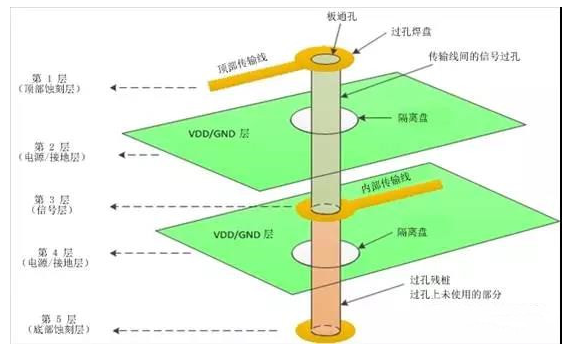

我們可以結(jié)合Layout結(jié)構(gòu)來理解其中的各段阻抗變化。首先看下阻抗最低的D點,這個地方對應的是BGA焊盤區(qū)域。一般要控制差分阻抗90歐,差分走線的線寬在25-30um左右,而BGA焊盤的直徑會有500-600um,所以這里最容易出現(xiàn)阻抗偏低的情況,需要把相鄰的幾層平面挖空。

另外一個阻抗較低的B點是Core層過孔的焊盤位置。這個焊盤的直徑一般是250-350um,也是比走線線寬高 了一個數(shù)量級,所以這里也要對相鄰幾層的平面做挖空處理。

C點區(qū)域是Core過孔的筒身部分。這部分會根據(jù)不同的筒身高度(Core層厚度)、相鄰層挖空大小/層數(shù)、周圍回流地孔的距離/數(shù)量等體現(xiàn)出容性或者感性。

最開始的阻抗較大的A點是走線在回流平面挖空區(qū)域部分。這個地方因為相鄰層都挖空掉,按照差分線寬量級的寬度布線,就會出現(xiàn)實際阻抗比目標值高的情況。

二、封裝過孔分析案例自動化建模

如上所述,封裝Core層過孔和BGA焊盤區(qū)域的多個布線參數(shù)都會影響這段鏈路的阻抗連續(xù)性,而且鏈路上不同組件對這些參數(shù)的調(diào)整方向需求有的還相互沖突,需要綜合權(quán)衡。這么多參數(shù)需要調(diào)整,不可能把所有的組合都先在封裝工具中設計出來再逐一用仿真工具提取模型進行分析。比較常見的做法是由資深的SI工程師根據(jù)經(jīng)驗判斷最關鍵的參數(shù)和大致的取值范圍,請封裝設計工程師做幾種不同的場景,然后在這基礎上把各層挖空大小做成變量進行掃描,或者根據(jù)仿真結(jié)果手動迭代調(diào)整參數(shù)。但是,這種做法存在很多限制:首先是嚴重依賴資深工程師的經(jīng)驗;其次是受項目交付周期限制,實際能覆蓋到的參數(shù)組合和調(diào)整范圍空間都比較有限;最后,如果出線層、疊層、材料、管腳排布、信號速率等發(fā)生變化,這些參數(shù)調(diào)整的結(jié)論不能直接復用,重新建模分析又非常消耗時間。

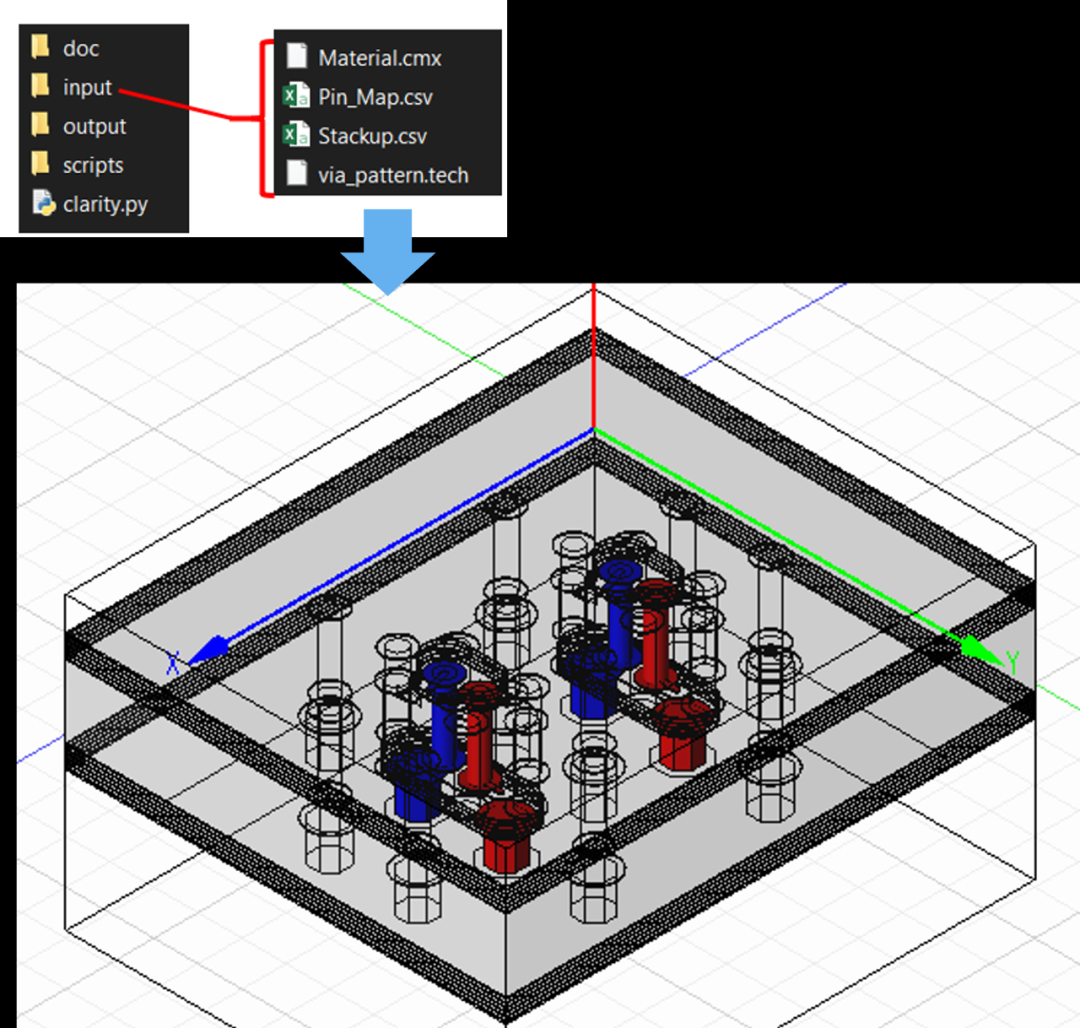

筆者的做法是利用仿真工具強大的參數(shù)表達式功能,編寫Python腳本,讀入PadStack、疊層材料、Pin Map等信息,自動創(chuàng)建封裝過孔優(yōu)化工程,把上述各種參數(shù),包括過孔間距、挖空區(qū)域大小、挖空層數(shù)、回流過孔方式、回流過孔距離、挖空區(qū)域走線線寬等,都在模型中做成可掃描的參數(shù)。這樣,調(diào)整參數(shù)時只要在仿真工具中修改數(shù)值,整個仿真結(jié)構(gòu)也會跟著改動,不需要返回封裝設計工具進行調(diào)整,更加方便快捷。而且,不管疊層、材料、管腳排布等如何變化,只要簡單修改輸入配置文件,十分鐘就能完成新的仿真工程建模。

三、設計參數(shù)自動化/智能化調(diào)整

完成仿真工程建模后,下一步就是要調(diào)整設計樣式的選擇和各設計參數(shù)的取值,以優(yōu)化阻抗連續(xù)性和串擾大小。這里會遇到一個問題,就是由于參數(shù)數(shù)量多,每個參數(shù)還有各自的取值范圍,即便SI工程師根據(jù)經(jīng)驗固定某些參數(shù)的數(shù)值或者綁定不同參數(shù)同步變化進行簡化,各參數(shù)排列組合后的取值空間很可能依然是巨大的。以5個獨立變量,每個變量10個掃描數(shù)值來計算,排列組合的取值空間就達到10^5=100,000個,這個數(shù)量級根本不可能在實際項目交付過程中去遍歷。即使是每個變量只有5個掃描數(shù)值,排列組合的取值空間也達到5^5=3125個,很難遍歷完成。因此,一般的做法還是需要SI工程師手動進行”調(diào)整參數(shù)”->”仿真”->”分析結(jié)果”->”調(diào)整參數(shù)”->”仿真“的迭代,受到項目交付周期和有效仿真/分析時間的限制,實際能完成的迭代次數(shù)非常有限,通常都不見得能找到最優(yōu)解。

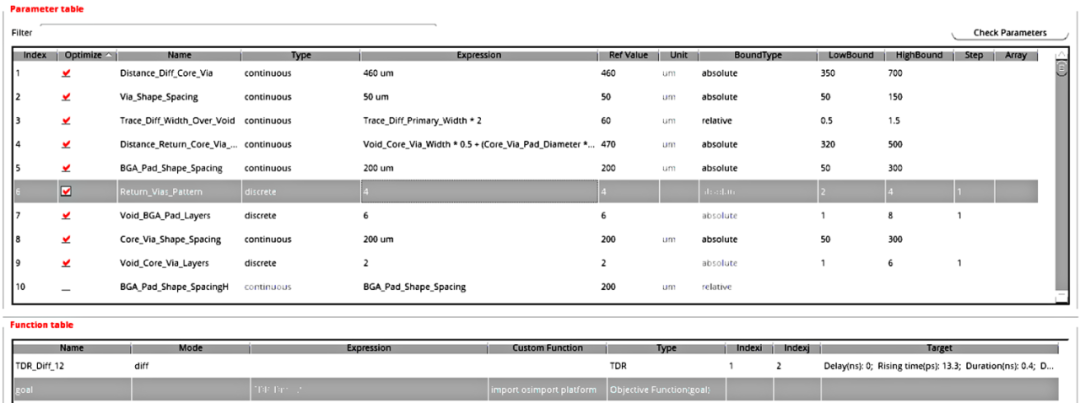

隨著仿真工具的發(fā)展,現(xiàn)在調(diào)參這個難題可以交給AI引擎來自動實現(xiàn)。這里我們利用Cadence最新推出的Optimality Intelligent System Explorer智能優(yōu)化引擎來完成封裝過孔優(yōu)化。在Cadence Clarity 3D Solver仿真工具中打開通過腳本創(chuàng)建出來的仿真工程,通過菜單欄命令打開Optimality Explorer優(yōu)化引擎,接下來只需要設置好需要調(diào)整哪些參數(shù)、每個參數(shù)的取值范圍,然后定義好我們要優(yōu)化的目標、設置并行跑的任務數(shù)量和仿真服務器資源,剩下的就是等Optimality Explorer根據(jù)機器學習算法自動完成” 調(diào)整參數(shù)”->” 仿真”->” 分析結(jié)果”->” 調(diào)整參數(shù)”->” 仿真 “的迭代,最終得到我們想要的優(yōu)化結(jié)果了。

值得一提的是,Optimality Explorer除了官方給出的一些常用的插損、回損、串擾、TDR等優(yōu)化目標,還支持Python接口,可以用Python自定義任意的目標函數(shù),比如本例我們用了自定義的TDR指標作為優(yōu)化目標,綜合考慮了TDR結(jié)果中的阻抗偏差最大值、阻抗偏差峰峰值、偏差阻抗長度等指標。

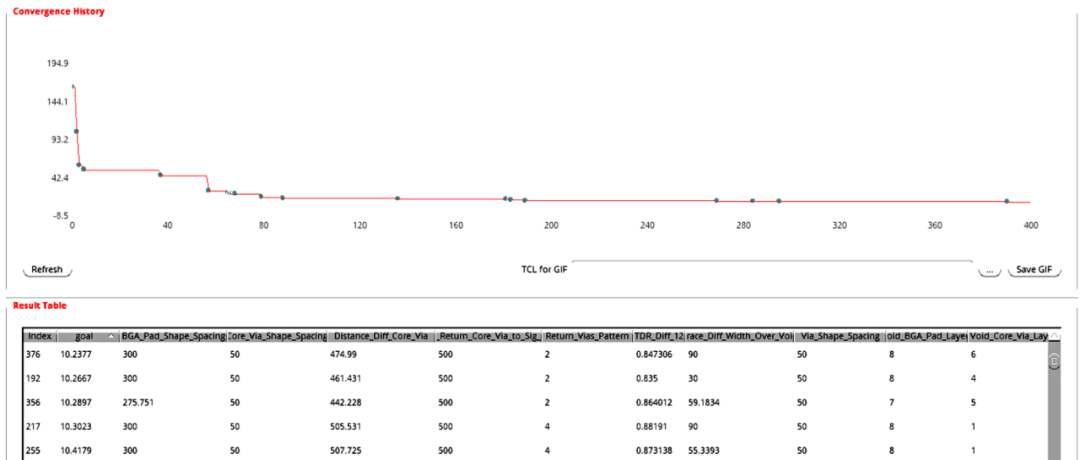

Optimality Explorer的收斂曲線如下。經(jīng)過幾十次迭代后,得到的仿真結(jié)果TDR指標就已經(jīng)優(yōu)于工程師手動迭代的結(jié)果。因為是工具自動調(diào)參,不需要工程師干預,我們可以按原定設置最大迭代次數(shù)繼續(xù)進行優(yōu)化,進一步得到更優(yōu)化的結(jié)果。

審核編輯 黃宇

-

阻抗

+關注

關注

17文章

958瀏覽量

45986 -

封裝

+關注

關注

126文章

7916瀏覽量

142998 -

BGA

+關注

關注

5文章

543瀏覽量

46882 -

焊盤

+關注

關注

6文章

551瀏覽量

38150 -

過孔

+關注

關注

2文章

200瀏覽量

21900

發(fā)布評論請先 登錄

相關推薦

焊盤差不多的連接器,阻抗能有多大差異?

OSI七層模型中的數(shù)據(jù)封裝過程

不同BGA封裝類型的特性介紹

BGA封裝的測試與驗證方法

Xilinx 7系列FPGA PCB設計指導

PCB阻抗匹配過孔的多個因素你知道哪些?

Xilinx FPGA BGA設計:NSMD和SMD焊盤的區(qū)別

BGA焊盤設計有什么要求?PCB設計BGA焊盤設計的基本要求

PCB設計優(yōu)化丨布線布局必須掌握的檢查項

過孔能否打在焊盤上?

PCB過孔的基礎知識與設計驗證

自動化建模和優(yōu)化112G封裝過孔 ——封裝Core層過孔和BGA焊盤區(qū)域的阻抗優(yōu)化

自動化建模和優(yōu)化112G封裝過孔 ——封裝Core層過孔和BGA焊盤區(qū)域的阻抗優(yōu)化

評論