電子硬件概覽

- FET:場效應晶體管

- FET是場效應晶體管,它通過控制柵極電壓來控制源極和漏極之間的電流,從而實現邏輯功能。

- CMOS:硅基互補金屬氧化物半導體晶體管

- CMOS是互補金屬氧化物半導體晶體管,它是一種基于硅基材料的半導體器件,具有高速度、低功耗、高集成度等優點。

- 摩爾定律已經失效,正在尋找“超越摩爾”的技術

- 為了超越摩爾定律,人們正在探索新的技術,如三維集成、柔性電子、生物電子等。

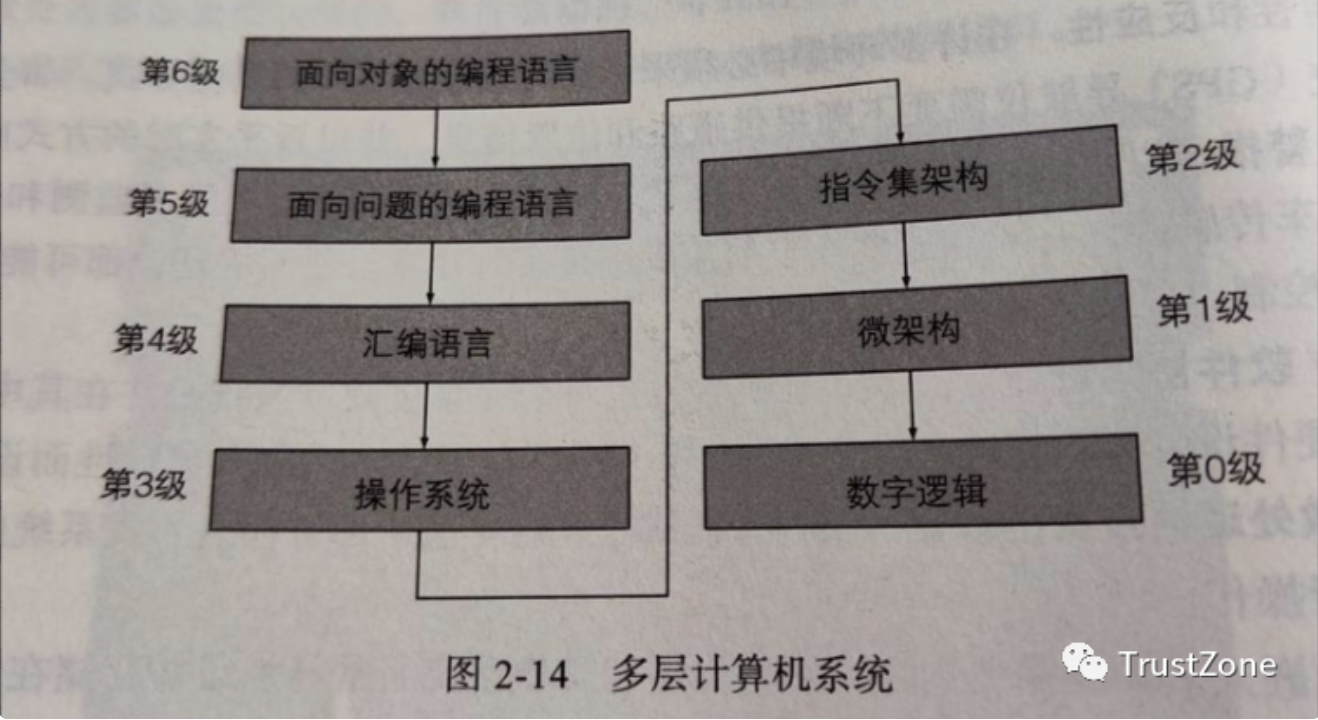

一、數字邏輯

數字邏輯是處理數字信號的邏輯,實質上是指基于二進制數學或布爾代數的邏輯。指用數字表示數字電路的信號和序列。

- 1、二進制邏輯:正電壓表示為邏輯1、高、真(true);無電壓表示為邏輯0、低、假(false)

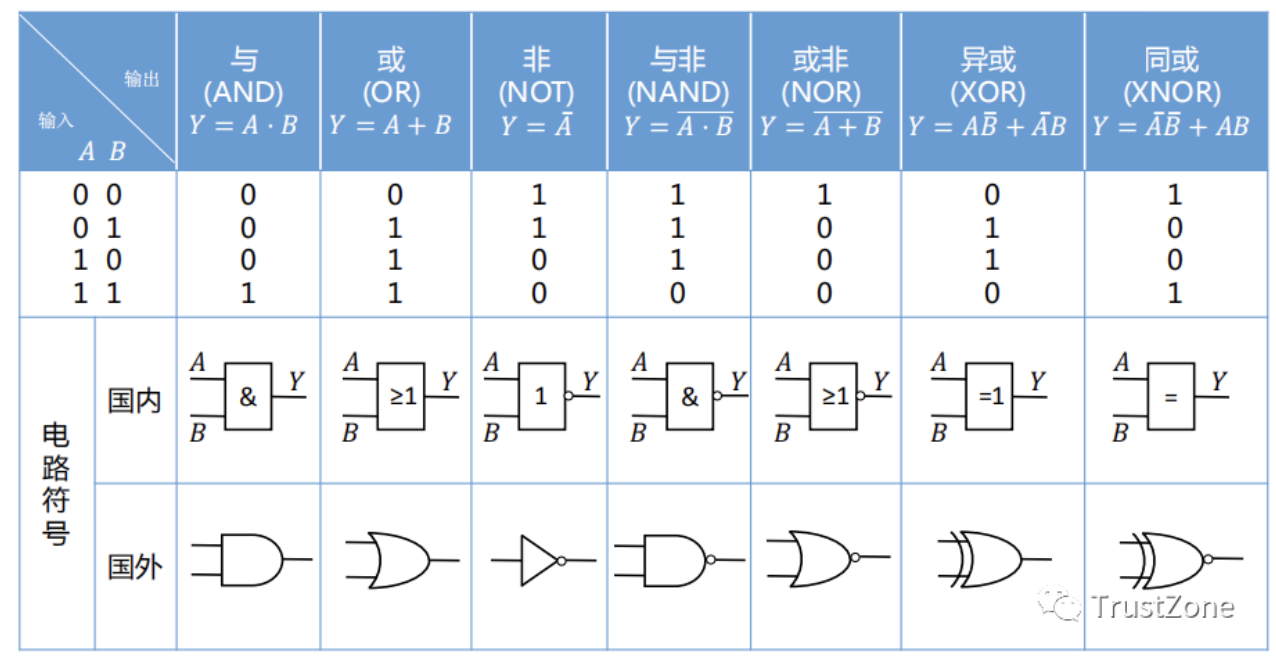

- 2、數字邏輯門:

- 3、時序電路:現代數字邏輯電路分為組合邏輯和順序邏輯(有存儲功能)

- ①時序電路元件:觸發器(鎖存器),D型、T型(反轉)、JK型

- ②計時參數:設置時間、保持時間、傳輸延遲

學習資料:數電基礎:時序邏輯電路[1]

二、ASIC 和 FPGA

為特定用途制造的集成電路,性能高、功能復雜、功率消耗低、單元較小、單位成本低,但開發周期長、設計流復雜、初始成本高、偶發成本高,在大批量生產上具有優勢

對已制造完成的芯片進行配置的集成電路, 由一組可編程的邏輯塊和可重構連接器構成,是現場可編程的 。邏輯塊可通過重新配置連接器進行連接,配置不同的功能。其靈活、上市時間快、設計簡單、可升級而不改變硬件,但功率消耗高、性能中等、單元成本高、資源浪費。在中等批量的生產上具有優勢。

還可以用來搭建原型驗證平臺。

三、印制電路板(PCB - Printed Circuit Board )

- 1、PCB的設計流程:

- 前期準備: 這包括準備元件庫和原理圖。在進行PCB設計之前,首先要準備好原理圖SCH的元件庫和PCB的元件庫。元件庫可以用peotel 自帶的庫,但一般情況下很難找到合適的,最好是自己根據所選器件的標準尺寸資料自己做元件庫。原則上先做PCB的元件庫,再做SCH的元件庫。PCB的元件庫要求較高,它直接影響板子的安裝;SCH的元件庫要求相對比較松,只要注意定義好管腳屬性和與PCB元件的對應關系就行。注意標準庫中的隱藏管腳。之后就是原理圖的設計,做好后就準備開始做PCB設計了。

- PCB結構設計: 這一步根據已經確定的電路板尺寸和各項機械定位,在PCB 設計環境下進行設計。

- PCB布局: 這主要是指在PCB板上放置元器件的位置。布線:是指根據已經設計的PCB布局,通過具體的連接方式將元器件連接起來。

- 布線優化和絲印: 主要是對已經完成的布線進行優化,比如調整走線的角度、長度等,以及添加絲印等。

- 網絡和DRC檢查和結構檢查: 這是指對已經完成的PCB設計進行網絡檢查和結構檢查,以確保其滿足設計要求。

- 制版: 是指將設計好的PCB圖紙送到工廠進行制作,制作完成后進行測試和驗收。

- 2、PCB生產流程:輪廓、創建銅線路、鉆孔、焊上元件、Gerber文件 有點意思:電路板廠之PCB制作工藝過程展示!(動圖講解)[2]

- 基材準備: 選擇合適的基材,通常是玻璃纖維增強的環氧樹脂(FR-4),進行切割和平整處理。

- 表面處理: 在基材表面進行清潔、去氧化和化學處理,以增強粘附性能。

- 涂覆銅箔: 在基材上涂覆一層銅箔,形成導電層。

- 圖形化蝕刻: 將Gerber文件的圖形信息通過光刻技術轉移到涂覆的銅箔上,并使用化學溶液蝕刻掉未受保護的部分。

- 孔位鉆孔: 根據設計需要,在板上鉆孔,形成連接電路和安裝孔位。

- 金屬化處理: 在鉆孔后,對板面進行金屬化處理,以增強電路連通性。

- 追蹤線路: 在板上涂覆保護層,并通過蝕刻或化學方法形成所需的導線路徑和連接。

- 表面處理: 根據要求,在PCB表面進行阻焊涂覆和表面處理,以保護電路和增強焊接性能。

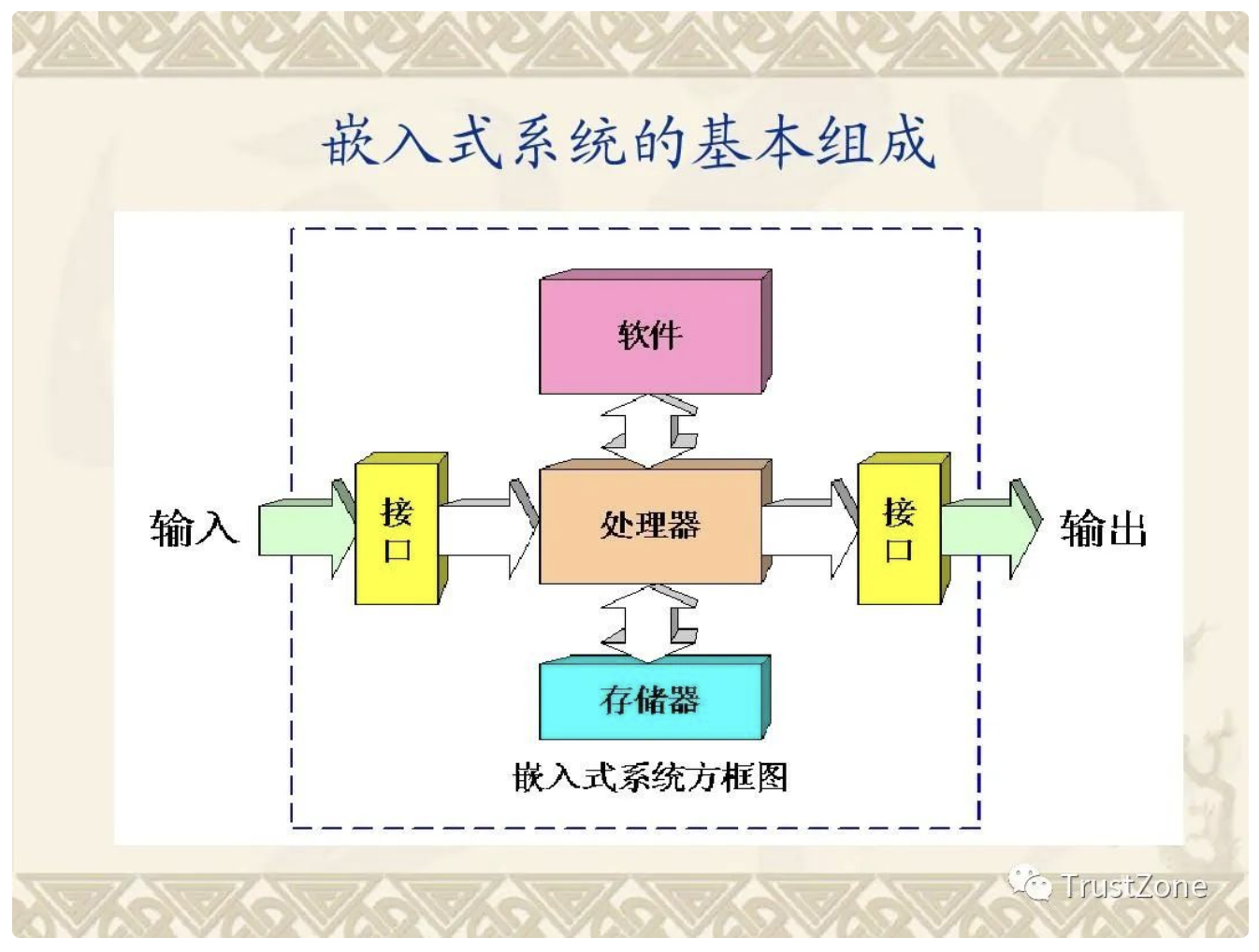

四、嵌入式系統

基于微處理器或微控制器的系統, 為特定功能而設計 。微控制器是一個整體,包括 CPU。其搭載的軟件通常需要工作在內存較少的簡單環境中。

五、硬件-固件-軟件交互

- 硬件是計算機系統的物理部分 ,包括中央處理器(CPU)、內存、硬盤、基本輸入輸出系統(BIOS)等。

- 固件負責在硬件和軟件之間建立通信 , 并管理計算機的基本功能 。它通常被存儲在只讀存儲器(ROM)或可編程只讀存儲器(PROM)中。

- 軟件是計算機系統的非物質部分,包括操作系統、編譯器和應用程序等 。操作系統負責管理計算機的資源,編譯器負責將源代碼轉換為機器代碼,而應用程序則為用戶提供特定的功能。

在硬件、固件和軟件的交互中, 固件會與硬件進行通信,將硬件的狀態和信息提供給操作系統和編譯器 。

而操作系統則會根據固件提供的信息,管理硬件資源,并向應用程序提供服務。

編譯器則將應用程序的源代碼轉換為機器代碼,以便操作系統能夠執行。

計算機固件根據所在設備的不同可以分為多種類型,最常見的有主板固件、顯卡固件、鼠標鍵盤固件等。每一種固件都具有自己獨特的功能和操作方式。

固件作為硬件的控制程序,起到了以下幾個重要作用:

- 啟動系統:固件負責電腦的啟動過程,可以加載操作系統,進行初始化設置和硬件自檢等操作。

- 管理硬件:固件可以管理電腦硬件的工作狀態,包括電源管理、溫度監控、風扇轉速控制等。

- 支持擴展設備:固件可以支持新設備的接入和識別,保證硬件的兼容性和穩定性。

- 升級與維護:固件可以進行升級和修復,提供新功能和修復已知問題,提高硬件的性能和穩定性。

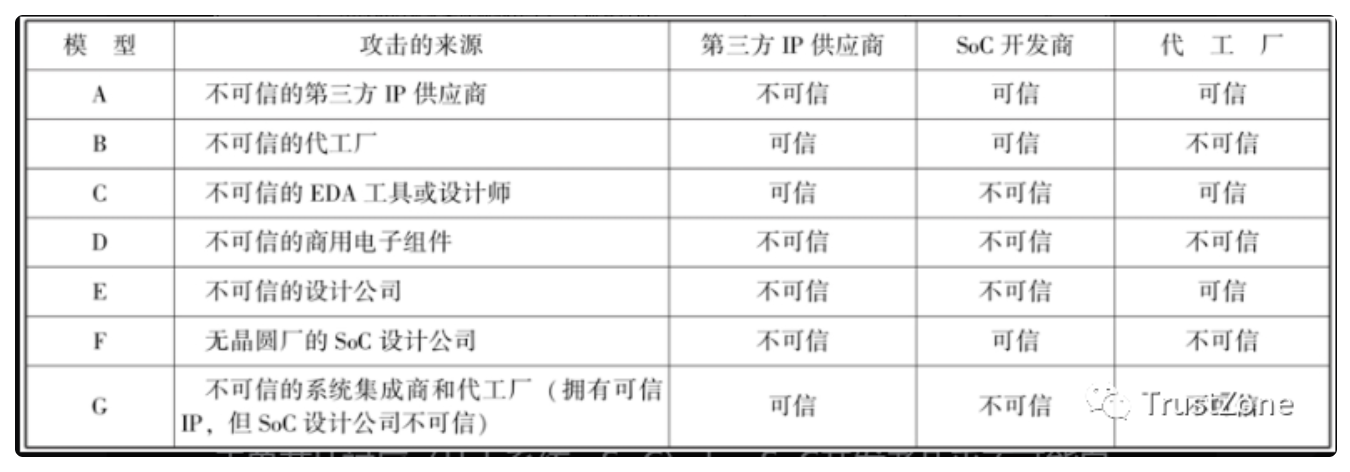

片上系統的設計與測試

本章講述 SoC 的設計流程、SoC 測試驗證的流程和原理

在設計VLSI(超大規模集成電路)時,會設定一個時序裕度,保證芯片的穩定運行。但IC上的門密度和設計復雜度在不斷增加,在納米尺度的制造工藝下將可能引入更多制造缺陷。因此, 驗證測試和制造過程的正確性變得越來越重要 。

一、基于 IP 的 SoC 生命周期

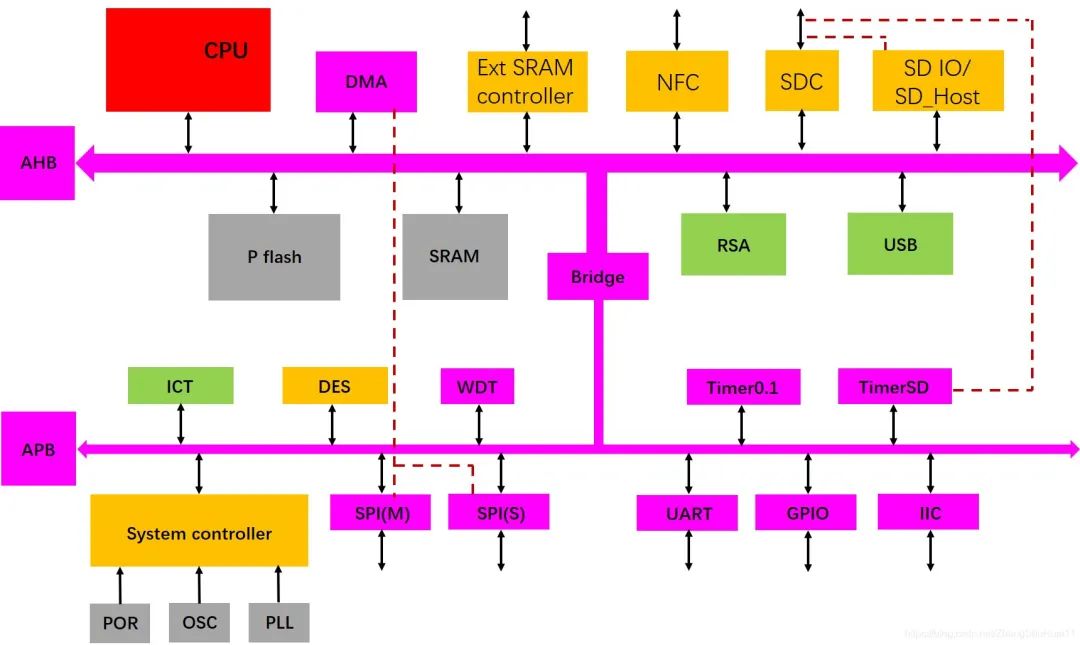

SoC(system on chip)片上系統 是一個包含給定系統所需所有元件的集成電路,通常包括模擬、數字和混合信號IP核心。

1、SoC的生命周期 :

- 設計階段: 在這個階段,制定設計規范,隨后將所有IP內核集成,并植入DFT結構,生成網表和GDSII格式文件。這個階段需要經過詳細的規劃和測試,以確保設計的正確性和性能。

- 制造階段: 在制造階段,將在晶圓片上進行光刻和化學處理,以制造出芯片。這個階段需要使用精密的設備和工藝,以生產出高質量的產品。

- 裝配階段: 即IC封裝,裝上外殼,并提供電氣連接和散熱的熱路徑,以保護芯片。這個階段需要使用先進的封裝技術,以確保芯片能夠正常工作并得到良好的保護。

- 發行階段: 在發行階段,產品將被分銷到各個銷售渠道,供消費者購買和使用。這個階段需要制定市場策略和銷售計劃,以促進產品的銷售和推廣。

- 系統集成階段: 在系統集成階段,與多個器件一同集成為一個系統。這個階段需要考慮如何將各個功能模塊集成在一起,以實現系統的完整性和穩定性。

- 退役階段: 在退役階段,產品將不再被生產和銷售,并逐漸退出市場。這個階段需要進行產品的清理和回收,以保護環境和資源。

在整個SoC的生命周期中,需要不斷地進行優化和改進,以提高產品的性能、降低成本并滿足市場需求。同時,也需要不斷地更新技術,以保持公司的競爭力和市場地位。

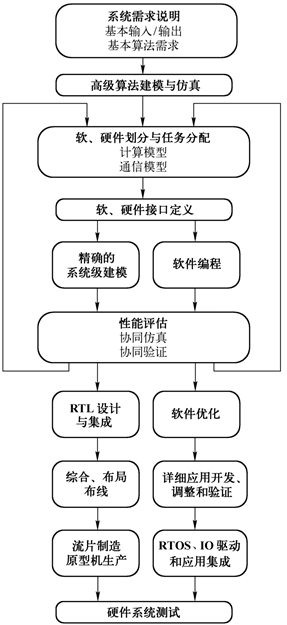

2、SoC的設計流程:

SoC 技術設計系統芯片,一般先要進行軟硬件劃分,將設計基本分為兩部分: 芯片硬件設計和軟件協同設計 。

芯片硬件設計包括:

- ①制訂設計規范,并指定一個IP列表實現既定規范。(3PIP的購買:軟IP核以HDL交付;硬IP核以GDSII交付;固定IP核使用通用庫交付。

- ②將所有IP集成,加入DFT結構,生成RTL描述(完整的系統級數字電路描述)和網表。

- ③門級網表被轉換為基于邏輯單元格和I/O幾何圖形的物理布局

- ④進行測試,測試完畢后,發往代工廠進行制造

二、SoC 的驗證測試流程

驗證階段又稱硅前驗證 ,即在流片前確保從設計規范到網表的功能正確和正確轉換的過程;

測試階段 ,是流片后的制造測試和生產測試的過程。

- IP 驗證 IP 是任何 SoC 的基本構建塊。因此,IP驗證需要詳盡的白盒驗證,這需要形式驗證和隨機模擬等方法,特別是對于處理器IP,因為一切都是由它們作為任何SoC的核心組件啟動和驅動的。下圖 顯示了我們如何通過基于 SystemVerilog 的 UVM TB 的詳盡隨機模擬來驗證處理器 IP。所有處理器指令都可以使用各種隨機值進行模擬,從而生成功能、斷言和代碼覆蓋率。我們使用覆蓋范圍來衡量驗證的進度和質量,然后進行最終的驗證簽核 IP 級驗證要求在 HVL 編程、正式和動態 ABV、仿真調試以及使用 VIP 和 EDA 工具方面具備良好的專業知識。

- ABV- 基于斷言的驗證,VIP – 驗證 IP

- UVM-通用驗證方法 UVC-UVM 驗證組件

- BFM總線功能模型VIP驗證IP RAL寄存器抽象層

- 子系統驗證 子系統主要由預驗證的IP和一些新建的IP組成,例如特定于芯片的網橋和系統控制器。圖 顯示了我們如何從子系統構建 SoC,該子系統使用 AMBA 等片上總線集成了所有必要的接口 IP、網橋和系統控制器。在這種情況下,我們更喜歡基于模擬的灰盒驗證,特別是使用驗證IP的隨機模擬。所有VIP,如AXI,AHB,APB,GPIO,UART,SPI和I2C UVC [UVM驗證組件]都將配置并與各自的接口連接。如圖所示,我們創建了其他 TB 組件,如參考模型、記分板和 UVM RAL,以使驗證環境自檢。我們在頂層執行各種VIP UVM序列,驗證數據流,并測量總線的性能。

- SoC驗證 SoC主要由預先驗證的第三方IP和一些內部IP組成。通常,我們更喜歡使用硬件仿真或模擬(simulation/emulation)技術進行黑盒驗證,以進行SoC級驗證。例如,您可能會遇到復雜的 SoC 驗證環境,如下圖 所示。SoC測試平臺[TB]將具有各種測試平臺組件,如標準UVM驗證IP[USB /藍牙/WiFi和標準接口],帶有UVM包裝器的傳統HDL TB組件[JTAG Agent],自定義UVM代理[固件代理],以及一些顯示器,以及記分牌和SystemC / C / C++功能模型。在這種情況下,您將不得不在芯片級別處理固件和UVM序列。作為驗證工程師,您需要知道如何使用標準 VIP、傳統 HDL BVM 和固件代碼實現這種混合驗證環境,更重要的是,了解如何使用 EDA 工具自動執行simulation/emulation。

深入一下:SoC Verification Flow and Methodologies[3]

1、SoC的驗證流程

- ①對 IP進行單獨驗證 。

- ② 基于接口協議 ,對芯片中各塊接口進行驗證

- ③ 系統級驗證 ,通過 仿真軟件進行硬件和軟件的驗證 。分別進行功能驗證和結構驗證。

- ④對IC的物理布局進行驗證。驗證完成。

2、SoC的測試流程

- ①晶圓測試,為晶圓提供電氣刺激進行測試

- ② 識別制造缺陷或故障 ,使用自動測試模式生成工具ATPG

- ③對芯片進行表征,找出芯片的理想工作參數

- ④功能測試和結構測試

- ⑤封裝模具的老化應力測試

三、調試性設計

SoC調試,即硅后驗證,在第一個硅制造后進行 。調試支持由 芯片上的調試性設計架構和軟件組成 。其策略是 將接入點放置在系統中 ,由它的接口獲得和控制芯片內部信號。

電子系統中有三種元件需要測試:數字邏輯、內存塊、模擬或混合信號電路。制造測試成本主要取決于測試數據的數量和測試時間

ATPG 掃描測試(又叫ATPG)。scan path。與邊界掃描測試的區別,是內部移位寄存器實現的測試數據輸入輸出。測試目標是std-logic,即標準單元庫。(掃描測試和邊界掃描,不是一個概念。需要區別對待。內部的觸發器,全部要使用帶SCAN功能的觸發器類型。)

Boundary scan Boundary scan:邊界掃描測試;boundary scan test。測試目標是IO-PAD,利用jtag接口互連以方便測試。(jtag接口,實現不同芯片之間的互連。這樣可以形成整個系統的可測試性設計。)

Lbist Lbist:LBIST 是一種內置自測 (BIST) 形式,其中芯片內部的邏輯可以在芯片本身上進行測試,而無需任何昂貴的自動測試設備 (ATE)。BIST 引擎內置于芯片內部,只需要像測試訪問端口 (TAP) 這樣的訪問機制即可啟動。Lbist的組成部分 片上lbist一般由三部分組成:BIST controller、TPG (Test Pattern Generator)、RA (Response Analyzer)。

mbist mbist:內建自測試BIST;(模擬IP的關鍵功能,可以開發BIST設計。一般情況,BIST造成系統復雜度大大增加。memory IP一般自帶BIST,簡稱MBIST)

loading board loading board:LOAD BOARD通常用于測試半導體器件的電氣特性,例如電流、電壓、功率等。它是連接測試設備和被測試芯片的橋梁,通常包括一些接口,例如引腳插座、測試點和電源接口等。LOAD BOARD的設計必須與被測試器件的引腳布局相匹配,以確保測試結果的準確性和可重復性。

BURN IN BOARD BURN IN BOARD則用于加速半導體器件的老化過程,以檢測器件在長期使用中的可靠性。它通常包括一個溫度控制系統,用于控制被測試器件的環境溫度。BURN IN BOARD還可以模擬真實世界的使用條件,例如高溫、低溫、高壓和高濕等。因此,LOAD BOARD和BURN IN BOARD的主要區別在于它們的用途。LOAD BOARD主要用于測試器件的電氣特性,而BURN IN BOARD則用于測試器件在長期使用中的可靠性。

1、DFT調試技術概覽

- ①掃描:對所有在掃描設計中的存儲元件進行訪問和控制。

- ②掃描觸發器(SFF):性能開銷低,但速度慢

- ③掃描鏈:將掃描觸發器連成一串,然后將掃描值與SO值(掃描輸出值)進行比較

- ④掃描測試壓縮:利用少量的測試的重要值來減少測試數據和測試時間

- ⑤邊界掃描:邊界掃描技術利用邊界掃描鏈,在芯片內部的信號線上插入測試信號,從而實現對芯片內部電路的測試和診斷。有效降低了PCB制造成本。

2、全速延遲測試

用于檢測計時相關故障的方法

- ①故障類型:轉換故障(慢升和慢降造成的延遲),路徑延遲故障(路徑上的累計延遲)

- ②兩種方法:LOS和LOC

印制電路板 :設計與測試

本章講述 PCB 的歷史、生命周期、設計驗證、裝配流程

印制電路板PCB是基于基地結構的非導電板,為電路電氣元件提供電氣連接和機械支撐。

一、PCB 的歷史

在PCB量產前,通常使用點對點的飛線連接;

早期PCB是在電路板材料上鉆孔,并在孔中植入黃銅。

20世紀20年代,PCB誕生,申請了第一個專利;

20世紀30年代到40年代,PCB在二戰中得到廣泛運用;

20世紀50年代,發明了酸刻蝕銅金屬電路板的方法;

20世紀80年代,表面貼裝技術(Surface Mount Technology,SMT)的發展在1980年代引入了新的PCB制造和組裝方法;

現代,三維PCB、柔性PCB。

二、PCB 的生命周期

PCB的生命周期與SoC的生命周期類似

設計規范->PCB設計->PCB原理圖->PCB布局->制造和裝配->檢測驗證

三、PCB 的設計驗證

惡意攻擊者可以利用當今復炸而高度集成的PCB設計, 借助隱藏孔或無源嵌入式元件 ,以 硬件木馬的形式篡改或植入額外的惡意電路 ,目前行業并無有效的安全措施來防御。

1、PCB檢查

- ①自動光學檢查(AOI):多次拍照,拼接成一個完整的大圖像,與設計圖進行比對。

- ②自動X射線檢查:利用不同材料對X射線的吸收率不同,對PCB進行檢查

2、PCB測試

- ①芯片內測試:萬用表原理

- ②功能測試

- ③JTAG邊界掃描測試

小結

到這里我們就對電子硬件、片上系統、PCB都有了一定認識。學習硬件安全的前提是我們得了解硬件,了解它的設計、測試、生產,才能指導在哪里會面臨安全風險,以及才有什么樣的手段去增加硬件的安全性。

-

PCB板

+關注

關注

27文章

1449瀏覽量

51742 -

二進制

+關注

關注

2文章

795瀏覽量

41686 -

時序電路

+關注

關注

1文章

114瀏覽量

21720 -

場效應晶體管

+關注

關注

6文章

364瀏覽量

19538 -

SoC系統

+關注

關注

0文章

52瀏覽量

10699

發布評論請先 登錄

相關推薦

SOC設計從Spec到流片:一窺全流程

【Soc級系統防御】Soc硬件木馬與電子鏈學習

SOC設計與驗證流程是什么?

SoC芯片的開發流程有哪幾個階段

使用Arm DesignStart處理器核搭建SoC流程

用于SoC驗證的(UVM)開源參考流程使EDA360的SoC

SoC設計流程

【Soc級系統防御】Soc全流程電子硬件概述

【Soc級系統防御】Soc全流程電子硬件概述

評論