一、概述

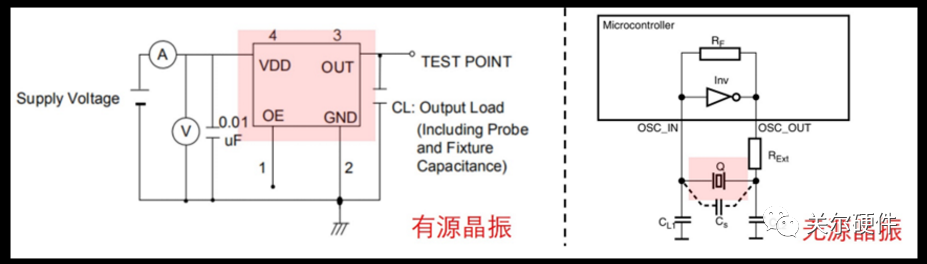

晶振是有源晶振的簡稱,又叫振蕩器。英文名稱是oscillator。

晶體則是無源晶振的簡稱,也叫諧振器。英文名稱是crystal,電路上簡稱為XTAL。

有源晶振(晶振):內部有時鐘電路,只需供電便可產生振蕩信號。

有源晶振內部是包含了一個無源晶振,然后再將阻容、放大等電路也包含進去。

晶體單元的特性取決于切割工藝,不同的切割方式決定了晶振的性能或參數,主要有三種:

音叉型(Turning Fork):頻率主要是KHz級,比如32.768KHz;

AT-Cut型:頻率主要是MHz,比如12MHz、26MHz、125MHz;

SAW型:頻率為百MHz、甚至GHz。

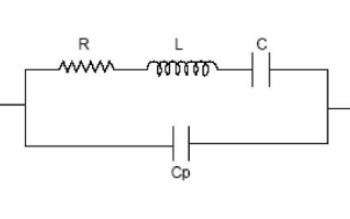

石英晶振結構圖:

晶體振蕩原理是壓電效應:

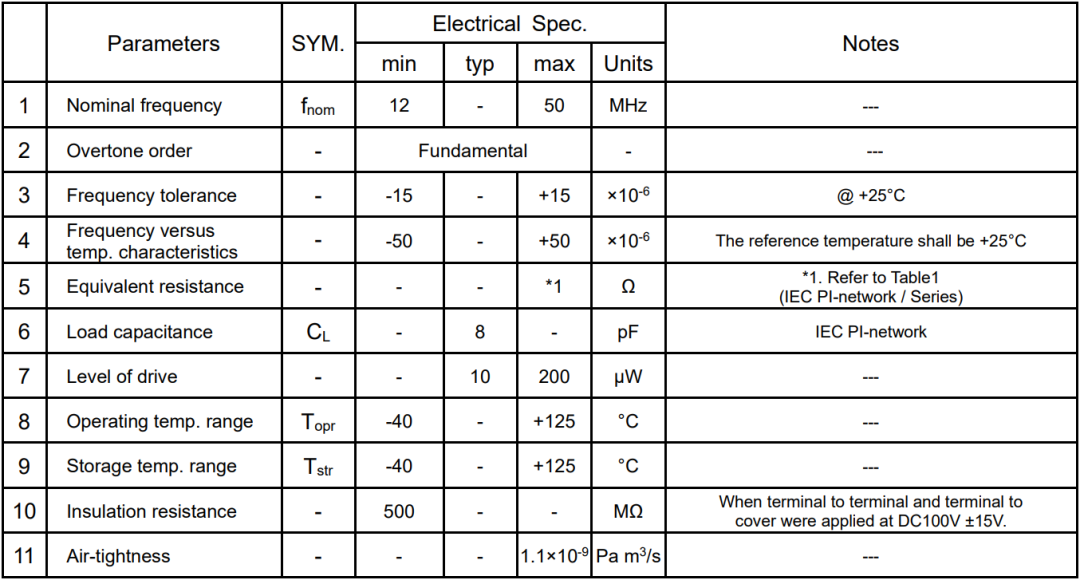

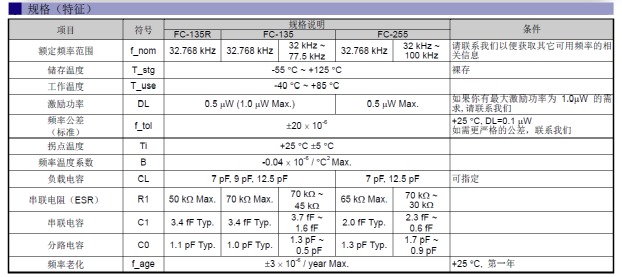

二、參數

標稱頻率(Normal Frequency) F0:電路設計上所需的實際頻率。

振動模式(Mode of Oscillation):按照切割工藝來劃分的。

負載電容(Load Capacitance)CL:在電路中跨接晶振兩端總的外界有效電容;要等于或接近晶振數據手冊給出的數值才能使晶振按照預期工作;比較通常使用的24MHz晶振負載電容是20pF;

靜態電容C0:以石英晶片為介電材料和兩個電極之間的電容;很多晶振規格里是<3pF的;

等效電阻:晶體上的等效ESR。

調整頻偏(Frequency Tolerance):在確定的負載電容下,振蕩頻率的偏差。

頻偏:常溫頻偏+溫度頻偏<芯片要求頻偏。

溫度頻偏(Temperature Tolerance):高溫時所帶來的頻率偏差。通常有溫度要求的,要選用10ppm。

激勵功率:振蕩需要的功率。主控端的輸出激勵功率不能太大,正常會串電阻,防止給到晶體的激勵功率偏大,造成晶體的損壞。

老化率:隨著使用時間,頻偏會加大。

三、設計電路

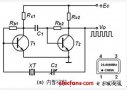

Xin和Xout的內部一般是一個施密特反相器,反相器是不能驅動晶體震蕩的。因此,在反相器的兩端并聯一個電阻,由電阻完成將輸出的信號反向180度反饋到輸入端形成負反饋,構成負反饋放大電路。

Rf:反饋電阻(主控端內置或外接);

Rd:限流電阻(預防晶振過驅,限制振蕩幅度);

Cg和Cd:負載電容;

電路中負載電容計算法:

CL=Cg*Cd/(Cg+Cd)+CPAR

Cg、Cd:負載電容;

CPAR:電路布線雜散電容及引腳寄生電容(2pF---9pF)。

輸出頻率F與寄生電容是反比的:

當電路中心頻率偏大時,說明負載電容CL偏小,增加Cg、Cd容值。

當電路中心頻率偏小時,說明負載電容CL偏大,減小Cg、Cd容值。

四、負阻

4.1 負電阻

英文:Negative Resistance

英文簡稱:– R

單位符號:Ω

負電阻不是晶振的內置參數, 但卻是振蕩線路設計時,很重要的性能指標。

是電路放大器(AMP)注入能量的大小用電阻來表示(是提供功率的器件,相當于激勵源)。

是保證振蕩器穩定振蕩并具有一定余量的重要指標。

是用阻抗表示的振蕩電路信號放大能力。

4.2 等效電路

在石英晶體振蕩狀態下,從石英振蕩體的兩端看振蕩回路時,能以等值輸入電容Ci和等值輸入電阻-Ri的串聯回路來表示,而石英晶體本身則成為等值的有效電感LL和有效電阻RR的串聯回路。

4.3 測試負阻方法:

量測負性阻抗:輸出端串接一個可變電阻,可變電阻調至最小,上電源讓電路正常動作,調整可變電阻,將之調大,直至振蕩器不起振,確定不起振后,再將可變電阻轉小,觀測波形,持續將可變電阻調小到振蕩器開始振蕩波形正常后,關閉電源,再打開電源,若振蕩器依舊可以起振,這時候可變電阻上的阻抗值再加上儀器所測得振蕩器單體的電阻值即為負性阻抗值。

若要獲得穩定的振蕩電路,振蕩電路IC的負電阻值(-R)至少為晶振的5倍以上,即絕對值|-R|>5R。舉例來說:如果晶振電路阻抗總值為30Ω,那么IC的負電阻值需要至少在-150Ω,這樣才能有效保障振蕩回路的穩定性。

若負性阻抗的能量源大于振蕩電路的損耗時,能源回路為平衡狀態,此回路為穩定振蕩,負性阻抗不是產品規格參數,但卻是振蕩線路設計時很重要的性能指針。

負性電阻振蕩器模型:

振蕩器描述為負性電阻 (Rn)、電路電抗 (Xc)、諧振器電抗 (XR) 和諧振器電阻 (RR) 的組合。當Rn>RR時,電路將以使Xc=-XR的頻率振蕩。

4.4 負阻調整

調整負載電容CL大小;

選用內阻較小的晶振;

修改電路上的其他參數,增大電路負性阻抗;

五、激勵功率計算及測試

有兩種辦法可以用來計算晶振的激勵功率:

5.1 通過電流計算

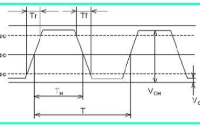

DL = ESR x (IQ)^2, IQ表示通過晶振電流的有效值, 通過示波器如下測量電流 ,如果過大的話, 則需要增加Rext電阻進行限流, 測量電流的話,晶振引腳空間小,不好操作。

5.2 通過電壓計算

電流IQ(RMS) = 2 π F x VRMS x Ctot,因此,可以通過電壓來計算激勵功率。通過示波器測量晶振引腳的Vpp電壓,及相應示波器探頭的電容Cprobe, 晶振的外部負載電容CL1。

計算公式如下:

六、晶體Layout

6.1 不能放置在板邊

如下圖所示,如果產品的晶體置于板邊,DUT產品的高速器件就會與實驗臺的參考接地板形成一定的電場,且寄生電容的存在,出現共模輻射,寄生電容越大,共模輻射也就越強。

下圖左邊的電場被板子隔開,不會產生很強的輻射。

雖然晶體是輻射源頭,但是晶體影響的是近場輻射,造成EMC測試的遠場輻射的直接原因是電纜或產品中最大尺寸與輻射頻率波長可比擬的導體。

6.2 鄰層挖空處理

主要有兩方面原因:

a)鄰近晶體的銅皮會與晶體之間,形成電容器,即寄生電容,影響到晶體的負載電容計算。當然,只要實際測試晶體頻偏沒有問題,這個寄生電容不影響到可靠性。

b)鄰近晶體的銅皮會產生熱,熱會影響到晶體的頻偏(溫度頻偏)。在手機電路設計方面,會在晶體正下方挖空兩層,起到隔熱傳遞。

七、案例

7.1、高溫導致頻偏大;

WIFI模組的尺寸比較小,發送數據過程中,功率比較大,WIFI模組上的溫度就比較高,就會導致WIFI模組上40MHz無源晶振頻率偏差變大。這種情況下,只能更換溫度偏差10ppm的物料。

另,WIFI的頻偏要求比較高,正常要選用頻率偏差10ppm的。

7.2、負阻電阻過小,導致概率開機有問題

某機器在可靠性開關機測試時,小概率的1%左右開不起來的現象。熱風槍加熱測試,不開機概率增加,負性阻抗是120歐姆,而晶體的內阻是50歐姆,也就是負性阻抗偏小,晶體振蕩不穩定。設計電路上的Rd改為100歐姆,測試的負性阻抗由250歐姆,重新老化開關機測試,測試OK。

7.3、輻射超標

某個產品在做EMC測試時,160MHz出現超標,是板子上16MHz晶體的倍頻。從板子上,16MHz晶體放置在PCB板上邊緣。解決方案:a)16MHz晶體往板子里面移動;b)在晶體四周做guard ring,起法拉第電籠作用。

(法拉第電籠:由金屬或良導體形成的籠子。可防止電磁場進入或逃脫籠子。原理:根據接地導體靜電平衡的條件,籠體是一個等位體,內部電勢差為零,電場為零,電荷分布在籠體的表面。)

-

振蕩器

+關注

關注

28文章

3918瀏覽量

139971 -

有源晶振

+關注

關注

1文章

913瀏覽量

21046 -

無源晶振

+關注

關注

1文章

845瀏覽量

16386 -

晶振

+關注

關注

34文章

3085瀏覽量

69043

發布評論請先 登錄

相關推薦

評論