晶體管尺寸在3nm時達到臨界點,納米片FET可能會取代finFET來滿足性能、功耗、面積和成本目標。同樣,正在評估2nm銅互連的重大架構變化,此舉將重新配置向晶體管傳輸電力的方式。

芯片制造商也可能會在2nm節點開始用釕或鉬在一定程度上取代銅。其他更溫和的變化將使用低電阻通孔工藝、替代襯墊和完全對齊的通孔方法來擴展銅鑲嵌互連。

通孔優化

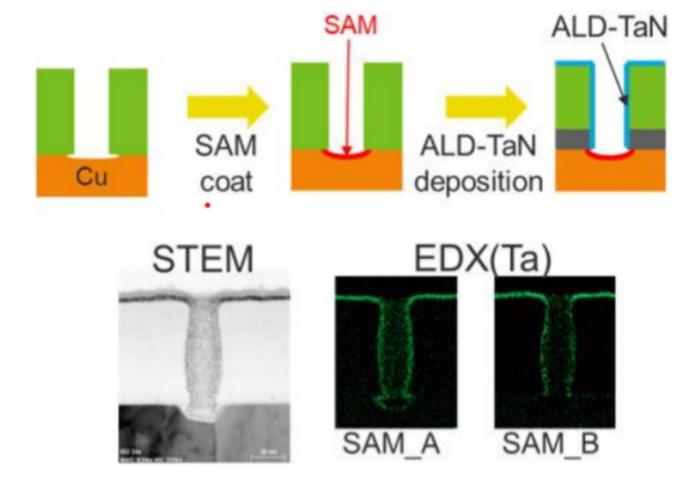

擴展銅技術的一個關鍵策略是消除銅通孔底部的阻擋金屬TaN。實現這一目標的一種方法是選擇性沉積自組裝單層(SAM)薄膜,通過原子層沉積來沉積TaN(ALD)沿側壁,去除 SAM并填充銅。在TaN阻擋層ALD之后,蒸發SAM,然后在通孔中進行銅化學沉積(ELD)(圖 1)。預填充通孔后,通過CVD在溝槽側壁上沉積釕襯墊,然后進行銅離子化PVD填充。

另一種減少通孔底部阻擋金屬(TaN)體積的策略涉及從PVD TaN到ALD TaN的過渡,這種過渡更加保形,并產生更薄、更連續的薄膜。ALD TaN 預計將在5nm節點上廣泛實施,或許采用SAM工藝。

圖1

圖1

完全對準通孔,選擇性沉積

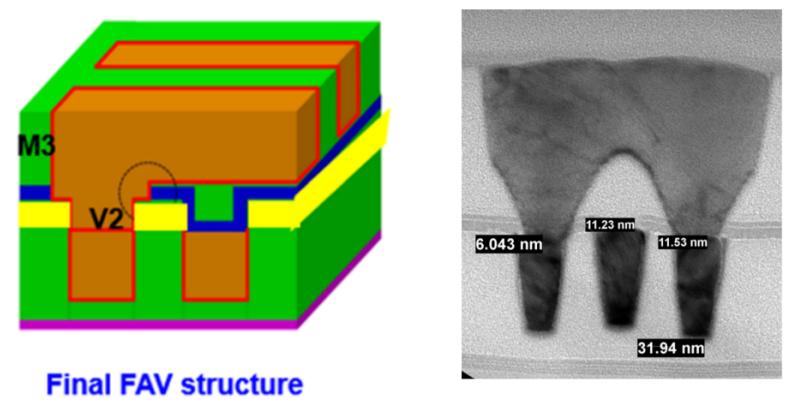

完全對準通孔(FAV)背后的想法是減少通孔和線路之間邊緣放置錯誤的影響,這些錯誤會導致器件故障和長期可靠性問題。自32nm節點以來,一直采用自對準方法,使用TiN硬掩模將互連對齊到以下水平。在完全對齊的通孔中,下方和上方的通孔被注冊。有兩種方法可以實現 FAV:從下面的線路蝕刻一些銅,然后圖案化并沉積通孔,或者通過在低 k 電介質上選擇性地沉積電介質薄膜,然后進行通孔圖案化。

凹槽蝕刻與蝕刻選擇性介電蓋結合使用時,可充當通孔引導圖案,從而減輕覆蓋和臨界尺寸(CD)引起的邊緣放置錯誤。通過CVD在低k材料上沉積選擇性氧化鋁薄膜,并充當部分蝕刻停止層。該工藝成功的關鍵是高選擇性,介電薄膜的橫向過度生長有限,并且與標準FAV工藝相比,電阻沒有降低或變化。

圖2

圖2

埋置電源軌

BPR和背面配電(BPD)的組合本質上采用電源線和地線,這些線之前是通過整個多層金屬互連布線的,并在晶圓背面為它們提供了專用網絡。通過將電源布線到背面,那里將會有很高、相對較寬的互連,而前面的信號和時鐘則帶有相對較細的電阻線,并且可以顯著獲得布線能力。

雖然這種在晶圓正面和背面建立晶體管接入的轉變將需要許多工藝和設計創新,但背面電源仍將采用平面逐層結構這一事實建立在現有行業技術的基礎上。

從晶圓減薄的角度來看,HBM存儲器的多芯片堆疊和現在邏輯的背面供電都推動晶圓減薄至10微米,但人們對變薄有著巨大的興趣。高密度堆疊正在推動這一需求,設計人員想要比目前可用的硅更薄的硅。從需要某些東西的那一刻起,技術人員就會擴展功能,這就是芯片堆疊所發生的情況。

結論

目前,正在評估5nm及以上工藝的許多工藝變化,包括通孔電阻優化、完全對齊的通孔、鈷帽和觸點,以及電源線和信號線的分離以釋放擁擠的互連層。半導體行業總是更愿意盡可能地進行漸進的工藝修改,而不是大規模的材料和結構變化。

新的襯墊可以提高可靠性,消除通孔底部的障礙并完全對齊通孔,似乎正在提供解決方案。選擇性沉積已進入鈷帽工廠,并且可能會在未來的其他應用中獲得接受。

-

半導體

+關注

關注

334文章

27537瀏覽量

220077 -

晶圓

+關注

關注

52文章

4936瀏覽量

128123 -

蝕刻工藝

+關注

關注

3文章

51瀏覽量

11753 -

硅半導體

+關注

關注

0文章

31瀏覽量

7374

發布評論請先 登錄

相關推薦

將銅互連擴展到2nm的研究

將銅互連擴展到2nm的研究

評論