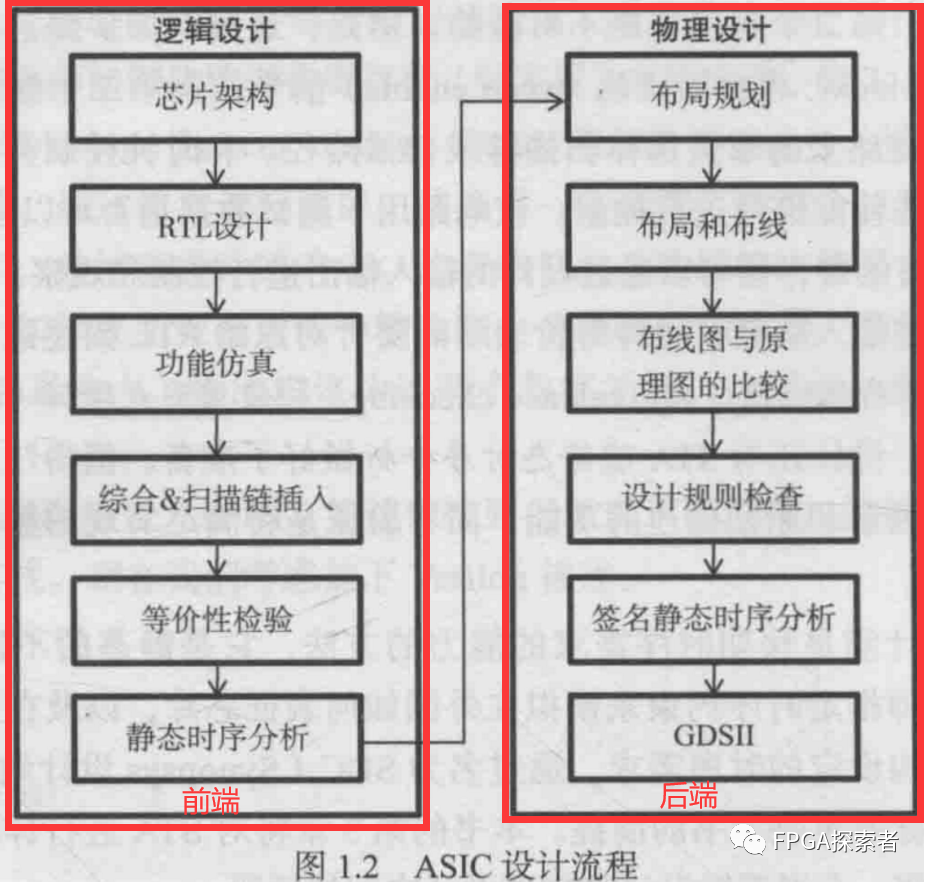

一、IC 前端設計流程(RTL to Gate-Netlist)

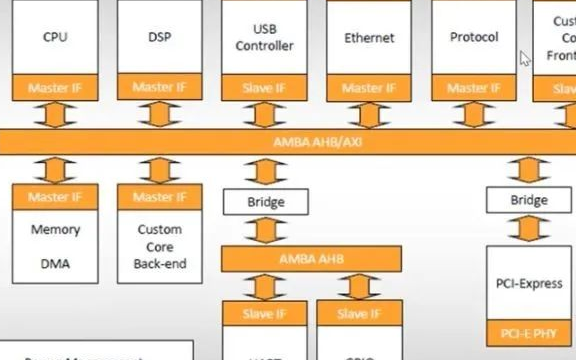

1、 芯片架構 :考慮芯片定義。

2、 RTL 設計 :芯片功能設計。硬件描述語言如 Verilog、VHDL、SystemVerilog。

3、 功能仿真 :驗證芯片功能設計的正確性。EDA 工具如 Synopsys 的 VCS、Cadence 的 NC-Verilog、Mentor 的 ModelSim。

4、 邏輯綜合 :將 RTL 轉換成門級網表 Gate Netlist;邏輯綜合要指定基于的庫、工藝,設定約束條件。綜合之前的仿真為前仿真,綜合之后的仿真為后仿真,所以這里還需要一個后仿真。EDA 工具如 Synopsys 的 Design Compiler、Cadence 的 Genus。

5、 靜態時序分析(STA) :檢查建立時間(Setup)和保持時間(Hold)是否違例(Violation)。EDA 工具如 Synopsys 的 PrimeTime。

6、 形式驗證 :在功能上,對綜合后的網表進行驗證。通過等價性檢查(Equivalence Check)方法,以功能驗證后的 HDL 設計為參考,對照綜合后的網表功能,檢查是否在功能上存在等價性,從而保證在邏輯綜合過程中沒有改變原先 HDL 描述的電路功能。EDA 工具如 Synopsys 的 Formality、Cadence 的 Conformal。

二、IC 后端設計流程(Gate-Netlist to GDSII)

作為 IC 設計的后端納米工藝 VLSI 物理設計與實現流程詳解文檔,包括了 Cadence Genus 綜合技術,物理設計與實現流程,RTL - to - GDSII 流程,讓你了解庫文件(網表庫、時序庫、物理庫)、RTL 文件、時序約束文件、綜合、平面布局規劃(芯片大小、IO、電源規劃、宏單元、布線光暈、擺放塊等等)、擺放、布線(實驗布線、特殊布線、真實布線)、時鐘樹綜合(預時鐘樹和后時鐘樹綜合)、時序分析、時序修正、電源分析、信號完整性分析、金屬填充、物理驗證、代工廠 Tapeout 等等。

0、 綜合 Synthesis :將硬件描述語言轉化成門級網表,即 RTL - to - Netlist。(這里隸屬于前端,所以,以 0 表示)EDA 工具為 Cadence 的 Genus,輸入文件為 .V + .LIB + .SDC(RTL 設計文件、工藝庫文件、時序約束文件)。

1、 設計輸入 Design Import :輸入文件為網表庫(.V)+ 時序庫(.LIB)+ 物理庫(.LEF)+ 時序約束文件(.SDC)+ IO 文件(.IO)+ 可選文件如規劃布局文件(.FP)、工藝文件(.QRC)、版圖文件(.GDS)、時鐘樹規范文件(.SPEC)、掃描鏈信息等等。

2、 平面布局規劃 Floorplan :包括芯片大小(Die Size)的規劃、I/O Pad 規劃、宏單元(Macro)以及大量硬核或模塊(Hard Cores、Hard Blocks)的規劃等等,是對芯片內部結構的完整規劃和設計。其中,電源規劃是給整個芯片的供電設計規劃出一個均勻的網絡。Power Ring(電源環)指為了均勻供電,包圍在芯片周圍的環形供電金屬,實現穩定供壓的作用;Power Strips(電源條)指芯片內部縱橫交錯的 Power Grids(電源網格),主要是防止 IR Drop(電壓降),也就是電路中有過高的壓降會導致器件運行速度很慢;

3、 掃描鏈定義 Scan Chain :掃描鏈(Scan chain)是可測試性設計(DFT)的一種實現技術;它通過植入移位寄存器(Shift Register),使得測試人員可以從外部控制和觀測電路內部觸發器的信號值,從而使得設計具有可控性和可觀察性。

4、 擺放 Placement :平面布局規劃后,宏單元、I/O Pad 的位置和放置標準單元的區域都已確定,Placement 是將設計中的所有標準單元和塊擺放到 Floorplan 的設計中;

5、 時鐘樹綜合 Clock Tree Synthesis :通過插入緩沖器 Buffer 減小負載和平衡延時(主要是針對時鐘偏差,能夠消除 Clock Skew),時鐘網絡及其上一級一級的緩沖單元構成了時鐘樹;

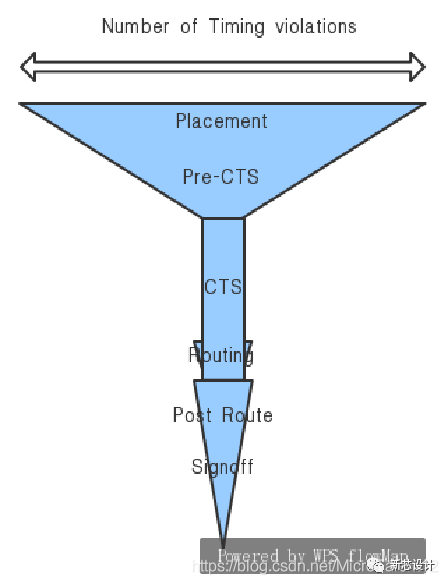

6、 靜態時序分析 STA Static Timing Analysis :時鐘樹插入之后,每一個單元的位置都確定下來了,工具可以提出 Global Route 形式的連線寄生參數,此時對延時參數的提取就比較準確了;然后通過 EDA 工具指定提取模式如 RC 提取模式、指定延時計算模式等等來進行建立時間與保持時間分析;如果發生時序違例,那么則返回上一層設計,通過修改設計等等使其滿足時序要求,從而達到時序收斂。通常,時序違例在不同的階段有著不同的數目,如下所示:

時序違例在不同的階段的不同數目

7、 布線 Routing :指的是在滿足工藝規則和布線層數限制、線寬、線間距限制和各線網可靠絕緣的電性能約束的條件下,根據電路的連接關系將各單元和 IO Pad 用互連線 Interconnect 連接起來;通俗地講,就是將 Placement 擺放后的模塊連接起來。Trial Route,實驗布線,是一種快速的全局布線。Special Route,特殊布線,簡稱 SRoute,連接 Power Structure 的 Router。NanoRoute,真實布線,是一種 Smart Routing,大致分為 Global Route(全局走線)和 Detail Route(詳細走線)。PR 的 EDA 工具如 Synopsys 的 IC Compiler、Cadence 的 SoC Encounter 和 Innovus。

8、 信號完整性 SI Signal Integrity :指的是分析信號在傳輸路徑上的質量。信號完整性主要表現在延遲、反射、串擾、時序、振蕩等幾個方面。

9、 金屬填充 Metal Fill :指的是在設計中添加金屬線形狀以滿足 Foundary 廠金屬密度規則的過程,如 Dummy Metal。另外,還有 Filler 的插入,如 Pad Filler 和 Cell Filler;Filler 指的是標準單元庫和 I/O Pad 庫中定義的與邏輯無關的填充物,用來填充標準單元和標準單元之間、I/O Pad 和 I/O Pad 之間的間隙。

10、 物理驗證 Physical Verification :主要有連線 Connectivity、金屬密度 Metal Density、幾何形狀 Geometry、過程天線 Process Antenna 等一些驗證要素。DRC(Design Rules Check)是對芯片版圖中的各層物理圖形進行設計規則檢查;LVS(Layout VS Schematic)是為了檢查版圖文件功能與原有電路設計功能的一致性,從而將版圖與網表進行比較。

11、 流片 Signoff :指的是成功完成 IC 設計的所有檢查和驗證的一個標志。

-

緩沖器

+關注

關注

6文章

1924瀏覽量

45580 -

IC設計

+關注

關注

38文章

1299瀏覽量

104175 -

EDA工具

+關注

關注

4文章

268瀏覽量

31878 -

RTL

+關注

關注

1文章

385瀏覽量

59896 -

靜態時序分析

+關注

關注

0文章

28瀏覽量

9601

發布評論請先 登錄

相關推薦

【「數字IC設計入門」閱讀體驗】+ 數字IC設計流程

IC前端和后端設計的區別

數字IC后端(CAD)

數字IC后端設計介紹,寫給哪些想轉IC后端的人!

IC前端設計(邏輯設計)和后端設計(物理設計)的詳細解析

數字IC前端設計+后端設計流程實現

數字IC前端設計+后端設計流程實現

評論