建立時間,保持時間

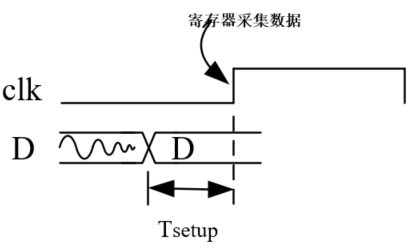

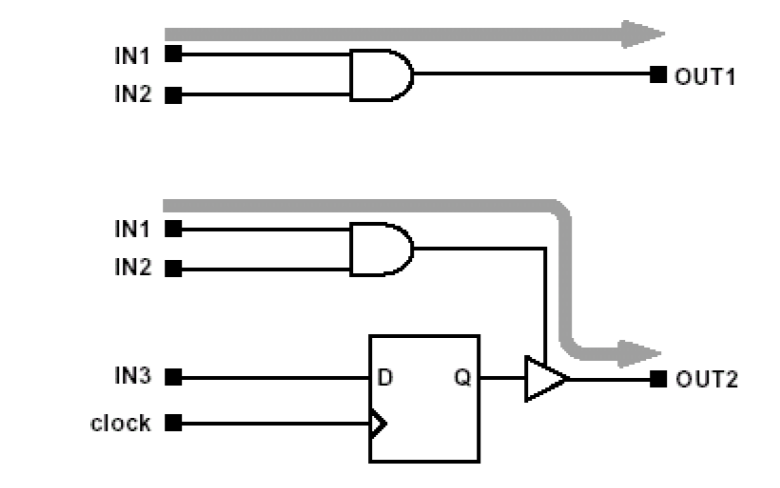

為了確保寄存器在時鐘沿穩定采集數據,那么必須要滿足寄存器的建立,保持時間要求。 建立時間要求:在寄存器有效時鐘沿之前至少Tsetup時間,數據必須到達且穩定。如下圖所示。

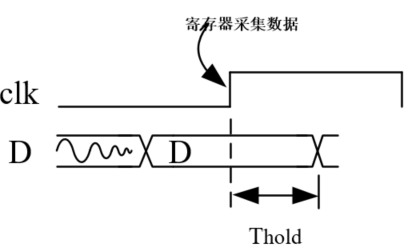

保持時間要求:在數據采集有效時鐘沿之后,數據必須維持最短Thold時間不變。如下圖所示。

建立時間裕量計算

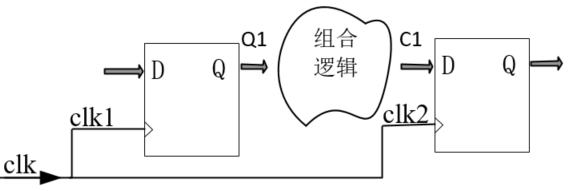

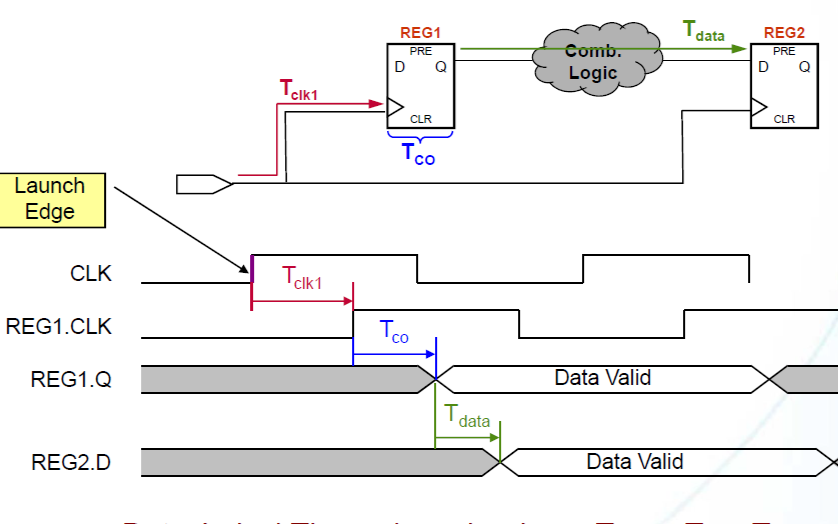

同步時序電路如下圖所示。這里對后面一個寄存器進行建立時間裕量分析。

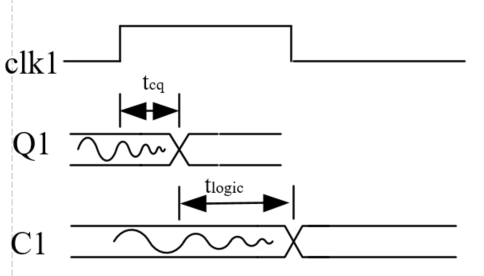

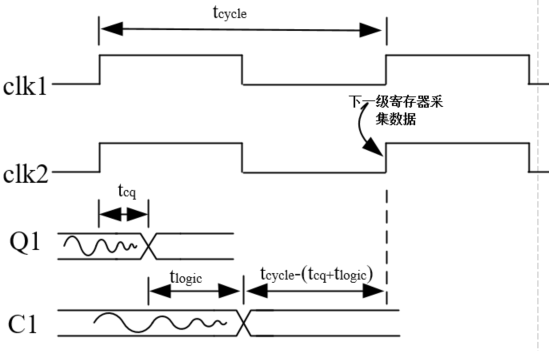

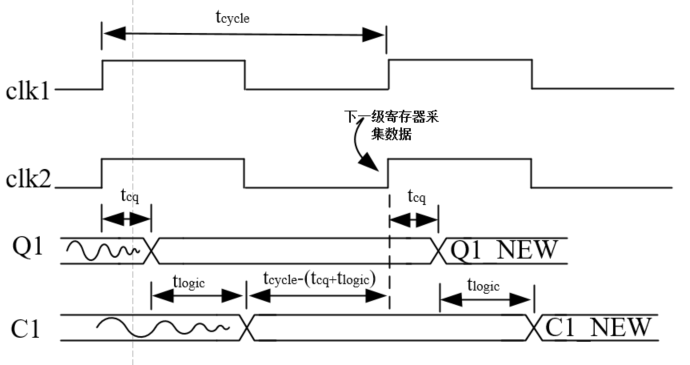

其中寄存器的輸出延時為Tcq,即時鐘有效沿之后延時Tcq時間,數據才到達寄存器Q端。第一個寄存器有效時鐘沿之后Tcq時間,數據才到達Q1端,如下圖所示。 再經過組合邏輯運算,得到數據C1,其中組合邏輯的延時為Tlogic。時序如下圖。

從這里可以看到,如果clk2和clk1之間沒有延時。那么對于后面的寄存器而言,數據提前于采樣時鐘沿之前Tcycle-(Tcq+Tlogic)時間到來,且穩定。其中Tcycle為時鐘周期。

由于寄存器要求的建立時間為Tsetup,故電路必須滿足 Tcycle -(Tcq+Tlogic)- Tsetup>0 。建立時間裕量 Tset_slack = Tcycle -(Tcq+Tlogic)- Tsetup

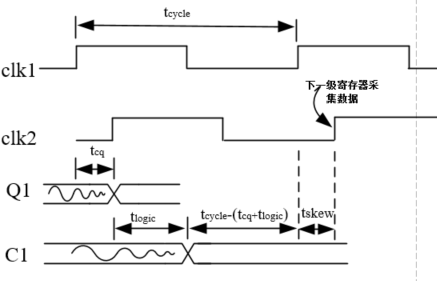

如果clk1與clk2之間存在skew,如下圖所示,如正skew。得建立時間裕量為

Tset_slack =Tcycle -(Tcq+Tlogic)- Tsetup + Tskew

這是對建立時間有益的。

保持時間裕量計算

在時鐘沒有skew的情況下。在后一個寄存器有效采樣時鐘沿之后,同時新的C1只有經過Tcq+Tlogic之后才會到達。故要滿足保持時間要求,只需要滿足Tcq+Tlogic>Thold。保持時間裕量Thold_slack = Tcq+Tlogic-Thold

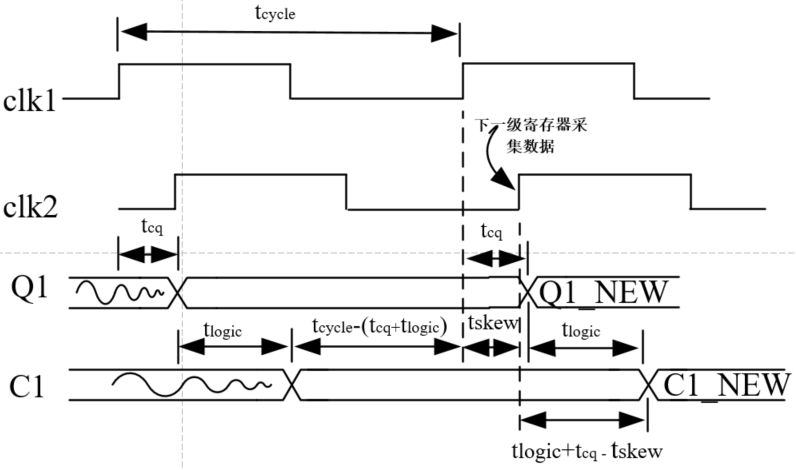

如果clk1與clk2之間存在skew。如下圖所示(正skew)。

可以看到,C1_NEW在clk2時鐘沿后,Tlogic+Tcq-Tskew就改變了。此時保持時間裕量Thold_slack = Tcq+Tlogic-Thold - Tskew 。可以看到,正skew對保持時間是無益的。

總結

可以看到,必須滿足建立時間要求和保持時間要求,即滿足如下關系式。 Tset_slack =Tcycle -(Tcq+Tlogic)- Tsetup +Tskew>0 Thold_slack =Tcq+Tlogic-Thold - Tskew > 0 從中可以看出,建立時間與保持時間要求是一對矛盾的關系,在設計電路時,我們要折中考慮。

審核編輯:湯梓紅

-

寄存器

+關注

關注

31文章

5389瀏覽量

121812 -

時鐘

+關注

關注

11文章

1756瀏覽量

132137 -

靜態時序分析

+關注

關注

0文章

29瀏覽量

9617 -

保持時間

+關注

關注

0文章

10瀏覽量

5719

原文標題:靜態時序分析基礎

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

[求助]靜態時序分析與時序仿真?

靜態時序分析基礎知識

靜態時序分析基礎知識

靜態時序分析基礎知識

評論