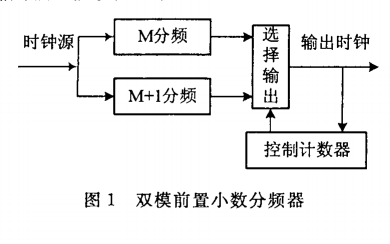

**1 **分頻器結(jié)構(gòu)及原理

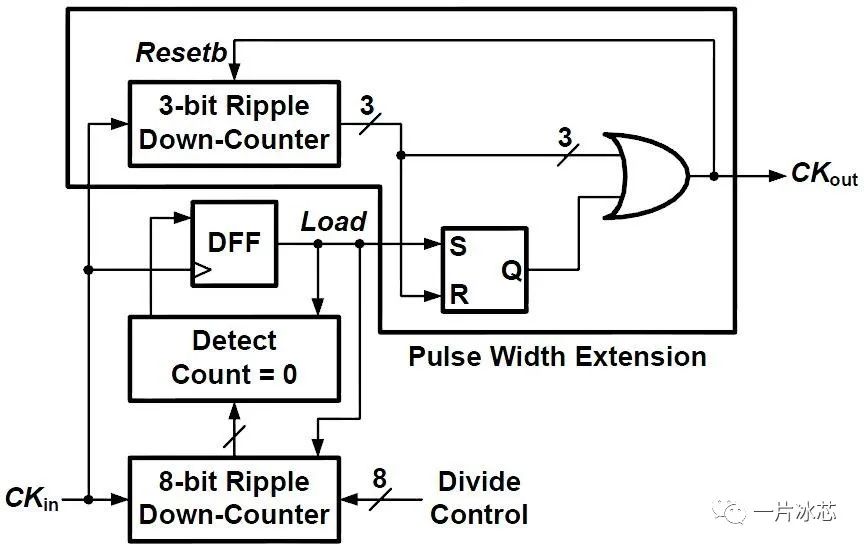

文獻(xiàn)給出的分頻器結(jié)構(gòu)如圖1所示。該分頻器最高輸入頻率(f in )為16.3GHz,也就是一個(gè)周期只有(T in ,T in = 1/ f in )61.3ps。為了避免后級PFD無法分辨如此小的脈寬,線路中增加了脈寬拓展電路,通過3-bit Ripple Down-Counter將最小脈寬拓展了8倍。

8 bit分頻比控制字(N)通過控制8-bit Ripple Down-Counter使分頻器從16-257連續(xù)整數(shù)分頻。總的分頻比為N+2。

Fig1. PLL Divider

圖1中的DFF應(yīng)包含一個(gè)外部復(fù)位信號,用于保證DFF初始輸出(圖1中的Load)為高電平。

初始Load為高電平時(shí),8-bit Ripple Down-Counter將8bit分頻比控制字(圖1中Divide Control, N)上的每bit配置(1或0)Load到8-bit Ripple Down-Counter DFF的輸出端,第一個(gè)CKin上升沿(或下降沿)到來時(shí)Load變?yōu)?,直到8個(gè)DFF輸出全部清零,Load信號再次置高,如此反復(fù),實(shí)現(xiàn)N分頻。

每個(gè)DFF輸出(dq)與輸入(di)相連實(shí)現(xiàn)二分頻,最終實(shí)現(xiàn)N+2分頻,如要實(shí)現(xiàn)257分頻時(shí),配置N=8'b11111111即可。

**2 **電路實(shí)現(xiàn)

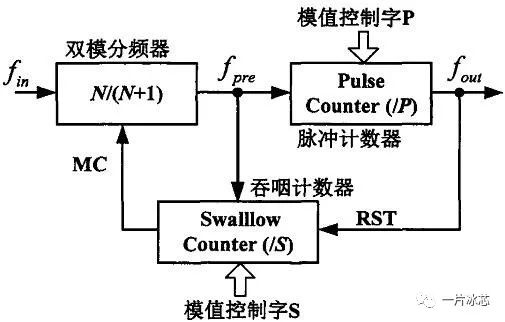

圖1中的Ripple Down-Counter可參考脈沖吞咽計(jì)數(shù)器中的脈沖計(jì)數(shù)器或吞咽計(jì)數(shù)器 ^[3-5]^ ,如圖2所示。只需要8個(gè)DFF級聯(lián)并加上一些邏輯門就可實(shí)現(xiàn),有這方面需求的人,最好親自試一下,這里不再給出具體做法,要提醒的是計(jì)數(shù)器里的DFF最好用差分結(jié)構(gòu)。

Fig2. 基于脈沖呑咽計(jì)數(shù)器結(jié)構(gòu)的可編程分頻器

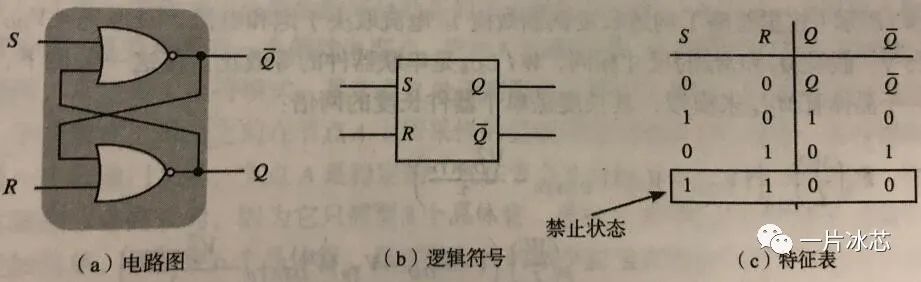

圖1中的SR Latch可由圖3實(shí)現(xiàn)。

Fig3. SR Latch的電路、符號圖及真值表

**3 **仿真結(jié)果

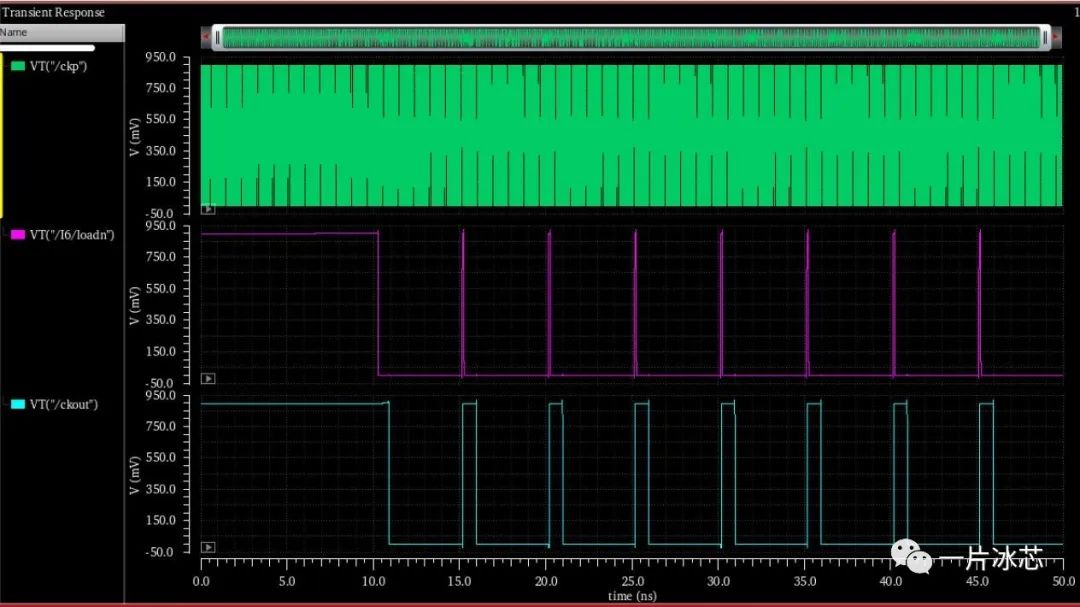

圖4給出了輸入頻率為10GHz,分頻比控制字N=00110000時(shí)的仿真結(jié)果。從上到下依次為輸入時(shí)鐘、拓展脈寬之前的輸出信號及8倍脈寬拓展后的輸出信號。圖中ckp頻率為10GHz,loadn為200MHz,脈寬為100ps,ckout為200MHz,脈寬為800ps。

Fig4. 分頻器仿真結(jié)果

**4 **思考與討論

圖1中的脈寬展寬電路,為什么用時(shí)序電路實(shí)現(xiàn),用組合邏輯也可以實(shí)現(xiàn),兩者有什么區(qū)別?用組合邏輯如何實(shí)現(xiàn)?工業(yè)上實(shí)用嗎?

利用這個(gè)分頻器如何實(shí)現(xiàn)小數(shù)分頻呢?小數(shù)分頻為何要引入Sigma-Delta?噪聲整形的原理是什么?

-

邏輯門

+關(guān)注

關(guān)注

1文章

142瀏覽量

24577 -

仿真器

+關(guān)注

關(guān)注

14文章

1027瀏覽量

84630 -

分頻器

+關(guān)注

關(guān)注

43文章

489瀏覽量

50642 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2283瀏覽量

95803 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6668

發(fā)布評論請先 登錄

相關(guān)推薦

怎么把小數(shù)分頻控制字與整數(shù)分頻控制字結(jié)合起來去控制可編程分頻器?

小數(shù)分頻鎖相環(huán)的工作原理

FPGA實(shí)現(xiàn)小數(shù)分頻器

△∑小數(shù)頻率合成器中的小數(shù)分頻器設(shè)計(jì)

分頻器的作用是什么 半整數(shù)分頻器原理圖分析

如何使用FPGA進(jìn)行任意小數(shù)分頻器的設(shè)計(jì)

偶數(shù)分頻器的設(shè)計(jì)

偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻和小數(shù)分頻詳解

分頻器之小數(shù)分頻設(shè)計(jì)

FPGA學(xué)習(xí)-分頻器設(shè)計(jì)

評論