在高速ADC中增加SFDR的主要限制是什么?

高速ADC是現代電子器件中一個十分重要的組成部分, 通常在工業、汽車、航空以及軍事等領域應用廣泛。隨著技術的發展,高速ADC的性能也不斷得到了提高,但是同時也面臨一些挑戰。其中最有意義的是如何提高高速ADC的SFDR,這可以提高信號的精度和準確性。

SFDR即“串擾自由動態范圍”,代表著ADC在高頻輸入信號下輸出第一個諧波之后的最高諧波信號跟原信號的分離度。在實際應用中,信號動態范圍比串擾自由動態范圍更為常用,但是SFDR更能代表ADC的精度。因此,提高ADC的SFDR非常重要。

提高高速ADC的SFDR需要解決幾個主要問題。首先是信號的抽樣。ADC需要將連續的模擬信號轉化為離散的數字信號。在抽樣時需要注意信號頻率盡量低于采樣率的一半,以避免混淆和失真。如果頻率超過了一半,就會產生混疊的現象,導致原始信號的失真。因此,要提高SFDR,就需要確保信號的抽樣頻率足夠高,以避免混疊。

其次,要確保ADC的時鐘和信號相互協調。ADC需要在準確的時鐘信號下進行抽樣和量化。如果時鐘信號存在抖動或者失真,就可能會導致采樣誤差和失真。因此,在設計高速ADC時,需要考慮時鐘信號的準確性和穩定性,以確保ADC的性能。

第三,ADC需要在合適的溫度和工作電壓下運轉。溫度和電壓變化會對ADC的性能產生重要影響,影響因素包括輸入噪聲和抖動等因素。因此,為了提高ADC的SFDR,需要考慮ADC的工作環境。

最后,要考慮ADC的反饋機制。在ADC的設計過程中,反饋控制是十分重要的。反饋機制可以幫助防止信號過沖或者欠沖,從而提高ADC的穩定性。同時,反饋控制也可以調整ADC的抽樣和量化速率,以滿足不同的應用需求。

總之,在提高高速ADC的SFDR方面,需要注意信號抽樣、時鐘準確性、溫度和工作電壓變化、以及反饋機制等關鍵因素。只有同時兼顧這些方面,才能夠在高速ADC設計中取得優異的性能。

-

adc

+關注

關注

99文章

6601瀏覽量

547511 -

諧波

+關注

關注

7文章

852瀏覽量

42278 -

SFDR

+關注

關注

0文章

40瀏覽量

13080

發布評論請先 登錄

相關推薦

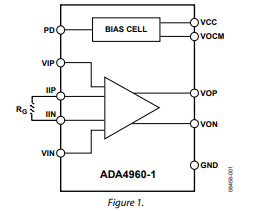

ADA4960-1低功耗、超高速度差分ADC驅動器技術手冊

ADC技術在信號處理中的應用

使用高速ADC工作中遇到兩個很關鍵的問題求解答

ADC12D1600計算SFDR得出的數值只有30dB,主要是2次諧波太大了,如何消除2次諧波?

使用ADC12DJ3200做采樣系統時,發現SFDR受限于交織雜散,有什么方法降低Fs/2-Fin處的雜散?

adc12d1600給一個高電平信號之后,SFDR質量變好了是什么原因?

高速adc與低功耗adc的區別

ADC模塊在MCU中的作用

最大限度地提高GSPS ADC中的SFDR性能:雜散源和Mitigat方法

評論