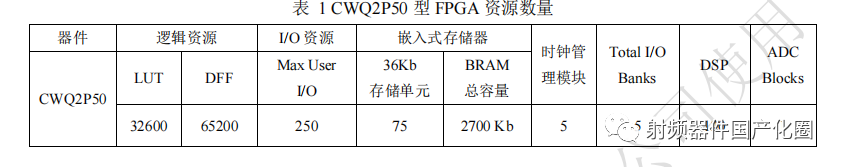

CWQ2P50是基于 SRAM 配置的高密度可編程邏輯陣列電路。其中,6輸入查找表數(shù)量32,600個(gè),嵌入式存儲(chǔ)器容量為2,700Kbit,用戶I/O數(shù)量250個(gè),內(nèi)置5個(gè)時(shí)鐘管理模塊,具有120個(gè)DSP數(shù)字信號(hào)處理模塊,資源數(shù)量列如表 1 所示。

產(chǎn)品特點(diǎn)

CWQ2P50主要用于具備高級(jí)串行連接功能的高性能信號(hào)處理應(yīng)用。

CWQ2P50具有以下特點(diǎn):

基于可配置為分布式存儲(chǔ)器的真實(shí)6輸入查找表(LUT)技術(shù)的高級(jí)高性能FPGA邏輯;

強(qiáng)大的時(shí)鐘管理塊(CMT),結(jié)合了鎖相環(huán)(PLL)和混合模式時(shí)鐘管理器(MMCM)模塊,可實(shí)現(xiàn)高精度和低抖動(dòng);

具有內(nèi)置FIFO邏輯的36Kb雙端口Block RAM,用于片上數(shù)據(jù)緩沖;

具有25x18乘法器, 48位累加器和預(yù)加器的DSP slice,用于高性能濾波,包括優(yōu)化的對(duì)稱系數(shù)濾波;

靈活的配置選項(xiàng),包括: SPI和并行 Flash接口; 專用的回讀重配置邏輯,可支持多比特流;自動(dòng)總線寬度檢測(cè)功能;

對(duì)所有器件都有系統(tǒng)監(jiān)控功能, 包括:片上/片外熱特性監(jiān)控; 片上/片外電源監(jiān)控;通過 JTAG端口訪問所有監(jiān)控量;

采用境內(nèi)28nm工藝設(shè)計(jì)加工,芯核電壓0.9V;

采用高可靠軍級(jí)塑封,采用Flip-Chip鍵合方式;

用戶可配置的模擬接口(XADC),將雙12位1MSPS模數(shù)轉(zhuǎn)換器與片上溫度傳感器和電源傳感器結(jié)合在一起;

多種配置選項(xiàng),包括對(duì)存儲(chǔ)器的支持,具有HMAC/ SHA-256身份驗(yàn)證的256位AES加密以及內(nèi)置的SEU檢測(cè)和校正。

產(chǎn)品用途

CWQ2P50為可編程邏輯器件,內(nèi)部集成了功能強(qiáng)大、并可以靈活配置組合的可編程資源,可實(shí)現(xiàn)輸入輸出接口、通用數(shù)字邏輯、存儲(chǔ)器、數(shù)字信號(hào)處理、時(shí)鐘管理等多種功能,同時(shí)提供了豐富的專用時(shí)鐘與布線資源, 適用于實(shí)現(xiàn)復(fù)雜、高速的數(shù)字邏輯電路,可廣泛應(yīng)用于通訊、信息處理、工業(yè)控制、數(shù)據(jù)中心、儀表測(cè)量、醫(yī)療儀器、人工智能、自動(dòng)駕駛等領(lǐng)域,尤其適用于低功耗、小型化應(yīng)用場(chǎng)景。

對(duì)應(yīng)國(guó)外產(chǎn)品情況

主要性能指標(biāo)、引腳與Xilinx公司FPGA產(chǎn)品XC7S50(FGG484)對(duì)標(biāo)。

-

電路

+關(guān)注

關(guān)注

172文章

5962瀏覽量

172875 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3218瀏覽量

126993 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

517瀏覽量

44162

原文標(biāo)題:CWQ2P50 型現(xiàn)場(chǎng)可編程門陣列電路

文章出處:【微信號(hào):射頻器件國(guó)產(chǎn)化圈,微信公眾號(hào):射頻器件國(guó)產(chǎn)化圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

現(xiàn)場(chǎng)可編程門陣列

現(xiàn)場(chǎng)可編程門陣列有哪些應(yīng)用?

XC7K325T-2FFG900I現(xiàn)場(chǎng)可編程門陣列

XC6SLX16-2FTG256C現(xiàn)場(chǎng)可編程門陣列

XA6SLX25-3CSG324Q現(xiàn)場(chǎng)可編程門陣列

XC3SD1800A-4CSG484LI現(xiàn)場(chǎng)可編程門陣列

XC5VLX85-1FF676C現(xiàn)場(chǎng)可編程門陣列

XC6SLX75T-2CSG484I現(xiàn)場(chǎng)可編程門陣列

XC7A200T-2FFV1156I現(xiàn)場(chǎng)可編程門陣列

FPGA-現(xiàn)場(chǎng)可編程門陣列

現(xiàn)場(chǎng)可編程門陣列的結(jié)構(gòu)與設(shè)計(jì)

現(xiàn)場(chǎng)可編程門陣列的供電原理及應(yīng)用

現(xiàn)場(chǎng)可編程邏輯門陣列器件 FPGA原理及應(yīng)用設(shè)計(jì)

CWQ2P50型現(xiàn)場(chǎng)可編程門陣列電路

CWQ2P50型現(xiàn)場(chǎng)可編程門陣列電路

評(píng)論