I/O電路中電壓比較器

在高速I(mǎi)/O電路設(shè)計(jì)中,輸入I/O的比較器是一個(gè)非常重要的模塊。它的主要功能是將兩個(gè)模擬信號(hào)進(jìn)行比較,輸出一個(gè)二進(jìn)制值。兩個(gè)輸入模擬信號(hào)可以是兩個(gè)互補(bǔ)的電壓信號(hào)也可以是一個(gè)單端信號(hào)與一個(gè)參考電壓。

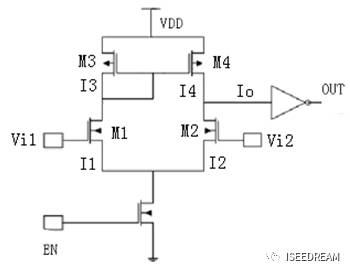

電壓比較器電路如下圖所示

比較器與運(yùn)放的符號(hào)完全一樣,結(jié)構(gòu)上也有許多相似之處。開(kāi)環(huán)工作下的運(yùn)放本身就可以看作一個(gè)比較器。但是比較器與運(yùn)放在設(shè)計(jì)上有許多不同點(diǎn)。運(yùn)放設(shè)計(jì)時(shí),最重要的是考慮輸出與輸入之間的線性傳輸關(guān)系及頻率補(bǔ)償?shù)姆€(wěn)定性,因此響應(yīng)時(shí)間與延遲時(shí)間往往很大,開(kāi)環(huán)增益也不容易做得很大;而比較器是大信號(hào)作用,所以總是處于開(kāi)環(huán)狀態(tài),不存在因?yàn)樨?fù)反饋造成的自激振蕩,因此頻率補(bǔ)償是不必要的。

在電壓比較器的參數(shù)中,響應(yīng)速度是其中非常重要的一個(gè)。一般要求比較器的響應(yīng)速度要很快。也就是說(shuō)在輸入電壓發(fā)生變化后,相應(yīng)輸出電壓的變化應(yīng)該很快出現(xiàn)。輸出電壓還應(yīng)該有很短的上升和下降時(shí)間。另外對(duì)于高性能的電壓比較器來(lái)說(shuō),還應(yīng)有高的開(kāi)環(huán)增益、低的失調(diào)電壓、高的壓擺率等。對(duì)于MOS差分放大器來(lái)說(shuō),失調(diào)過(guò)大是其固有缺點(diǎn),因此減少失調(diào)也是一個(gè)關(guān)鍵問(wèn)題。

對(duì)于高速的I/O輸入電路設(shè)計(jì)中,接收器總是工作在一定的噪聲環(huán)境中,雖然共模噪聲能夠得到很好的抑制,但差模噪聲的存在總是不可避免的。如果比較器足夠的快,并且噪聲的幅度也足夠大,如果輸入恰好位于比較器的閾值點(diǎn)附近,則噪聲就可能會(huì)造成接收器的錯(cuò)誤翻轉(zhuǎn),使輸出出現(xiàn)一些錯(cuò)誤脈沖。因此當(dāng)接口電路設(shè)計(jì)中用到比較器時(shí),接收器通常會(huì)引入閾值遲滯。

閾值遲滯在接收器的設(shè)計(jì)中是一種非常重要的技術(shù)。因?yàn)楫?dāng)接收器的輸入沒(méi)有連接、連接的驅(qū)動(dòng)器的驅(qū)動(dòng)能力下降時(shí),接收器就會(huì)產(chǎn)生不確定的輸入,而閾值遲滯則可以在這種情況下確保接收器的輸出是一個(gè)確定值。如下圖所示,中間的方框水平方向的長(zhǎng)度大小就是遲滯電壓的大小

I/O信號(hào)完整性介紹

信號(hào)完整性(Signal Integrity,簡(jiǎn)稱SI)是指互連線上信號(hào)的質(zhì)量,信號(hào)完整性研究則主要是觀察互連線的電氣特性參數(shù)是如何影響數(shù)字信號(hào)的電壓電流波形的。信號(hào)具有良好的信號(hào)完整性是指當(dāng)需要的時(shí)候,信號(hào)具有所必須達(dá)到的電壓電流數(shù)值。

信號(hào)完整性問(wèn)題一般分成五種:

1、單一網(wǎng)絡(luò)的信號(hào)質(zhì)量,即在信號(hào)路徑或返回路徑上由于阻抗突變而引起的信號(hào)反射和波形失真;

2、相鄰網(wǎng)絡(luò)間的串?dāng)_,主要是由與理想回路或非理想回路耦合的電容、電感引起的干擾信號(hào);

3、電平波動(dòng)(rail collapse),即由輸入輸出接口電路中封裝寄生電感所引起的電壓波動(dòng),典型的有過(guò)沖和地彈;

4、來(lái)自系統(tǒng)的電磁干擾,這是因?yàn)楦哳l信號(hào)傳輸會(huì)產(chǎn)生大量的EMI(Electromagnetic Interference)噪聲,最終會(huì)導(dǎo)致ISI(inter-symbol interference);

5、高頻信號(hào)在有損傳輸線上傳輸引起的損耗和衰減(lossy and attenuation)。

信號(hào)反射

信號(hào)的振鈴(ringing)和環(huán)繞振蕩(rounding)是由線上的寄生電感和電容引起的信號(hào)反射。振鈴屬于欠阻尼狀態(tài),而環(huán)繞振蕩屬于過(guò)阻尼狀態(tài)。該種類型的信號(hào)完整性問(wèn)題通常發(fā)生在周期信號(hào)中,如時(shí)鐘等。振鈴和環(huán)繞振蕩是由多種因素引起的,振鈴可以通過(guò)適當(dāng)?shù)亩私佑枰詼p小,但是不可能完全消除。

源端與負(fù)載端阻抗不匹配會(huì)引起線上反射,負(fù)載將一部分電壓反射回源端。如果負(fù)載阻抗小于源阻抗,反射電壓為負(fù);反之,如果負(fù)載阻抗大于源阻抗,反射電壓為正。布線的幾何形狀、不正確的線端接、經(jīng)過(guò)連接器的傳輸及電源平面的不連續(xù)等因素的變化均會(huì)導(dǎo)致此類反射。

在高速信號(hào)傳輸中由于信號(hào)的頻率很高,信號(hào)的上升時(shí)間或下降時(shí)間很短。當(dāng)信號(hào)線的長(zhǎng)度足夠的長(zhǎng),以至于信號(hào)的傳播延時(shí)大于信號(hào)波形的上升時(shí)間或下降時(shí)間時(shí),傳輸線效應(yīng)就起作用了。此時(shí)如果傳輸線特征阻抗與發(fā)送器輸出阻抗或者接收器輸入阻抗不匹配,就會(huì)在傳輸線上產(chǎn)生信號(hào)的反射。反射會(huì)導(dǎo)致過(guò)沖,從而降低系統(tǒng)的噪聲容限和引起較大的延時(shí)。

解決高頻信號(hào)反射問(wèn)題主要方法是在設(shè)計(jì)時(shí),盡量使傳輸線特征阻抗與發(fā)送器輸出阻抗或者接收器輸入阻抗匹配,一般加入終端匹配電阻,該電阻要根據(jù)信號(hào)傳輸介質(zhì)和傳輸長(zhǎng)度的不同而做出相應(yīng)的變化。

串?dāng)_

串?dāng)_主要是由線間的耦合電容和耦合電感引起的信號(hào)相互干擾的現(xiàn)象。串?dāng)_噪聲就是由相鄰跳變的攻擊者線通過(guò)耦合電容或耦合電感對(duì)受害者線的干擾信號(hào)。由于耦合電容是導(dǎo)致線間信號(hào)串?dāng)_的主要因素,而且線間耦合電感很小,所以這里對(duì)電感就不作主要分析了。串?dāng)_噪聲在不同外部條件下主要有兩種不同的表現(xiàn):邏輯毛刺和時(shí)序延遲。

當(dāng)受害者線處于靜態(tài),或者其跳變窗口與攻擊者線跳變窗口分離時(shí),若噪聲信號(hào)足夠大,超過(guò)門(mén)限電壓,將導(dǎo)致受害者線的邏輯狀態(tài)改變,經(jīng)傳播并被觸發(fā)器鎖存后,產(chǎn)生功能錯(cuò)誤。如下圖所示

當(dāng)攻擊者線和受害者線的開(kāi)關(guān)窗口重疊時(shí),串?dāng)_效應(yīng)將導(dǎo)致受害者線的延遲變化,如下圖所示。

串?dāng)_延遲最大的問(wèn)題在于該延遲具有不確定性,與攻擊者線和受害者線的相對(duì)跳變方向相關(guān)。若兩者跳變方向相反,則串?dāng)_延遲增大,將可能導(dǎo)致建立時(shí)間問(wèn)題;反之,則串?dāng)_延遲減小,將可能導(dǎo)致保持時(shí)間問(wèn)題。

顯然,攻擊者跳變?cè)娇旎蛘唏詈想娙菰酱螅當(dāng)_噪聲就越大。驅(qū)動(dòng)器越強(qiáng)(有更低的驅(qū)動(dòng)阻抗)或者接地電容越多,串?dāng)_噪聲就越小。對(duì)于長(zhǎng)線,互連電阻也起作用,互連電阻越大,串?dāng)_噪聲就越大。對(duì)于串?dāng)_延遲的不確定性,耦合電容與總的互連電容之比是一個(gè)非常重要的因素。

電平波動(dòng)

接口電路中的電平波動(dòng)主要是由于寄生電感的作用,某些線上的電流突變導(dǎo)致電源-地網(wǎng)絡(luò)的電壓波動(dòng)。由于電感作用,線上電流突變將導(dǎo)致該線與其相鄰線上的電壓突變。如果這些線是片上電源-地網(wǎng)絡(luò)的一部分,所引起的電壓波動(dòng)就會(huì)影響到電源和地網(wǎng)絡(luò)。由于電感效應(yīng)只對(duì)高頻長(zhǎng)線重要,自感的提取和分析主要集中于時(shí)鐘線,互感效應(yīng)集中于高頻總線信號(hào)。

對(duì)于有電感問(wèn)題的電路,一種途徑是在信號(hào)層之間增加電源層。由于制造成本和功耗高,此法不再使用。對(duì)于時(shí)鐘網(wǎng)絡(luò),信號(hào)電流回路應(yīng)該使用同層并行的屏蔽電源線,減小時(shí)鐘的自感,并使對(duì)其他連線的感性噪聲最小。對(duì)于總線,每4到8個(gè)并行的長(zhǎng)總線信號(hào)之間插入電源線。對(duì)于長(zhǎng)線,增加反相器減小互感效應(yīng)。Repeater插入仍然是減小電感噪聲的最有效的方法之一。

在高頻下,接口電路除了考慮片上寄生電感對(duì)高速信號(hào)完整性的影響外,芯片封裝的電感更是不能忽略,尤其是對(duì)于wire-bond或者periphery-bumped封裝類型的芯片。此時(shí)輸入輸出PAD和電源或地PAD都會(huì)表現(xiàn)出比較大的自感,其值在2nH到20nH之間,主要取決于線的長(zhǎng)度和封裝類型。在高速開(kāi)關(guān)的情況下,流過(guò)電源和地的瞬態(tài)電流很大,由于自感的存在,引起電源電壓的波動(dòng)或者地電壓的反彈---地彈(Ground-bounce)。如果要提高傳輸速率,減少地彈的影響,必須從如下幾個(gè)方面入手:

減少輸出擺幅;

不要驅(qū)動(dòng)過(guò)大的片外負(fù)載;

減少同時(shí)跳變的驅(qū)動(dòng)器數(shù)目;

盡可能減少寄生電感。

EMI噪聲

EMI(Electromagnetic Interference)輻射主要是由電場(chǎng)中電荷的運(yùn)動(dòng)或者電場(chǎng)本身變化引起的。通常,任何比較陡直的電平變化,如時(shí)鐘、數(shù)據(jù)、地址或者控制信號(hào),都會(huì)在電子系統(tǒng)中產(chǎn)生電磁輻射。在數(shù)字系統(tǒng)中,周期性的時(shí)鐘信號(hào)是產(chǎn)生EMI的主要源頭。然而,控制信號(hào)和時(shí)序信號(hào)、地址和數(shù)據(jù)總線、互連電纜和連接器同樣也會(huì)產(chǎn)生大量的EMI噪聲。在高速串行信號(hào)傳輸系統(tǒng)中,隨著數(shù)據(jù)傳輸速度的提高,尤其是采用源同步傳輸方式后,數(shù)據(jù)傳輸線上的電平變化很快,這時(shí)就要重視傳輸線產(chǎn)生的EMI了。要減少高速串行信號(hào)傳輸系統(tǒng)中的EMI,通常可以采用差分信號(hào)傳輸方式。

平衡差分線路有兩個(gè)大小相等,但方向相反的電流,稱為奇模態(tài)信號(hào)(odd-mode signal)。當(dāng)這些奇模態(tài)信號(hào)產(chǎn)生的場(chǎng)相互耦合,彼此纏繞,它們就不能輻射出去產(chǎn)生危害,因此有一個(gè)平衡緊密耦合的差分傳輸通路有助于減少電磁干擾的輻射。差分信號(hào)同樣有抗外部源干擾的能力。這些外部源比如說(shuō)電動(dòng)機(jī)的感應(yīng)輻射,鄰近傳輸線的串?dāng)_等。

介質(zhì)損耗與衰減

當(dāng)信號(hào)在長(zhǎng)距離有損傳輸線上傳輸時(shí),由于非電介質(zhì)、輻射等原因通常信號(hào)的高頻分量會(huì)衰減得很厲害,有的信號(hào)在接收端只剩下基波分量,高頻分量完全衰減掉了。為了減少高頻分量的衰減,通常要在PCB的設(shè)計(jì)上下功夫。但在電路設(shè)計(jì)上,也出現(xiàn)了一些技術(shù),它們并不能減少信號(hào)傳播過(guò)程中的高頻分量的衰減,但是它們可以保證信號(hào)在經(jīng)過(guò)同樣的衰減后,信號(hào)仍具有較大比例的高頻分量。這些技術(shù)最初應(yīng)用在通信領(lǐng)域,如預(yù)加重技術(shù)(pre-emphasis)、均衡技術(shù)(equalization)。當(dāng)然,它們應(yīng)在高速信號(hào)傳輸領(lǐng)域也是非常有用的。

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

8438瀏覽量

148106 -

差分放大器

+關(guān)注

關(guān)注

8文章

496瀏覽量

52591 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1423瀏覽量

96048 -

電磁干擾

+關(guān)注

關(guān)注

36文章

2357瀏覽量

106011 -

電壓比較器

+關(guān)注

關(guān)注

18文章

220瀏覽量

37836

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

PCB電路中的電源完整性設(shè)計(jì)

何為信號(hào)完整性?信號(hào)完整性包含哪些

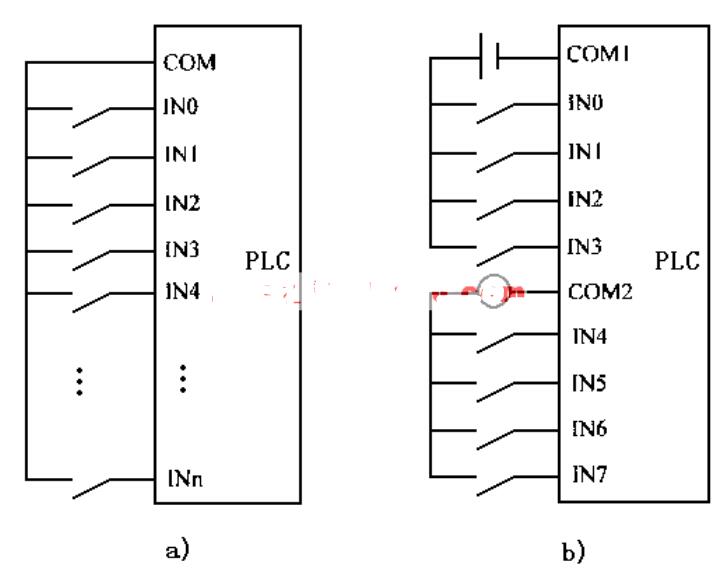

數(shù)字I/O介紹

冗余I/O

基于Rocket I/O模塊的高速I/O設(shè)計(jì)

基于SmartRail的I/O的介紹

高速串行總線的信號(hào)完整性驗(yàn)證

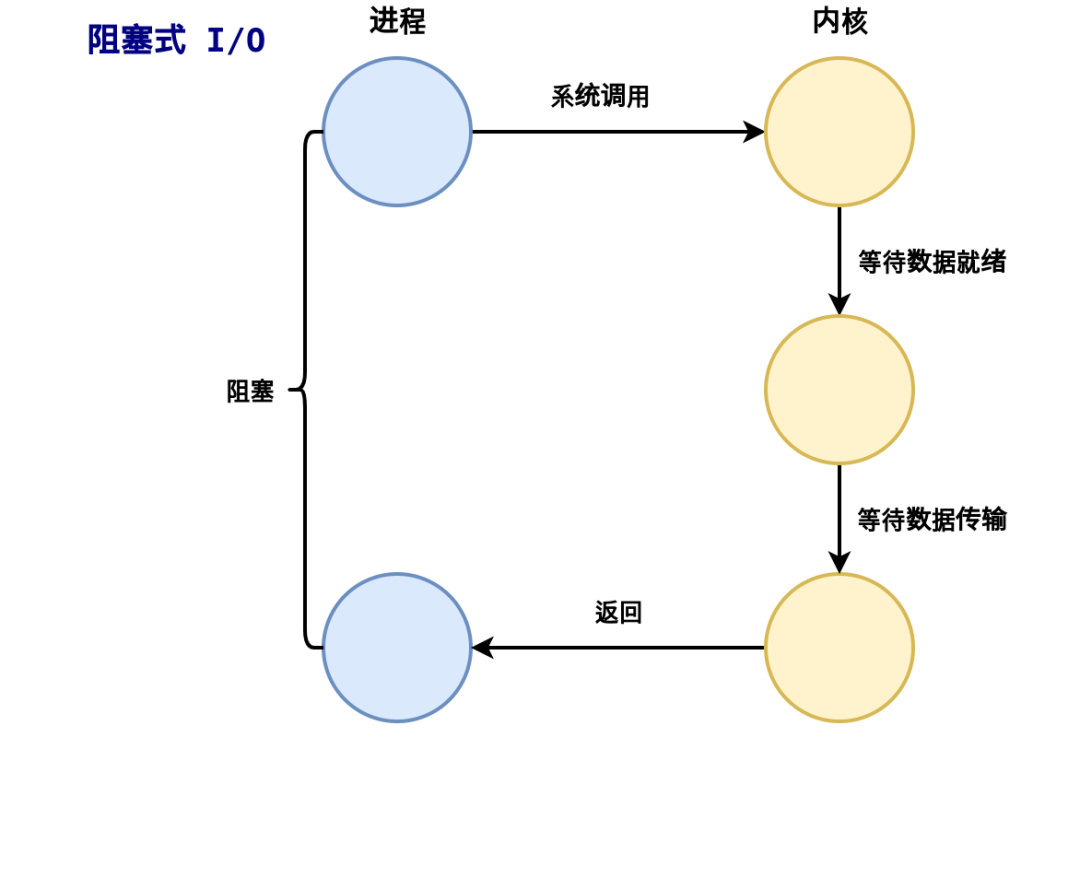

如何更改 Linux 的 I/O 調(diào)度器

PLC的I/O模塊如何選擇

Linux中如何使用信號(hào)驅(qū)動(dòng)式I/O?

評(píng)論