01

輸入輸出范圍

軌到軌運放,想必大家都不陌生。

Power rail

什么是供電電源軌?

運放供電電壓,決定運放處理信號的范圍。

軌到軌指的是,運放輸入輸出范圍,可以擺到電源軌。

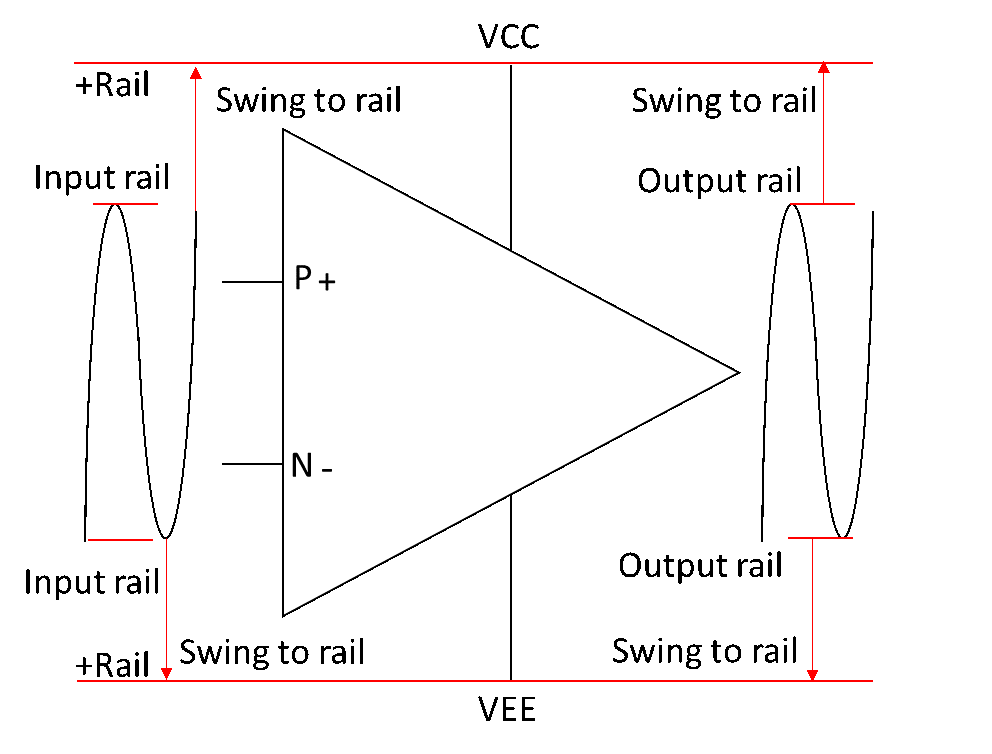

如下圖所示:

為什么會有非軌到軌特性?

輸入:差分基本放大電路,MOS/BJT在輸入電壓(共模)較大時,進入非線性區,導致非軌到軌現象產生。

輸出:甲乙類功率放大電路,BJT的飽和電壓、二極管的Forward壓降,導致此現象產生。

非軌到軌特性對電源設計的影響?

在下最早接觸電力電子設計時,碰到過這種情況。選用某非軌到軌運放,輸入正弦波,輸出突然被削頂。

而后突然驚覺。竟選用非軌到軌運放。難怪如此。說起來抽象,直接上圖:

結論1:

結論:在現今CMOS電平橫行年代,軌到軌特性尤為重要!

02

頻率特性(速度)

1

帶寬增益積

GBW: Gain bandwidth product

什么是GBW?

運放開環帶寬為1時的頻率,亦稱為單位增益帶寬。

啰嗦一句,這里工程師,經常把GBW誤稱為帶寬。真實的兩個概念,運放一般給出帶寬增益積的指標。

GBW對電源采樣電路有哪些影響?

仍以差分放大電路為例。不考慮誤差時,增益為R2/R1,某次應用中,你突然發現,放大100kHz信號,為何增益小于R2/R1?

這時你要問自己,設計電路時,考慮GBW了嗎?

以某運放為例:

GBW=1MHz,AOL=100kHz=20dB(10倍)。

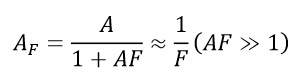

以閉環系統思路分析:

你的期望是: 100kHz信號能完整放大10倍(理論上R2/R1=10)

實際情況是: 增益G=5,因為開環增益不夠的緣故。

結論2

GBW越大,一般某頻率處,開環增益越大,理論增益和實際增益差距越小。

2

壓擺率

SR: Slew rate

什么是SR?

運放輸出電壓的轉換速率。

通常單位為V/us

SR怎樣考量?

如果,某信號需要快速保護,擺率會影響這個信號的延遲。

結論3

快速運放擺率大,適合做快速保護。

03

精度

1

輸入失調電壓Vos

Offset voltage

什么是輸入失調電壓Vos?

簡單解釋:為了使輸出電壓為零,在輸入端施加的差分電壓。

為什么會有輸入失調電壓Vos?

運放輸入級,BJT/CMOS組成的差分放大電路,理論上完全對稱。

然而,受工藝所限,不匹配的輸入級,導致了輸入失調電壓。

Vos對電源的影響?

以差分放大電路為例:

理論增益為:

考慮失調電壓后增益為:

多大影響,一算便知~

結論4

輸入失調電壓會影響精密度,對于精確度較高的應用,選取失調電壓小的運放。

2

輸入偏置電流

Bias current

什么是輸入偏置電流Ibias?

運放輸入端P/N輸入電流之和。

為什么存在輸入偏置電流Ibias?

運放輸入是差分放大電路,那想讓它工作,得給人靜態工作點吧。

輸入偏置電流,便由輸入級直流工作點引入。

Ibias對電源采樣調理電路的影響?

仍以差分放大電路分析:

考慮偏置電流,放大倍數為:

因此,理論上,只要電阻參數完全相等,輸入偏置電流對差分放大電路,沒有任何影響。

但其他運放典型應用呢?以反相比例放大電路(R*=0)為例:

考慮偏置電流,放大倍數為:

結論5

輸入偏置電流可以通過差分、添加補償電阻去除。

04

抗擾度

1

共模抑制比

CMRR: Common mode rejection ratio

什么是共模抑制比CMRR?

差分信號放大倍數/共模信號放大倍數

也許一般人不重視這個參數,但是,當你的調理電路,被開關噪聲,干擾的一塌糊涂,你就懂這個痛了。

結論6

越大的CMRR,對抑制開關噪聲(共模干擾),越有效果。

2

電源抑制比

PSRR: Power supply rejection ration

什么是電源抑制比PSRR?

電源信號/對應的輸出電壓。

也許還有人,也不重視這個參數,但是當你發現,輸出疊加輔助電源的開關次信號,你就懂了。

在下當年調電路時,發現運放輸出,總是疊加一個很小的紋波,和輔電開關頻率一致,我陷入了沉思…

結論7

PSRR越大,輔電對運放輸出影響越小。

-

二極管

+關注

關注

147文章

9669瀏覽量

166926 -

放大電路

+關注

關注

104文章

1789瀏覽量

106812 -

CMOS電平

+關注

關注

0文章

18瀏覽量

7219 -

失調電壓

+關注

關注

0文章

123瀏覽量

13892 -

軌到軌

+關注

關注

0文章

14瀏覽量

6620

發布評論請先 登錄

相關推薦

從零學運放—04 單電源運放的設計

運放設計的十個大坑

11個運放常見指標資料下載

運放-單電源運放和雙電源運放

教你從4個維度7個指標選取適合你的電源運放

教你從4個維度7個指標選取適合你的電源運放

評論