【模擬電路設計】輸入失調(diào)電壓(Input Offset Voltage,VOS)

運算放大器的Data sheet一般分為兩大類:直流參數(shù)和交流參數(shù)。DC參數(shù)決定了輸出與理想運算放大器匹配的精確程度。因此,運算放大器的精度取決于直流誤差的大小。

我們在使用運放時,經(jīng)常會看到一個參數(shù),輸入失調(diào)電壓,輸入失調(diào)電壓 (VOS) 是運算放大器 (op amp) 規(guī)格中的常見直流參數(shù)。但是這個值是干嘛的?今天我們主要分為如下兩方面進行講解一下。

①失調(diào)電壓的理解

②失調(diào)電壓的產(chǎn)生

失調(diào)電壓的理解

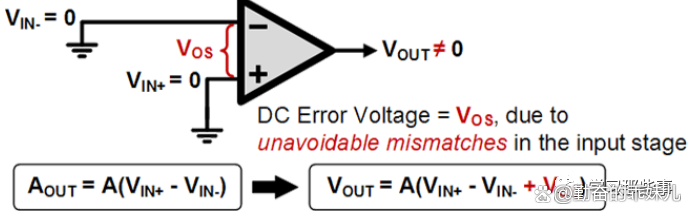

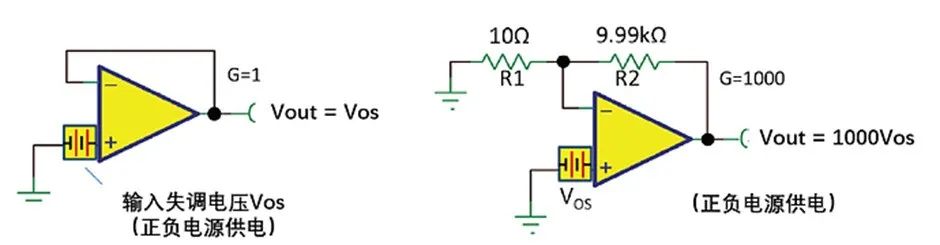

理想情況下,如果運算放大器的兩個輸入電壓完全相同,則輸出應為0V。但運放內(nèi)部兩輸入支路無法做到完全平衡,導致輸出永遠不會是0,具體見圖1所示。此時保持放大器負輸入端不變,而在正輸入端施加一個可調(diào)的直流電壓,調(diào)節(jié)它直到輸出直流電壓變?yōu)?V,此時正輸入端施加的電壓的負值即為輸入失調(diào)電壓,用VOS表示。但是,多數(shù)情況下,輸入失調(diào)電壓不分正負, 生產(chǎn)廠家會以絕對值表示。輸入失調(diào)電壓乘以增益,表現(xiàn)為輸出電壓與理想值的偏差。當運用在傳感器時,運算放大器的輸入失調(diào)電壓會導致傳感器檢測靈敏度出現(xiàn)誤差。為了將檢測誤差保持在指定的容限水平以下,有必要選擇具有低輸入失調(diào)電壓的運算放大器。

因此,可以知道對于一些要求高的產(chǎn)品會選擇輸入失調(diào)電壓較小的運放,失調(diào)電壓為1uV以下,屬于極優(yōu)秀的。100uV以下的屬于較好的。

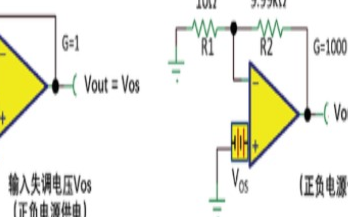

例如:當一個放大器被設計成A倍閉環(huán)電壓增益時,如果放大器的失調(diào)電壓為VOS,則放大電路0輸入時,輸出存在一個等于A*VOS的直流電平,此輸出被稱為輸出失調(diào)電壓。閉環(huán)增益越大,則輸出失調(diào)電壓也越大。對我們想要的輸出偏差就越大。

圖1 對VOS的圖解

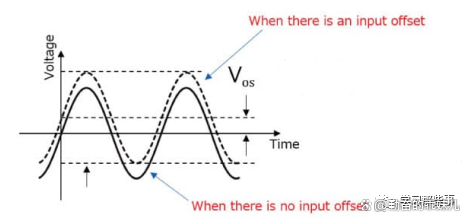

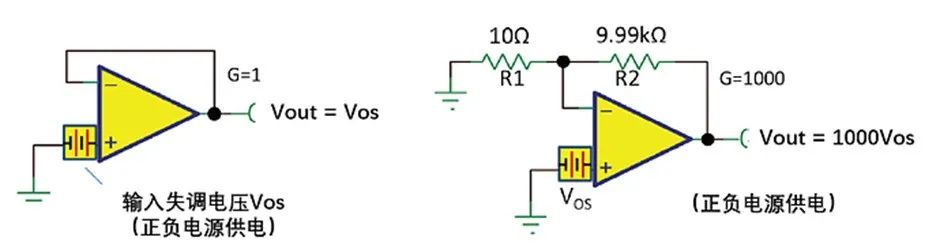

理論來說Vout=A(VIN+-VIN-),但實際是Vout=A(VIN+-VIN-+VOS),意味著Vout會受VOS干擾。我們來看圖2加深印象,可以看見實線是我們想要的輸出波形,虛線為實際的輸出波形,當V0S越小時,虛線越接近實線。

圖 2 輸出波形

02失調(diào)電壓產(chǎn)生原因

①芯片制造工藝導致

輸入失調(diào)電壓的產(chǎn)生,主要是因為輸入級對稱晶體管的不匹配所導致,而這種情況在工藝上很難避免,就好比同樣加工的產(chǎn)品尺寸總會有一定的誤差,不可能完全一樣,只是看你衡量的尺度,比如只精確小數(shù)點后兩位時值可能一樣,但是精確到小數(shù)點后十位、后百位時,就會出現(xiàn)差異了,這是工藝上無法避免的,所以導致任何運放都會有失調(diào)電壓。

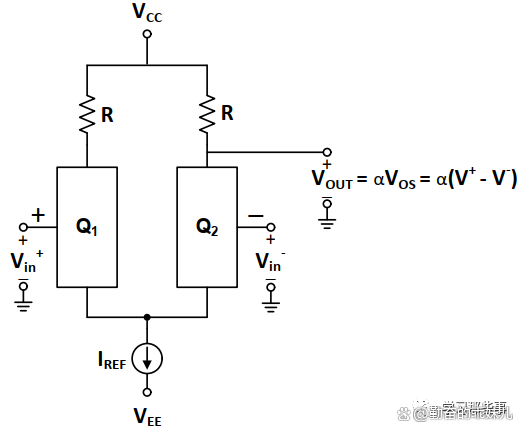

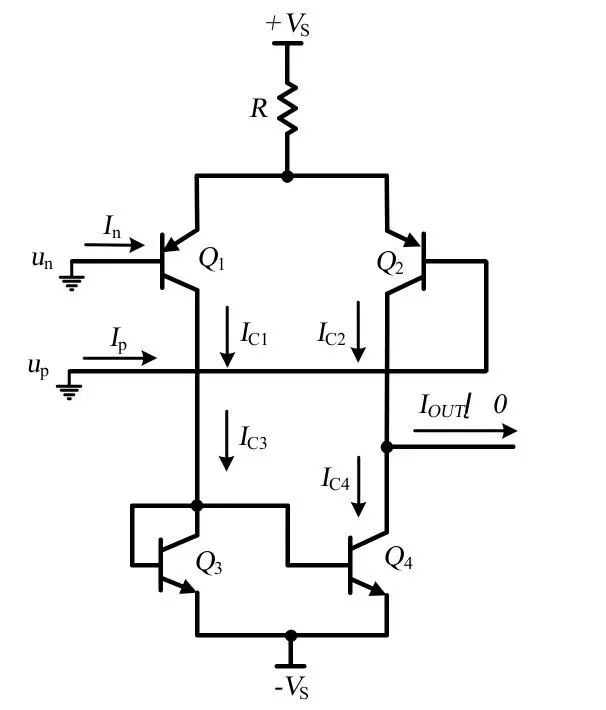

大多數(shù)運放的輸入級由差分放大器組成。如圖3所示,其中Q1(+或同相輸入端)和Q2(-或反相輸入端)可以是BJT、FET或MOS晶體管。運算放大器的輸入端是這些晶體管的基極(BJT)或柵極(FET、MOS)。理想情況下,電路的每個支路都是平衡的,這樣一半的電流流過每個晶體管(IQ1=IQ2=IREF/2),并且反相和同相輸入處于相同的電位。而實際中R、Q1和Q2中的不匹配會使該電流失衡,造成晶體管的基極(柵極)電壓變得不相等,從而產(chǎn)生小的差分電壓VOS。

圖3 放大器輸入級電路

②芯片封裝工藝導致

大多數(shù)芯片封裝過程不會影響失調(diào)電壓。但是少數(shù)情況下封裝過程會影響運放的失調(diào)電壓,比如封裝過程中芯片受到微小的應力影響。

③對策

常用的處理方法是在運放生產(chǎn)后進行測試與校準,或者在輸出級使用斬波等技術(shù)改善運放的失調(diào)電壓。

產(chǎn)品使用上直接選擇VOS遠小于被測直流量的放大器,或者通過運放的調(diào)零措施消除這個影響。如果我們只關心被測信號中的交變成分,直接可以在輸入端和輸出端增加交流耦合電路,將其消除。

調(diào)零方法:有些運放有兩個調(diào)零端,一般數(shù)據(jù)手冊會有講如何進行調(diào)零,我們只需要根據(jù)要求接電位器調(diào)零即可。對沒有調(diào)零端的運放,可采用外部的輸出調(diào)零或者輸入調(diào)零。

03總結(jié)

當然上面的內(nèi)容其實我們只需要了解即可,重點知道輸入失調(diào)電壓越小越好,但是實際使用中有時候并不需要太小的,根據(jù)實際情況進行選擇即可,因為越小意味著價格越貴。

產(chǎn)生VOS的原因主要是由于硅芯片制造過程中輸入晶體管和元件不匹配,以及封裝過程中施加在芯片上的應力影響。這些影響共同導致流經(jīng)輸入電路的偏置電流失配,導致運算放大器輸入端出現(xiàn)電壓差。通過增加匹配、改進封裝材料和工藝,可降低VOS。

-

運算放大器

+關注

關注

215文章

4952瀏覽量

173137 -

運放

+關注

關注

47文章

1166瀏覽量

53139 -

芯片封裝

+關注

關注

11文章

505瀏覽量

30648 -

失調(diào)電壓

+關注

關注

0文章

123瀏覽量

13887

發(fā)布評論請先 登錄

相關推薦

運算放大器電路出現(xiàn)誤差?你需要了解失調(diào)電壓與開環(huán)增益的關系

運算放大器:詳解電路中的失調(diào)電壓與開環(huán)增益

為何說運算放大器的輸入失調(diào)電壓很重要?

輸入失調(diào)電壓對運算放大器性能的影響是什么?

AD708_超低失調(diào)電壓雙運算放大器

具精準 50μV 失調(diào)電壓的運算放大器工作在 76V 輸入電壓范圍

模擬運算放大器的失調(diào)電壓變化

運算放大器輸入失調(diào)電壓的理解和產(chǎn)生原因

運算放大器輸入失調(diào)電壓的理解和產(chǎn)生原因

評論